X+r(t)

Фиг I

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в информационно-изме- рительных системах и системах автоматического управления, работающих в условиях аддитивных случайных помех.

Целью изобретения является повышение быстродействия.

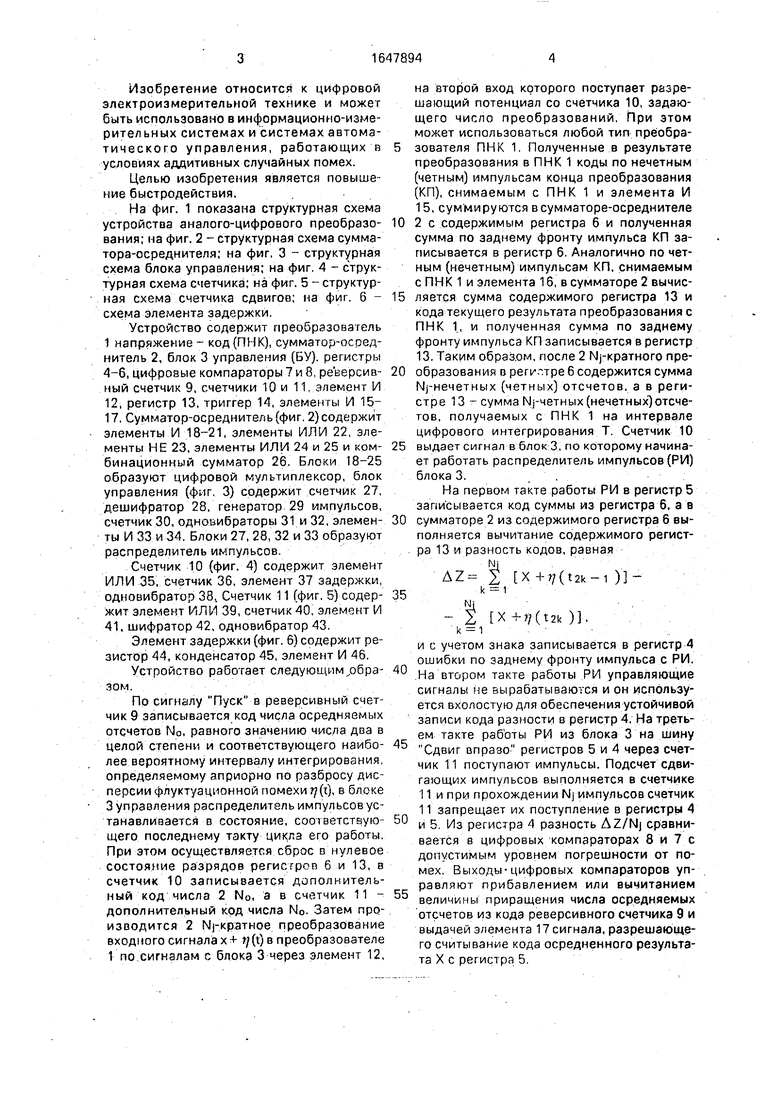

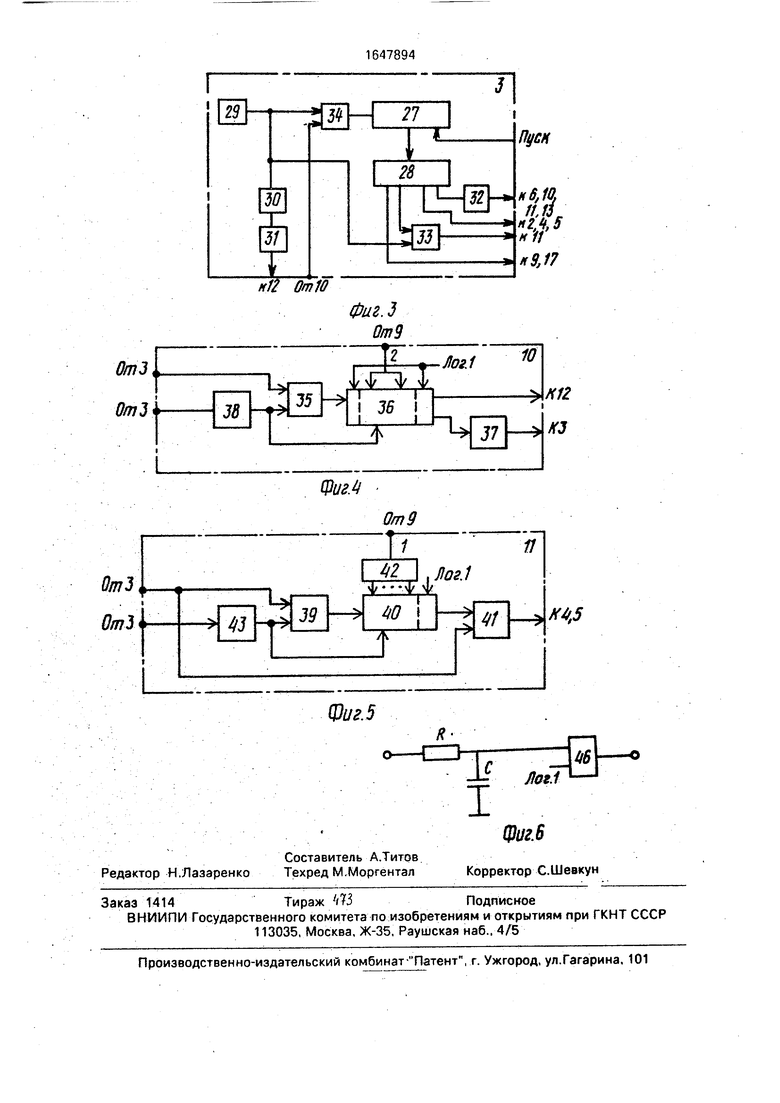

На фиг. 1 показана структурная схема устройства аналого-цифрового преобразования; на фиг. 2 - структурная схема сумма- тора-осреднителя; на фиг. 3 - структурная схема блока управления; на фиг, 4 - структурная схема счетчика; на фиг. 5 - структурная схема счетчика сдвигов; на фиг. 6 - схема элемента задержки.

Устройство содержит преобразователь 1 напряжение - код (ПИК), сумматор-осоед- нитель 2, блок 3 управления (БУ). регистры 4-6, цифроаые компараторы 7 и 8, реверсивный счетчик 9, счетчики 10 и 11, элемент И 12, регистр 13, триггер 14, элементы И 15- 17, Сумматор-осреднитель(фиг. 2) содержит элементы И 18-21, элементы ИЛИ 22, элементы НЕ 23, элементы ИЛИ 24 и 25 и комбинационный сумматор 26. Блоки 18-25 образуют цифровой мультиплексор, блок управления (фиг. 3) содержит счетчик 27, дешифратор 28, генератор 29 импульсов, счетчик 30, одноьибраторы 31 и 32, элементы И 33 и 34. Блоки 27, 28, 32 и 33 образуют распределитель импульсов.

Счетчик 10 (фиг. 4) содержит элемент ИЛИ 35, счетчик 36, элемент 37 задержки, одновибратор 38t Счетчик 11 (фиг. 5) содержит элемент ИЛИ 39, счетчик 40, элемент И 41, шифратор 42, одновибратор 43.

Элемент задержки (фиг. 6) содержит резистор 44, конденсатор 45, элемент И 46.

Устройство работает следующим,образом.

По сигналу Пуск в реверсивный счетчик 9 записывается код числа осредняемых отсчетов No, равного значению числа два в целой степени и соответствующего наиболее вероятному интервалу интегрирования, определяемому априорно по разбросу дисперсии флуктуационной помехи 17(1), в блоке 3 управления распределитель импульсов устанавливается в состояние, соо ветствую щего последнему такту цикла его работы. При этом осуществляется сброс в нулевое состояние разрядов регистров 6 и 13, в счетчик 10 записывается дополнительный код числа 2 N0, а в счетчик 11 - дополнительный код числа N0. Затем производится 2 Nj-кратное преобразование входного сигнала х + J/(t) в преобразователе 1 по сигналам с блока 3 через элемент 12,

на второй вход которого поступает разрешающий потенциал со счетчика 10, задающего число преобразований, При этом может использоваться любой тип преобразователя ПНК 1. Полученные в результате преобразования в ПНК 1 коды по нечетным (четным) импульсам конца преобразования (КП), снимаемым с ПНК 1 и элемента И 15, суммируются всумматоре-осреднителе

2 с содержимым регистра 6 и полученная сумма по заднему фронту импульса КП записывается в регистр 6. Аналогично по четным (нечетным) импульсам КП, снимаемым с ПНК 1 и элемента 16, в сумматоре 2 вычисляется сумма содержимого регистра 13 и кода текущего результата преобразования с ПНК 1, и полученная сумма по заднему фронту импульса КП записывается в регистр 13. Таким образом, после 2 Nj-кратного преобразования в регигтре 6 содержится сумма Nj-нечетных (четных) отсчетов, а в регистре 13 - сумма Nj-четных (нечетных)отсчетов, получаемых с ПНК 1 на интервале цифрового интегрирования Т. Счетчик 10

выдает сигнал в блок 3, по которому начинает работать распределитель импульсов (РИ) блока 3.

На первом такте работы РИ в регистр 5 записывается код суммы из регистра б, а в

сумматоре 2 из содержимого регистра 6 выполняется вычитание содержимого регистра 13 и разность кодов, равная

AZ- X+J/(t2k-i )k - 1

5 X+v(t2k ).

k 1

0

5

5

и с учетом знака записывается в регистр 4 ошибки по заднему фронту импульса с РИ. На втором такте работы РИ управляющие сигналы не вырабатываются и он используется вхолостую для обеспечения устойчивой записи кода разности в регистр 4. На третьем такте работы РИ из блока 3 на шину Сдвиг вправо решстров 5 и 4 через счетчик 11 поступают импульсы. Подсчет сдвигающих импульсов выполняется в счетчике 11 и при прохождении NJ импульсов счетчик 11 запрещает их поступление в регистры 4 0 и 5 Из регистра 4 разность AZ/Nj сравнивается в цифровых компараторах 8 и 7 с допустимым уровнем погрешности от помех. Выходы-цифровых компараторов управляют прибавлением или вычитанием величины приращения числа осредняемых отсчетов из кода реверсивного счетчика 9 и выдачей элемента 17 сигнала, разрешающего считывание кода осредненного результата X с регистра 5

Таким образом, изменение интервала интегрирования, определяемого кодом счетчика 9 на i-м шаге поиска осуществляется на четвертом такте работы РИ блока 3 управления в соответствии с итерационной формулой

NH-I-NI + #NI,

где Ni-i N0+ в No,

+ 1 I AZ/Nj I -Ai 0; I AZ/Nj I -A2 0;

Д2 I AZ/NI I Ai.

J 2 0

Если Да I AZ/Nj I Ai, то на четвертом такте работы распределителя импульсов с выхода элемента 17 снимается сигнал, разрешающий считывание кода с регистра 5. На пятом такте работы распределителя импульсов происходит запись дополнительного кода удвоенного числа осредняемых отсчетов из источника 9 в счетчик 10 и дополнительного кода числа осредняемых отсчетов в счетчик 11, обнуление регистров 6 и 13. Счетчик 10 выдает сигнал в блок 3 и запрещает работу распределителя импульсов. Устройство оказывается подготовленным для следующего цикла работы.

После нескольких шагов поиска (нескольких описанных циклов) в реверсивном счетчике 9 устанавливается некоторое значение N, соответствующее значению допустимой погрешности AI с заданной доверительной вероятностью/, причем низкочастотные помехи не оказывают влияние на время поиска необходимого NJ (быстродействие устройства).

Если коды значений низкочастотной помехи отличаются друг от друга при временном интервале, не большем Т, то быстродействие по сравнению с известным устройством будет выше не менее, чем на 2Т, где Т - длина интервала цифрового интегрирования.

Счетчик 10 служит для подсчета числа импульсов, поступающих на запуск ПНК 1. По сигналу из блока 3 одновибратор 38 формирует импульс, по переднему фронту которого осуществляется запись логической 1 в младший и старший разряды счетчика 36, а в остальные разряды - запись обратного кода числа осредняемых отсчетов NJ, снимаемого с реверсивного счетчика 9. Выход элемента И 35 соединен со счетным входом счетчика 36, и по заднему фронту импульса с одновибратора 38 содержимое счетчика 36 увеличивается на единицу. Таким образом, в старшем разряде счетчика 36 записана 1, а в остальных - дополнительный код удвоенного числа осредняемых отсчетов 2 NJ. Импульсы запуска ПНК 1 через элемент

35 поступают на счетный вход счетчика 36, а при прохождении 1 2Nj импульсов старший разряд счетчика обнуляется, С единичного выхода старшего разряда счетчика снимается сигнал, запрещающий поступление импульсов на запуск ПНК 1 через элемент 12, который служит вентилем, С нулевого выхода счетчика с задержкой в элементе 27 снимается сигнал, разрешающий поступление импульсов на распределитель испульсов в блоке 3. Время задержки в блоке 37 хз tnp + tea, где tnp - время преобразования ПНК 1; tea- время суммирования кодов в сумматоре 2 и записи кода в регистр 13 или 6.

Счетчик 11 предназначен для подсчета числа сдвигающих импульсов, поступающих в регистры 4 и 5. Сдвиг кода вправо в регистрах 4 и 5 соответствует делению на число осредняемых отсчетов NJ, если NJ равно значению числа два в целой степени. Шифратор 42 служит для преобразования единичного позиционного кода значений log2Nj, снимаемого со счетчика 9 в двоичный код. По сигналу с блока 3 одновибратор 43 формирует

импульс, по которому в старший разряд счетчика 40 записывается 1, а в остальные - дополнительный код значения logzNj. Сдвигающие импульсы из блока 3 поступают на третий вход счетчика 11. Через элемент 39 они поступают на счетный вход счетчика 40, в котором осуществляется их подсчет. При прохождении требуемого количества импульсов со старшего разряда счетчика 40 снимается сигнал, запрещающий поступление сдвигающих импульсов на регистры 4 и 5 через элемент 41, выполняющий функцию вентиля.

45

Формула изобретения

1. Устройство аналого-цифрового преобразования, содержащее преобразователь напряжение - код, первый вход которого является входной шиной, второй

0 вход соединен с выходом первого элемента И, первые выходы соединены соответственно с входами первой группы входов сумма- тора-осреднителя, а второй выход соединен с первым входом сумматора-осреднителя,

5 выходы которого соединены соответственно с первыми входами первого и второго регистров, выходы последнего из которых соединены соответственно с входами второй группы входов сумматора-осреднителя, второй вход которого соединен с первым

выходом блока управления, второй выход которого соединен с первыми входами первого счетчика и первого элемента И, второй вход которого соединен с первым выходом первого счетчика, вторые входы которого объединены с соответствующими первыми входами второго счетчика и с соответствующими выходами реверсивного счетчика, выход второго счетчика соединен с первым входом третьего регистра и вторым входом первого регистра, выходы которого соединены с входами первого и второго цифровых компараторов, первые выходы которых соединены соответственно с входами Сложение и Вычитание реверсивного счетчика, выходы третьего регистра являются выходной шиной, отличающееся тем, что, с целью повышения быстродействия, в него введены четвертый регистр, триггер, второй, третий и четвертый элементы И, пер- вый и второй входы которого соединены соответственно с вторыми выходами первого и второго цифровых компараторов, третий вход объединен со Счетным входом реверсивного счетчика и соединен с треть- им выходом блока управления, а выход соединен с вторым входом третьего регистра, третий вход которого объединен с третьим входом первого регистра и соединен с первым выходом блока управления, четвертые входы третьего регистра соединены соответственно с выходами второго регистра, второй вход которого объединен с третьим входом сумматора-осреднителя и соединен с выходом второго элемента И, первый вход которого соединен с первым выходом триггера, второй выход которого соединен с первым входом третьего элемента И, а вход объединен с вторыми входами второго, третьего элементов И и первым входом сум- матора-осреднителя, выход третьего элемента И соединен с четвертым входом сумматора-осреднителя, выходы которого

соединены с соответствующими первыми входами четвертого регистра, второй вход которого объединен с третьим входом второго регистра, вторым входом второго счетчика и третьим входом первого счетчика и соединен с четвертым выходом блока управления, третий вход четвертого регистра соединен с выходом третьего элемента И, а выходы соединены с соответствующими входами третьей группы входов сумматора- осреднителя, пятый выход блока управления соединен с третьим входом второго счетчика, второй выход первого счетчика соединен с первым входом блока управления, второй вход которого объединен с входом установки реверсивного счетчика и является шиной Пуск.

2, Устройство по п. 1, о т л и ч а ю. ще е- с я тем, что блок управления выполнен на двух элементах И, двух одновибраторах, дешифраторе, двух счетчиках и генераторе импульсов, выход которого соединен с входом первого счетчика, первыми входами первого и второго элементов И, второй вход последнего соединен с первым выходом дешифратора, второй выход которого является третьим выходом блока, первым выходом которого является третий выход дешифратора, четвертый выход которого соединен с входом первого одновибратора, выход которого является четвертым выходом блока, входы дешифратора соединены с сответствующими выходами второго счетчика, вход запуска которого является вторым входом блока, а счетный вход соединен с выходом первого элемента И, второй вход которого является первым входом блока, выход второго элемента И является пятым выходом блока, выход первого счетчика соединен с входом второго одновибратора, выход которого является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1451861A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU432676A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ АКТИВНОЙ МОЩНОСТИ | 1993 |

|

RU2074397C1 |

| Двухотсчетный преобразователь синусно-косинусно-модулированных сигналов переменного тока в код | 1985 |

|

SU1283969A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

Изобретение относится к цифровой электроизмерительной технике и может использоваться в информационно-измерительных системах и системах автоматического управления, работающих в условиях аддитивных случайных помех-. Изобретение позволяет повысить быстродействие. Это достигается тем. что введением в устройство, содержащее преобразователь 1 напряжение-код, сумматор-осреднитель 2, блок 3 управления, регистры 4-6, реверсивный счетчик 9, счетчики 10 и 11. цифровые компараторы 7 и 8, элемент И 12, введены регистр 13, триггер 14, элементы И 15-17. При этом за счет сравнения осредненных отсчетов, получаемых на одном интервале цифрового интегрирования, уменьшается влияние низкочастотных помех на время поиска числа осредняемых отсчетов, обеспечивающих заданную погрешность преобразования. 1 з.п. ф-лы. 6 ил. w ё о Јь VI 00 о 4

Отб ОтКМОаКбтНоЗ

-JxSJJ

-, ь

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| - М.: Энергия, 1970, с | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1989-01-18—Подача