с вторым входом второй группы второго элемента 2-2 И-2 ИЛИ и с вторым входом первой группы з-ооого элемента 2-3 И-2 ИЛИ, первий BXO/J первой группы первого элемента 2-2 И-2 ИЛИ, подключен к первому входу первой группы первого элемента 2-3 И-2 ИЛИ и к первому входу первой группы элемента 2-1-2 И-3 ИЛИ второй вход второй группы первого элемента 2-2 И-2 ИЛИ соединен с пер

вым входом первой группы первого элемента 2-3 И-2 ИЛИ, второй вход третьей группы элемента 2-1-2 И-3 ИЛИ подключен к второму входу первой группы второго элемента 2-2 И-2 ИЛИ и к первому входу второй группы второго элемента 2-3. И-2 ИЛИ, первый вход второй группы, второго элемента 2-2 И-2 ИЛИ соединен с первым входбм , первой группы второго элемента 2-3 И-2 ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи цифровой информации на магнитный носитель | 1973 |

|

SU470855A1 |

| Устройство магнитной записи цифровой информации | 1982 |

|

SU1062774A1 |

| Устройство для магнитной записи цифровой информации на диски | 1978 |

|

SU769608A1 |

| Устройство детекмирования сигналов воспроизведения с магнитного диска | 1984 |

|

SU1205180A1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство кодирования информации для записи на магнитный носитель | 1982 |

|

SU1045382A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство записи-воспроизведения многоканальной цифровой информации на магнитный носитель | 1991 |

|

SU1777176A1 |

1 Изобретение относится к записи ди кретных или цифровых данных и предна начено для использования в вычислительной технике, в частности в запоминающих устройствах на магнитных но сителях. Известно устройство предварительной компенсации при записи цифровой информации, содержащее регистр сдвиг блок выделения образца, блок обнаружения ошибки, блок сдвига импульсов, блок генерирования задержанных синхроимпульсов, усилитель записи, шину цифровой информации, шину импульсов синхронизации, информационный вход регистра сдвига соединен с шиной циф ровой информации, а синхронизирующий с входом блока генерирования задержа ных синхроимпульсов. Регистрсдвига состоит из последовательно соединенных триггеров первой группы и послЬдовательно соединенных триггеров второй группы, выходы триггеров, обеих групп соединены с входами блока . выделения образца, выход последнего триггера первой группы дополнителЬно соединен с разрешающим входом бло ка сдвига импульсов, управляющие вхо :ДЫ которого подключены к выходам блока выделения образца, коммутируюiщие входы блока сдвига,импульсов соединены с выходами блока генерирования задержанных синхроимпульсов, выход блока сдвига импульсов подключен к входу блока записи Q, Недостатком указанного устройства предварительной компенсации при записи .цифровой информации заключается в малой -точности компенсации, так ка не учтено изменение разрешающей способности пар магнитная головка - ма1- нитная поверхность при переходе от одной пары к другой и при изменении радиуса дорожки (цилиндраJ, Наиболее близким к предлагаемому явлйется устройство для магнитной заСиси цифровой информации на диски, содержащее регистр сдвига с входом импульсной последовательности информации, входом синхроимпульсов и входом, установки схемы в исходное состояние, дешифратор, входами подключенный к-выходам регистра сдвига, коммутатор, управляющими входами подключенный к выходам дешифратора, а инфор мационным входом - к центральному выходу регистра сдвига, схему выработки задержанных синхросерий, вход которой подключен к входу синхроимпульсов, а выходы - к соответствующим входам коммутатора, усилитель записи , под1слюченный к выходу коммутатора, блок управления схемой выработки задержанных синхросерий, вход которого подключен к входу адреса дорожки , а .выходы - к дополнительным входам управляемой схемы выработки задержанных синхросерий Г Устройство позволяет изменять величину вводимых предыскажений в записываемый сигнал в зависимости от радиуса дорожки диска и тем самым повысить плотность записи. Однако в данном случае не учитывается разброс параметров пар магнитная головка - носитель, что также не позволяет достичь высокой томности компенсации.. Цель изобретения - повышение точности компенсации. Указанная цель достигается тем, что в устройство для записи сигналов цифровой информации, содержащее регистр сдвига, выходы которого подклю чены к соответствующим входам дешифратора , а информационный вход и синх ровход - к шинам сигналов цифровой информации и синхроимпульсов, коммутатор, выход которого связан с входом блока записи, блок формирования задержанных синхросерий, вход которого соединен с шиной синхроимпуль сов, а выходы - с первой группой вхо дов коммутатора, разрешающий вход ко торого подключен к выходу среднего разряда регистра сдвига, блок управления- с подключенной к его первому управляющему входу адресной шиной, введены дополнительная адресная шина и подключенный к ней блок хранения кодов разрешающей способности, выход которого соединен с вторым управ ляющим входом блока управления, вклю ченного между выходами дешифратора и второй группой входов коммутатора, при этом блок управления содержит элемент ИЛИ с прямым и инверсным выходами, два элемента 2-2 И-2 ИЛИ, два элемента 2-3 И-2 ИЛИ и элемент 2-1-2 И-3 ИЛИ, при этом первый вход первой группы первого элемента 2-2 И-2 ИЛИ, первый вход первой группы первого элемента 2-3 И-2 ИЛИ, вход второй группы элемента 2-1-2 И-3 ИЛИ второй вход первой группы второго элемента 2-2 И-2 ИЛИ и первый вход первой группы второго элемента 2-3 И-2 ИЛИ являются соответственно первым, вторым, третьим, четвертыми пятым информационными входами блока управления, выходами блока управления являются выходы первого элемента 2-2 И-2 ИЛИ первого элемента 2-3 И-2 ИЛИ, элемента 2-1-2 И-3 ИЛИ, вто рого элемента 2-2 И-2 ИЛИ и второго элемента 2-3 И-2 ИЛИ, один вход элемента ИЛИ подключен к выходу блока

хранения кодов разрешающей способное; 45 «формации (фиг. 1 и 2 , шину 2 нити, к второму входу второй группы первого элемента 2-3 И-2 ИЛИ и к третьему входу второй группы второго элемента 2-3 И-2 ИЛИ, другой вход элемента ИЛИ соединен с адресной ши- 50

ной номеров цилиндров, с третьим входом второй группы первого элемента 2-3 И-2 ИЛИ и с вторым входом второй группы второго элемента 2-3 И-2 ИЛИ, прямой выход э-лемент9 ИЛИ подключен 55 к второму входу первой группы первого элемента 2-2 И-2 ИЛИ, к второму входу первой группы первого элемента 2-3 И-2 ;

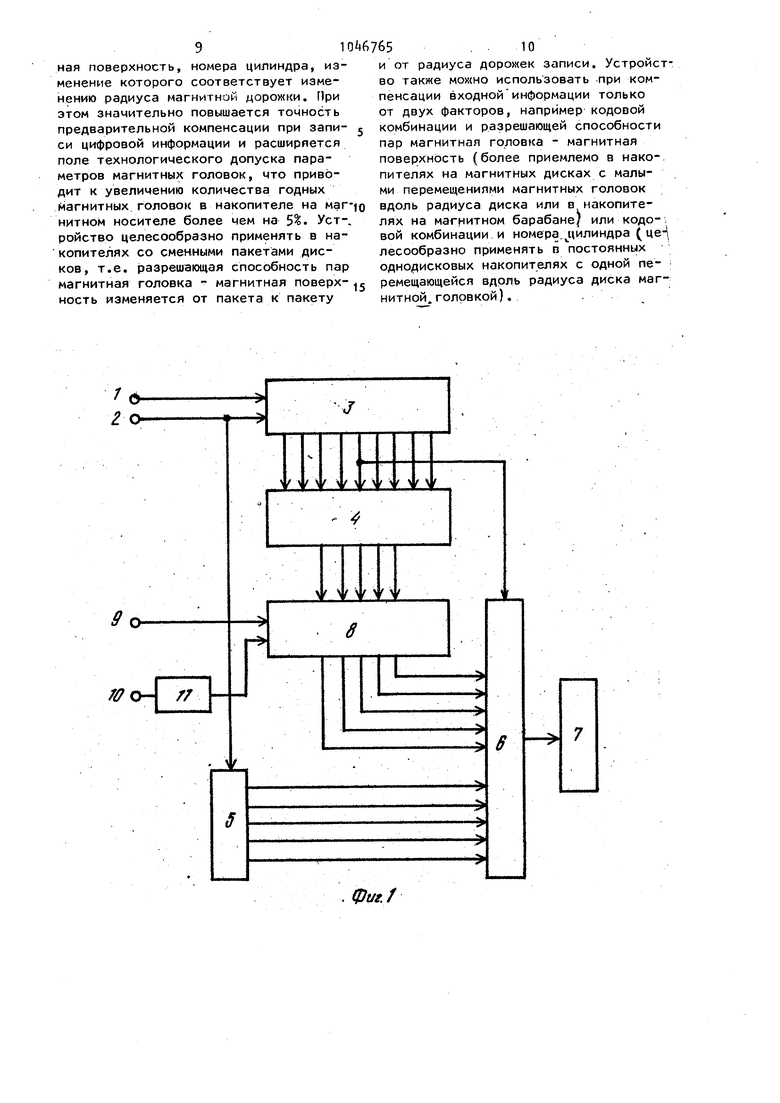

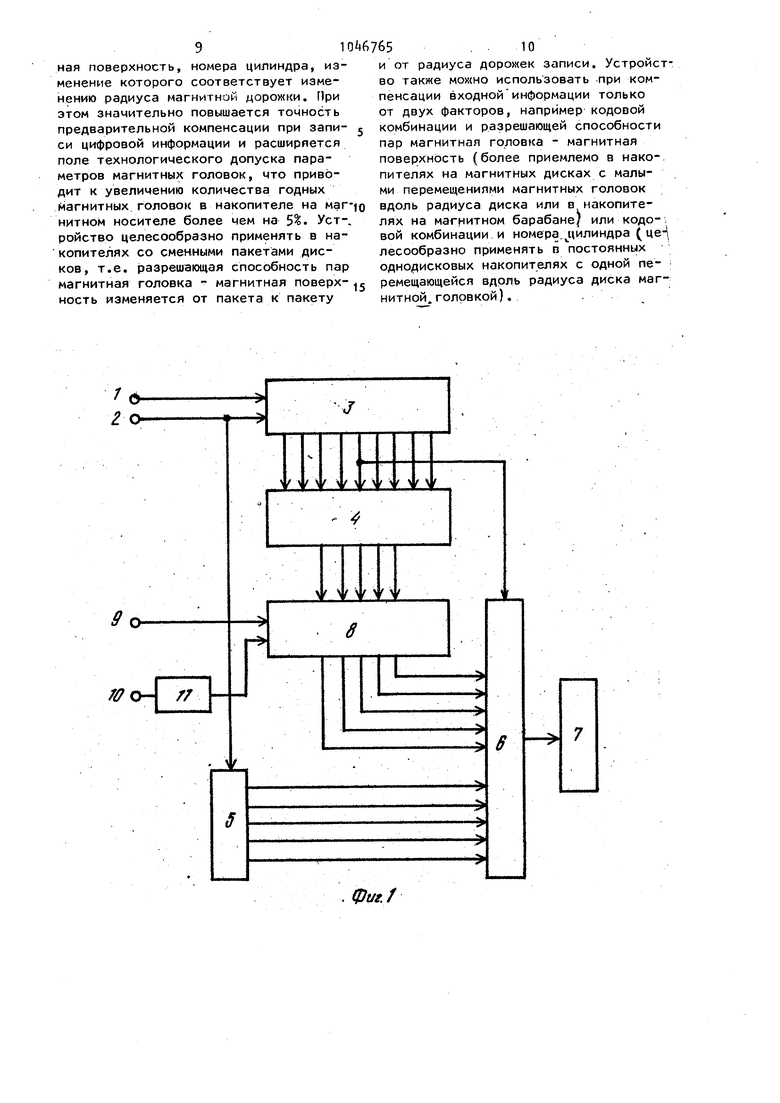

пульсов синхронизации, регистр 3 сдвига, дешифратор k, блок 5 формирования задержанных синхросерий,коммутатор 6, блок 7 записи, блок 8 управ- .

ную адресную.шину 10, блок 11 хранения кодов разрешающей способности

Шина 1 цифровой информации предназначена для приема сигналов цифровой информации на вход устройства. Шина 2 импульсов синхронизации пред .назначена для синхронизации работы устройства. Информационный вход реИЛИ и к первому входу второго элемента -2 И-2 ИЛИ,инверсный выход элемента ИЛИ соединен с первымгвходом второй группы первого элемента 2-2 И-2 ИЛИ,с вторым входом первой группы элемента 2-1-2 И-3 ИЛИ, с первым входом третьей группы элемента 2-1-2 И-3 ИЛИ, с вторым входом второй группы второго элемента 2-2 И-2 ИЛИ и с вторым входом первой группы второго элемент-а 2-3 И-2 ИЛИ, первый вход первой группы первого элемента 2-2 И-2 ИЛИ подключен к первому входу первой группы первого элемента 2-3 И-2 ИЛИ и к первому входу первой группы элемента 2-1-2 И-3 ИЛИ, второй вход второй группы первого элемента 2-2 И-2 ИЛИ соединен с первым входом первой группы первого элемента 2-3 И-2 ИЛИ, второй вход третьей группы элемента 2-1-2 И-3 ИЛИ подключен к второму ВХОДУ первой группы второго элемента -2 И-2 ИЛИ и к первому входу второй группы второго элемента 2-3 И-2 .1ЛИ, первый вход второйгруппы второго элемента 2-2 И-2 ИЛИ соединен с первым входом первой группы второго элемента 2-3 И-2 ИЛИ. Блок управления вырабатывает сигнал оптимальной величины компенсации сигналов входной цифровой информации в зависимости от сигналов на его информационных и управляющих входах путем сдвига записываемого сигнала в сторону, противоположную сдвигу этого сигнала при воспроизведении. На фиг. 1 изображено устройство для записи сигналов цифровой инфор- . мации, блок-схема; на фиг. 2 - функциональная схема устройства; на фиг, 3 - временные диаграммы, поясняющие работу устройства. Устройство предварительной компенсации при записи цифровой информации содержит шину 1 цифровой инления, адресную шину 9, дополнительгистра 3 сдвига соединен с шиной 1, , а синхронизирующий вход - с шиной 2. Выходы регистра 3 сдвига подключены к входам дешифратора k, который состоит из элементов И12-15 и элемента ИЛИ-НЕ 16 и предназначен для выработки на выходе сигналов, соответствующих комбинациям цифровой информации на его входе Блок 5 формирования задержанных синхросерий . состоит из последовательно соедин(бнных элементов задержки. Вход блока 5 подключен к шине 2, а выходы соединены с первой группой входов коммутатора 6, который состоит из v элементов 3 И 21-25 и элемента 5 ИЛИ 26 и представляет собой мультиплексор. Разрешающий вход коммутатора 6 подключен к(3-выходу регистра 3 сдвига. Блок 8 управления состоит из элемента ИЛИ 27 с прямым и инверсным выходами, элемента 2-2 И-2 ИЛИ 28 элемента 2-3 И-2 ИЛИ 29, элемента 2-1-2 И-3 ИЛИ 30, элемента 2-2 И-2 ИЛИ 31 и элемента 2-3 И-2 ИЛИ 32, пр этом первый вход первой группы элемента 2-2 И-2 ИЛИ 28 первый вход первой группы элемента 2-3 И-2 ИЛИ 2 вход второй группы элемента 2-1-2 И-3 ИЛИ 30, второй вход первой групп элемента 2-2 И-2 ИЛИ 28 и первый вхо первой группывторого элемента 2-3 И-2 ИЛИ 32 образуют соответственно -первый, второй, третий, четвертый и пятый информационные входы блока 8 управления, выходы которого являются выходами элемента 2-2 И-2 ИЛИ 28, эл мента 2-3 И-2 ИЛИ 29, элемента 2-1-2 И-3 ИЛИ 30, элемента 2-2 И-2 .ИЛИ 31 и элемента 2-3 И-2 ИЛИ 32,первый вход элемента ИЛИ 27 подключен к выходу блока 11 хранения кодов разрешающей способности,к второму входу второй группы элемента 2-3 И-2 ИЛИ 29 и к третьему входу второй труппы элемента 2-3 И-2 ИЛИ 32. Второй вход элемента ИЛИ 27 соединен с адресной шиной 9, с третьим входом второ группы элемента 2-ЗИ-2 ИЛИ 29 и с вторым входом второй группы элемента 2-ЗИ-. ИЛИ 32. Прямой выход элемента ИЛИ 27 подключен к второму входу первой группы элемента 2-2И-2 ИЛИ 28, к вто рому входу первой группы элемента 2-3 И-2 ИЛИ 29 и к первому входу элемента 2-2И-2 ИЛИ 31. Инверсный выход элемента ИЛИ 27 соединен с первым входом второй группы элемента 2-2И-2 ИЛИ 28 с вторым входом пер 10 . вой группы элемента 2-1-2 И-3 ИЛИ 30, с первым входом третьей группы элемента 2-1-2 И-3 ИЛИ 30, с вторым входом второй группы, элемента 2-2 И-2 ИЛИ 31 и с вторым входом первой группы элемента 2-3 И-2 ИЛИ 32. Первый вход первой группы элемента 2-2 И-2 ИЛИ 28 подключен к первому вхрду первой группы элемента 2-3 И-2 ИЛИ 29 и к первому входу первой группы элемента 2-1-2 И-3 ИЛИ 30 Второй второй группы элемента 2-2 И-2 ИЛИ 28 соединение первым входом первой группы элемента 2-3 И-2 ИЛИ 29. Второй вход третьей группы элемента 2-1-2 И-3 ИЛИ 30 подключен к второму входу первой группы элемента 2-2 И-2 ИЛИ 31 и к первому входу второй группы элемента 2-3 И-2 ИЛИ 32, первый вход второй группы элемента 2-2 И-2 ИЛИ 31 соединен с первым входом первой группы элемента 2-3 И-2 ИЛИ 32. Информационные входы блока 8 управления соединены с выходами дешифратора k, а выходы блока 8 управления подключены к второй группе входов коммутатора 6. Адресная шина 9 предназначена для приеме на первый управляющий вход блока 8 управления си|- нала номера цилиндра. Адресная шина 10 предназначена для приема сигналов номера магнитной головки на адресные входы блока 11 хранения кодов разрешающей способности пир магнитная головка - магнитная поверхность, в качестве которого можно использовать стандартное ПЗУ (например микросхему 155 РЕЗ)„ Рассмотрим работу устройства по функциональной схеме ( фиг. 2К Сигналы входной цифровой информации фиг. За) подаются на информационный вход регистраЗ сдвигаи сдвигаются (сдвиг происходит в направлении слева направо) на один разряд по каждому синхроимпульсу (фиг. , поступающему на вход синхронизации регистра сдвига 3. С выхода регистра 3 сдвига сигналы цифровой информации (фиг. 3с)- цифровая последовательность наQ-выходе регистра 3 сдвига, цифровая последовательность на; выходах Т), Е ,f , б, Н, | ,7, К регистра 3 сдвига представляет собой цифровую последовательность на С|-аыходе регистра 3 сдвига, сдвинутую D каждом такте работы устройства на один разряд, подаются на входы 7 . , дешифратора 4, где в каждом такте работы устройства происходит сравнъ ние поступающей комбинации сигналов цифровой информации с, образцовыми комбинациями (табл. l) , если имеется равенство,, то на соответствующем выходе блока выделения образца t вы рабатывают сигнал, который указывает С D EFGHI JK

- безразличное состояние.

Компенсация от номера магнитной головки

Компенсация от номера цилиндра

Результирующая величина компенсации

Ifr - компенсация не производится.

Направление компенсации задаё тся кодовой последовательностью. С выхода блока 8 управления на вторую группу входов коммутатора 6 подают сигналы, разрешающие прохождение на выход устройства сигналов, задержанных во времени (фиг, 3 т,и) или поступающих во времени раньше { фиг. 3 Б,R.) на величину Д-fc-i или -bj относительно сигналов (фиг.35) , которые подают на выход устройства, если входной сигнал не компенсируют. Сигналы на выходе блока 6 .сдвига импульсов фиг.ЗV) представляют собой скомпенсированную входную цифровую информацию.

Для пояснения работы логического преобразователя пр.едставлена табл. 2.

Таблица 2.

u.t A.t Д.Ц A-t At, &t, At,

Введение в предлагаемое устройство адресной шины номера магнитных голово и блока хранения кодов разрешающей способности пар магнитная головка магнитная поверхность выгодно отличает это устройство от устройства преварительной компенсации при записи цифровой информации, применяемое в системе накопителя на магнитных дисках ЕС-5080, который принят за баэовый образец, так как предварительная компенсация осуществляется не только в зависимости от. кодовой комбинации данных, поступающих на вход устройства, но и от разрешающей способности пар магнитная головка - магнит5 8I Сигналы с выхода дешифратора и поступают на информационные входы блока 8 управления. Наличие единичного сигнала на первом управляющем входе блока управления указывает на то, что необходимо произвести дополнительную компенсацию сигналов входной информации в .зависимости отномера цилиндра, нулевой сигнал указывает на отсутствие дополнительной компенсации. Единичный сигнал, поступающий на второй управляющий вход блока управления с выхода блока хранения кодов разрешающей способности, указывает на то, что необходимо произвести дополнительную компенсацию в зависимости от номера магнитной Толовки. Нулевой сигнал указывает на отсутствие дополнительной компенсации. . .

ная поверхность, номера цилиндра, изменение которого соответствует изменению радиуса магнитной дорожки, 1ри этом значительно повышается точность предварительной компенсации при записи цифровой информации и расширяется поле технологического допуска параметров магнитных головок, что приводит к увеличению количества годных Магнитных головок в накопителе на маг нитном носителе более чем на 5. Уст-, ройство целесообразно применять в накопителях со сменными пакетами дисков, т.е. разрешающая способность пар магнитная головка - магнитная поверхность изменяется от пакета к пакету

J

70

f f f f f

f f f

и от радиуса дорохчек записи. Устройство также использовать при компенсации входнойинформации только от двух факторов, например кодовой комбинации и разрешающей способности пар магнитная головка - магнитная поверхность (более приемлемо в нако-. пителях на магнитных дисках с малыми перемещениями магнитных головок вдоль радиуса диска или в накопителях на магнитном барабане/ или кодо-; вой комбинации и номера.чцилиндра ( целесообразно применять п постоянных однодисковых накопителях с одной пе- ремещающейся вдоль радиуса диска магнитной, головкой), .

Фие./ ra

фиг-З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| КОМПЕНСАЦИОННОЕ УСТРОЙСТВО К ВЕСАМ, У КОТОРЫХ ВЕС ВЗВЕШИВАЕМОГО ТЕЛА УРАВНОВЕШИВАЕТСЯ ЭЛЕКТРОМАГНИТНОЙ СИЛОЙ | 1933 |

|

SU38793A1 |

| Способ приготовления искусственной массы из продуктов конденсации фенолов с альдегидами | 1920 |

|

SU360A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для магнитной записи цифровой информации на диски | 1978 |

|

SU769608A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-10-07—Публикация

1982-04-05—Подача