Изобретение относится к приборостроению и может быть использовано в точной магнитной записи в цифровых накопителях на магнитной ленте.

Известно устройство для записи и воспроизведения цифровой информации, содержащее в записывающий части делитель, блок умножения частоты, по два элемента И, блока памяти, регистра, счетчика, формирователя, три элемента ИЛИ, кодер, аппарат магнитной записи, а в воспроизводящей части - декодер, делитель, три элемента И, регистр, блок памяти, блок восстановления

синхронизации, сдвигающий регистр, два формирователя, счетчик и блок сравнения. .Данноеустройство позволяет использовать код обнаружения ошибки для синхронизации воспроизводимой информации. Однако в случае отсутствия в цифровой информационной последовательности единиц возникают трудности для ее восстановления при воспроизведении. Это является недостатком устройства.

Наиболее близким по технической сущности к заявляемому устройству записи воспроизведения многоканальной цифро41

о

вой информации на магнитный носитель является устройство, состоящее из записывающей и воспроизводящей частей. Записывающая часть содержит делитель, распределитель импульсов, блок формирователя сигналов записи, элемент ИЛИ и п информационных каналов, каждый из которых включает в себя два элемента И, регистр, формирователь и счетчик. В воспроизводящей части устройство содержит блок формирования сигналов воспроизведения и п информационных каналов, каждый из которых состоит из регистра, двух схем сравнения, формирователя, двух счетчиков, четырех элементов И, двух ОЗУ и элемента ИЛИ.

Недостатком данного устройства является недостаточная помехозащищенность за счет того, что могут встречаться комбинации в массивах регистрируемой информации, состоящие из одних нулей.

Целью изобретения является повышение помехозащищенности за счет улучшения свойств синхронизации каждого канала.

Поставленная цель достигается тем, что в известное устройство записи-воспроизведения многоканальной цифровой информации на магнитный носитель, содержащее в записывающей части входные информационные шины, шину синхронизации, соединенную с входом делителя, формирователь и п информационных каналов, в каждом из которых содержится счетчик, а в воспроизводящей части - п информационных каналов, каждый из которых включает регистр, первое оперативное запоминающее устройство (ОЗУ), два элемента И, выходы которых соединены с входами элемента ИЛИ, и аппарат для записи и воспроизведения, в записывающую часть введены коммутатор, элемент задержки, триггер, вход которого соединен с выходом элемента задержки, с установочными входами счетчиков п каналов и первыми входами коммутатора и аппарата для записи и воспроизведения, а в каждый канал введены два ОЗУ, дешифратор, триггер и элемент ИЛИ, выходы каждого из которых подключены к соответствующим информационным входам аппарата для записи и воспроизведения, первый и второй входы соединены с выходами ОЗУ, выходы триггеров подключены к информационной группе входов ком- мутатора, первые входы соединены с выходами дешифратора, а вторые входы триггеров каждого канала связаны между собой, с вторым входом коммутатора, с выходом формирователя и входом элемента задержки, входы дешифраторов соединены

с соответствующими выходами счетчиков, входные информационные шины подключены к первым входам ОЗУ и счетчика своих каналов, шина синхронизации связана с

вторыми входами ОЗУ всех каналов, вторым входом аппарата для записи и воспроизведения и третьим входом коммутатора, при этом первый, выход триггера подключен к управляющим входам первых ОЗУ всех ка0 налов, а второй выход - к управляющим входам вторых ОЗУ, выход делителя связан с входом формирователя, первый выход коммутатора соединен с дополнительным информационным входом аппарата для за5 писи и воспроизведения, а остальные выходы соединены с третьими входами элементов ИЛИ соответствующих каналов, в воспроизводящую часть введены формирователь, триггер, декоммутатор, а в каждый

0 канал - второе ОЗУ, второй и третий регистры и второй элемент ИЛИ, входы которого соединены с выходами ОЗУ, а выходы-с соответствующими информационными входами декоммутатора, выходы первого элемента

5 ИЛИ каждого канала подключены к соответствующим группам управляющих входов декоммутатора, первые входы первых ОЗУ всех каналов соединены между собой и подключены к первым входам второго регистра,

0 первого элемента И своих каналов И к первому выходу триггера, первые входы вторых ОЗУ всех каналов соединены между собой и подключены к первым входам третьего регистра и второго элемента И своих каналов

5 и второму выходу триггера, выход формирователя соединен с первыми входами первых регистров всех каналов, а его вход связан с входом триггера и первым выходом аппарата для записи и воспроизведения, второй

0 выход аппарата для записи и воспроизведения подключен к вторым входам первых регистров и вторым входам обоих ОЗУ всех каналов и выходной шине синхронизации, информационные выходы аппарата для за5 писи и воспроизведения первых (п-1) каналов подключены к третьим входам первых регистров и двух ОЗУ соответствующих каналов, информационный выход п канала аппарата для записи и воспроизведения

0 соединен с третьими входами двух ОЗУ своего канала, а дополнительный информационный выход связан с третьим входом первого регистра п канала, при этом в каждом канале выходы первого регистра соеди5 нены с соответствующими входами второго и третьего регистров, выходы второго и третьего регистров подключены к входам перво/о и второго элементов И, а выходы декоммутатора связаны с выходными информационными шинами.

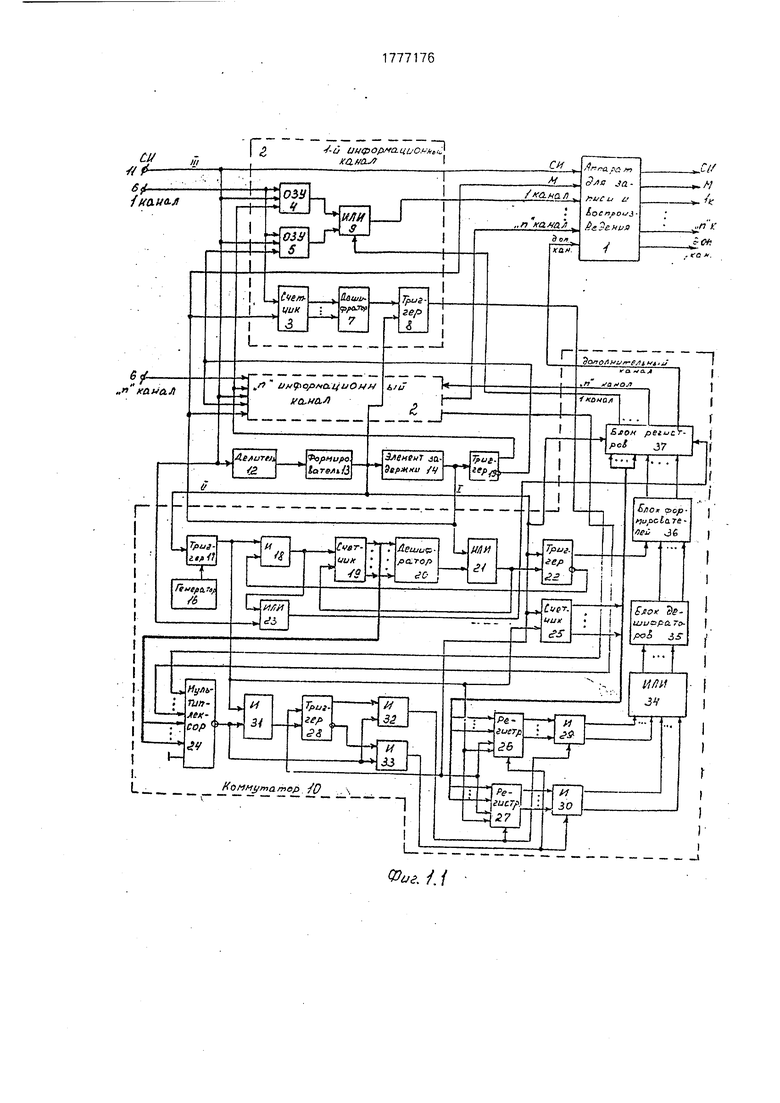

Коммутатор содержит генератор, три триггера, три логических элемента ИЛ И, два счетчика, дешифратор, блок дешифраторов, два регистра, блок регистров, мультиплексор, два ключа, четыре логических элемента И и блок формирователей, вход которого соединен с первым выходом второго триггера, группа входов подключена к выходам блока дешифраторов, а выходы связаны с входами блока регистров, другая группа входов которого соединена с соответствующими выходами второго счетчика и соответствующими входами первого и второго регистров, первый вход блока регистров подключен к первым входам первого и второго регистров, первым входам всех триггеров, первому входу второго счетчика и второму входу коммутатора, второй вход блока регистров соединен с выходом перЕЮ- го логического элемента ИЛИ, первый вход которого связан с третьим входом коммутатора, а второй соединен с выходом первого логического элемента И и первым входом первого счетчика, второй вход первого счетчика подключен к выходу второго логического элемента ИЛИ и второму входу второго триггера, выходы первого счетчика соединены с соответствующими входами дешифратора и первой группой входов мультиплексора , вторая группа входов которого связана с группой входов коммутатора, выход мультиплексора подключен к первым входам второго, третьего и четвертого логических элементов И, второй вход второго логического элемента И соединен с выходом первого триггера, первым входом первого логического элемента И, вторым входом второго счетчика и тактовыми входами первого и второго регистров, установоч- ные входы которых подключены соответственно к управляющим входам первого и второго ключей и выходам третьего и четвертого логических элементов И, выходы первого и второго регистров соединены с информационными входами первого и второго ключей соответственно, выходы которых подключены к входам третьего логического элемента ИЛИ, выходы третьего логического элемента ИЛИ соединены с входами блока дешифраторов, выход генератора подключен к второму входу первого триггера, второй вход первого логического элемента И соединен с вторым выходом второго триггера, выход дешифратора связан с первым входом второго логического элемента ИЛИ, второй вход которого соединен с первым входом коммутатора, при этом выход второго логического элемента И подключен к счетному входу третьего триггера, выходы которого соединены с вторыми входами третьего и четвертого логических ментов И соответственно, а выходы блока регистров связгны с соответствующими выходами коммутатора.

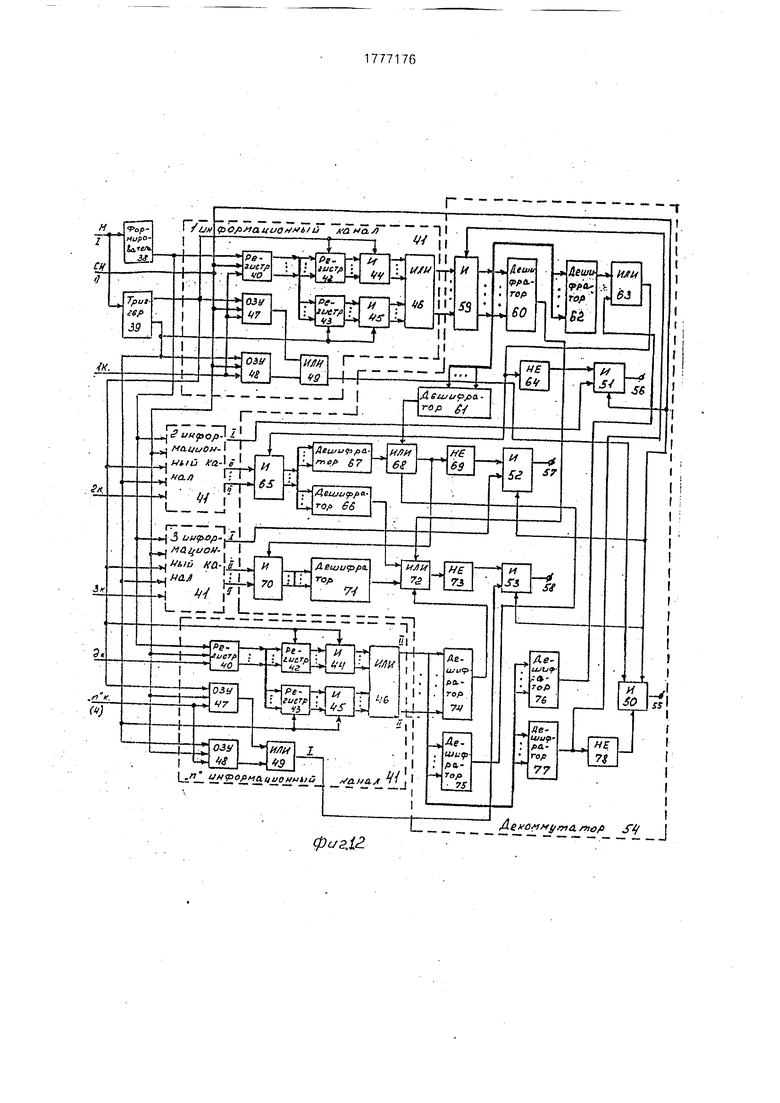

5Декоммутатор состоит из п каналов,

первый из которых включает в себя п дешифраторов, элементы НЕ и И, я каждый последующий канал содержит на один дешифратор меньше, чем в предыдущем кана- 10 ле, по два элемента И и по одному элементу НЕ и ИЛИ, при этом информационные входы декоммутатора соединены с первыми входами первых элементов И своих каналов, вторые входы которых подключены к выхо- 15 дам элементов НЕ, а выходы связаны с выходами декоммутатора, первая группа управляющих входов декоммутатора подключена к соответствующим входам п дешифраторов первого канала, остальные

0 группы управляющих входов через вторые элементы И соединены с входами дешифраторов своих каналов, при этом выходы первых дешифраторов всех каналов подключены к входам элемента ИЛИ п кана5 ла, выходы вторых дешифраторов-к входам элемента ИЛИ (п-10 канала и т.д., выход последнего дешифратора первого канала соединен с входом элемента НЕ своего канала и одним из входов второго элемента И

0 последующего канала, а выход элемента ИЛИ каждого канала (кроме первого) подключен к входу элемента НЕ своего канала и одному из входов второго элемента И последующего канала.

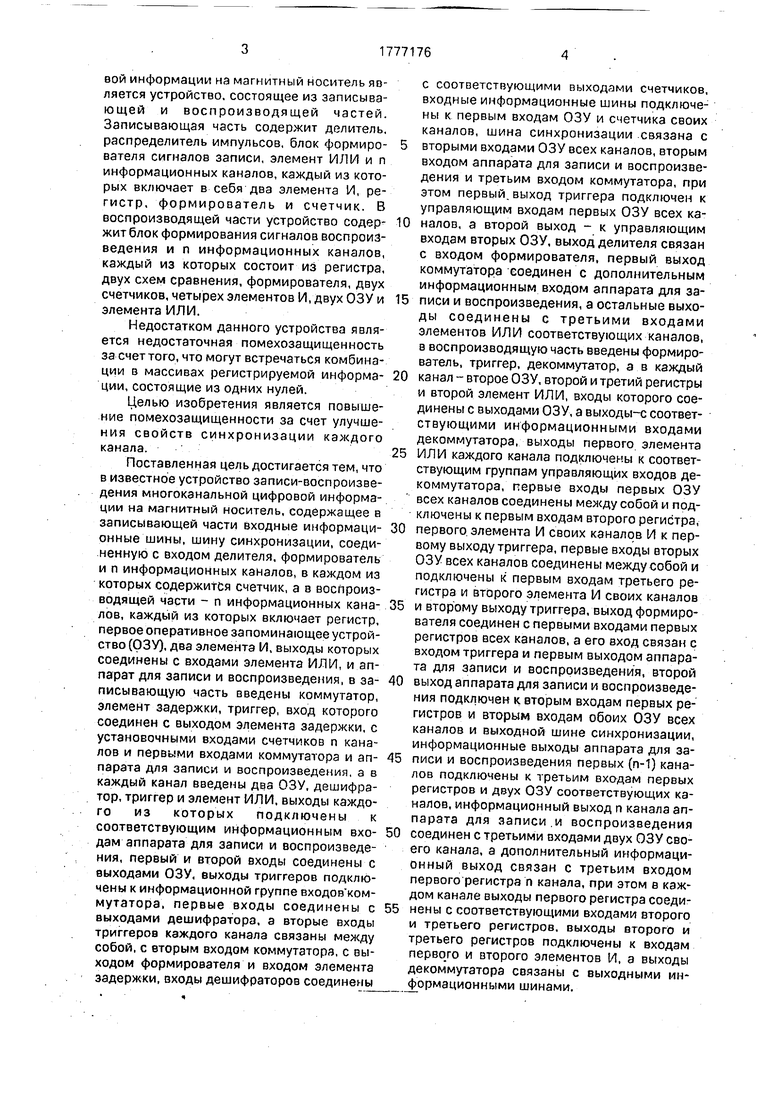

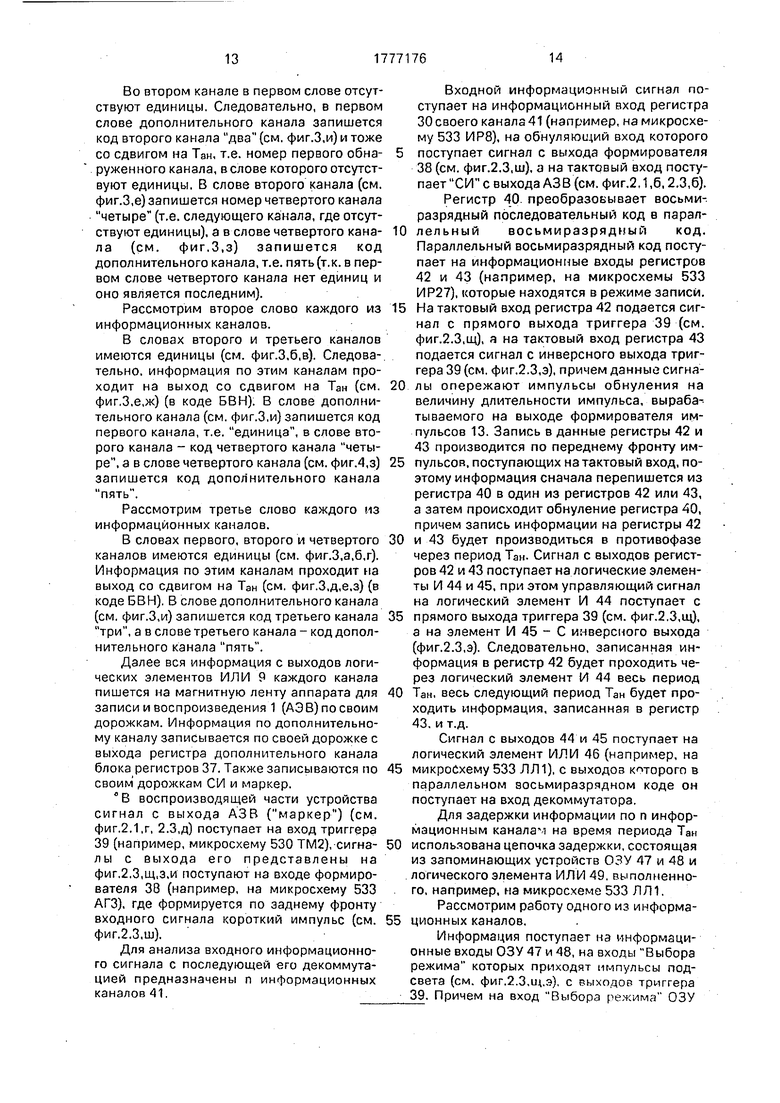

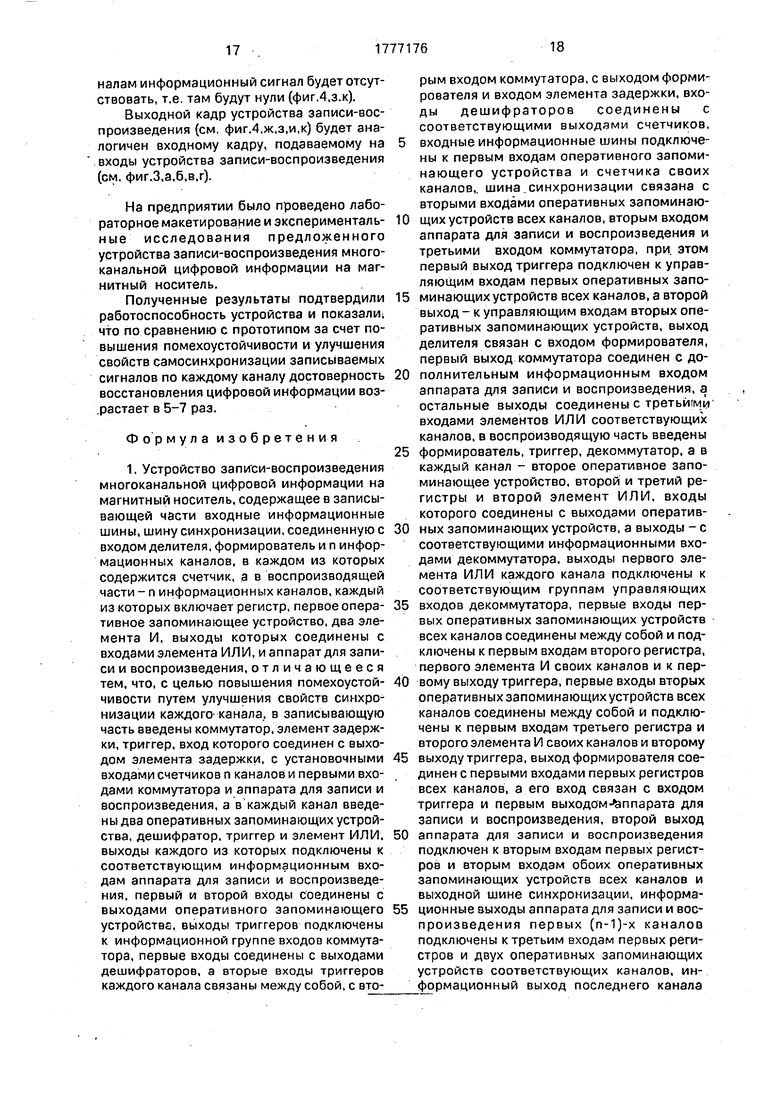

5Нафиг.1.1-1.2 приведена функциональная схема устройства записи-воспроизведения цифровой информации на магнитный носитель: на фиг.2-4 - временные диаграммы, поясняющие его работу.

0 Устройство содержит аппарат для записи и воспроизведения 1, п информационных каналов 2, в каждом из которых содержится счетчик 3, два оперативных запоминающих устройства (ОЗУ) 4 и 5, причем

5 входы счетчика 3, ОЗУ 4 и 5 подключены к соответствующим входным информационным шинам 6 своих каналов, выходы счетчика 3 соединены с входами дешифратора 7, подключенного к триггеру 8, и элемент ИЛИ

0 9, выхоцы каждого из которых подключены к соответствующим информационным входам аппарата для записи и воспроизведения 1, первый и второй входы соединены с выходами ОЗУ 4 и 5, а выходы триггеров 8

5 подключены к информационной группе входов коммутатора 10. Устройство содержит также шину синхронизации 1, соединенную с вторыми входами ОЗУ 4 и 5 всех информационных каналов 2. вторым входом эппарата для записи и воспроизведенич 1 третьим

входом коммутатора 10 и с входом делителя 12, подключенного к формирователю 13, к выходу которого подсоединены вторые входы триггеров 8 каждого информационного канала 2, второй вход коммутатора 10 и вход элемента задержки 14, а выход элемента задержки 14 связан с входом триггера 15, с установочными входами счетчиков 3 п информационных каналов 2 и с первыми входами коммутатора 10 и аппарата для записи и воспроизведения 1. Коммутатор 10 содержит генератор 16, последовательно соединенный с триггером 17, с логическим элементом И 18, со счетчиком 19, выходом связанным с дешифратором 20 и через логический элемент ИЛИ 21 - с триггером 22. Сигнал с выхода логического элемента И 18 поступает на вход логического элемента ИЛИ 23. Коммутатор 10 содержит также мультиплексор 24, информационные входы которого связаны с выходами триггеров 8 каждого канала, а адресные входы - с выходами счетчика 19, счетчик 25, входы которого соответственно соединены с выходом формирователя 13, с обнуляющими входами регистров 26 и 27, триггера 28 и с выходом триггера, с тактовыми входами регистров 26 и 27, при этом информационные входы регистров 26 и 27 связаны с выходами счетчика 25, а выходы их - соответственно с ключами 29 и 30. выполненными, например, на логических элементах И, на управляющие входы которых приходит сигнал с мультиплексора 24 через логический элемент 31, триггер 28 и логические элементы И 32 и 33, которые через логический элемент ИЛИ 34 подключены к блоку дешифраторов 35, состоящему из (п+1) дешифраторов. Коммутатор 10 содержит также блок формирователей 36, определяющий режимы записи или сдвига блока регистров 37, состоящий из (ги 1) регистров, на входы которых приходит информационный сигнал с выхода счетчика 25, а управляющие сигналы - с триггера 22 и блока дешифраторов 35, а выходы блока регистров 37 подключены соответственно к третьему входу логических элементов ИЛИ 9 своего информационного канала 2, при этом выход регистра дополнительного канала связан с дополнительным информационным входом аппарата для записи и воспроизведения 1.

В воспроизводящей части устройство содержит формирователь 38. входом связанный с триггером 39 и с первым выходом аппарата для записи и воспроизведения 1, а выходом подключенный к первым входам регистров 40 и к каждому из п информационных каналов 41. Каждый информационный канал содержит первый регистр 40,

выходами подключенный к второму 42 и третьему 43 регистрам, которые соответственно через логические элементы И 44 и 45 подключены к входам логического элемента

И 46. Управляющие сигналы с выходов триггера 39 соответственно поступают на управляющие входы регистров 42 и 43,логических элементов И 44 и 45 и ОЗУ 47 и 48, с выходов которых сигнал через логический элемент

0 ИЛ И 49 поступает на соответствующий своему каналу логический элемент И (50 - для первого канала, 51 - для второго канала, 52 - для третьего канала и т.д., 53 - для п канала, где п 4), которые входят в состав

5 декоммутатора 54, а через них - на соответствующую каждому каналу выходную информационнуюшину55-58. Информационные выходы аппарата для записи и воспроизведения 1 первых(п-1) кана0 лов подключены к третьим входам первых регистров 40 и двух ОЗУ 47 и 48 соответствующих каналов, информационный выход п канала аппарата для записи и воспроизведения соединен с третьими входами двух

5 ОЗУ 47 и 48 своего канала, а дополнительный выход связан с третьим входом первого регистра 40 п канала. В состав декоммутатора входят также последовательно соединенные многовходовый и логический

0 элемент И 59 (выполненный, например, на микросхемах 530 ЛА9), дешифраторы 60-62 (выполненные, например, на микросхемах 533 ЛАЗ) и логические элементы ИЛИ 63 и НЕ 64; последовательно соединенные мно

5 говходовый логический элемент И 65, дешифраторы 66 и 67 и логические элементы ИЛИ 68 и НЕ 69, последовательно соединенные миоговходовый логический элемент И 70, дешифратор 71 и логические элементы

0 ИЛИ 72 и НЕ 73 и последовательно соединенные дешифраторы 74-77 и логический элемент НЕ 78.

Устройство работает следующим образом.

5 Допустим, что импульсные последовательности каждого канала содержат по три слова, т.е. m 3, восьмиразрядного кода. Количество каналов примем, например, равным 4, т.е. п 4.

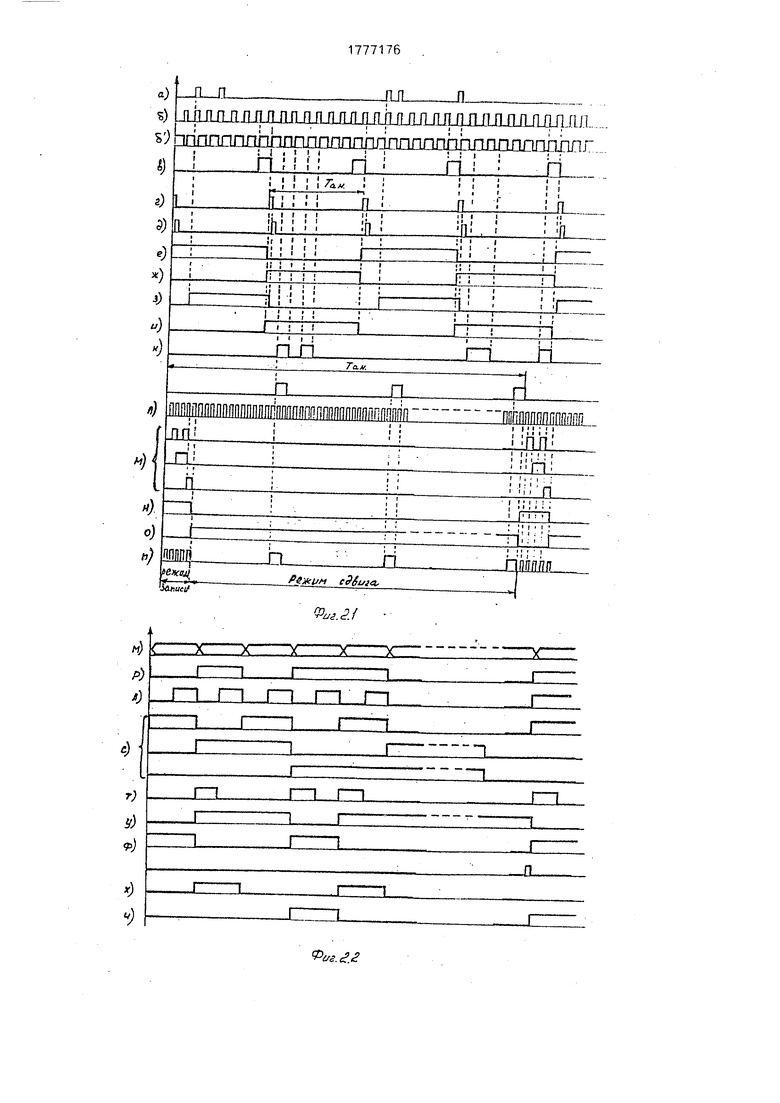

0 Синхросигнал (см. фиг.2.1,6) с шины синхронизации 11 поступает на вход делителя 12 на восемь (например, микросхемы 533 ИЕ7, 533 ЛАЗ), где формируется маркер в конце каждого слова через восемь тактов

5 СИ (период повторения его обозначим через Тан) (см. фиг.2.1.в), который поступает на формирователь 13 (например, микросхему 533 АГЗ), а с него сформированный по заднему фронту короткий импульс записи (фиг,2.1,г) поступает на элемент задержки

14, где он задерживается на величину дли- тепьности импульса и этот импульс обнуления (фиг.2.1,д) приходит на вход триггера 15 (например, микросхему 533 ТМ2), инверсный выход которого соединен с его D-вхо- дом.

Для анализа информации на отсутствие единиц в словах по всем п каналам предусмотрено п информационных каналов 2 в записывающей части устройства. Рассмотрим работу одного информационного канала, так как остальные работают аналогично. Входная информация (см. фиг,2.1,а) поступает на С-вход счетчика 3, выполненного, например, на микросхеме 533 ИЕ7, с кото- рого приходит на входы дешифратора 7, выполненного,например, на микросхеме 533 ЛАЗ. Если хотя бы на одном из входов счетчика 3 появится единица, что означает, что за время анализа Тан прошел хотя бы один информационный импульс, то на выходе дешифратора 7 устанавливается высокий импеданс (см. фиг.2.1 ,з). По приходу переднего фронта импульса записи с формирователя 13 (см. фиг.2.1,г) сигнал с выхода дешифра- тора 7 перепишется в триггер 8 (см. фиг.2.1,и). Импульсы обнуления с выхода элемента задержки 14 (см. фиг.2.1,д), период следования которых равен времени анализа Тат приходят следом за импульсом записи и обнуляют счетчик 3, подготавливая его к работе. Одновременно с приходом на вход Осчетчика 3 входная информация одновременно поступает на информационные входы ОЗУ 4 и 5, выполненные, например, по а.с. СССР Мг 1179362. кл. G 06 F 13/16. Также на входы Выбора режима ОЗУ 4 и 5 приходят импульсы подсвета с выходов триггера 15, причем на вход ОЗУ 4 приходят импульсы подсвета с прямого выхода триг- гера 15 (см. фиг.2.1,е), а на вход ОЗУ 5 - с инверсного выхода триггера 15 (см. фиг.2.1,ж). Это обусловлено тем, что одно ОЗУ работает в режиме записи, а другое - в режиме считывания попеременно в течение каждого Тан.. Для работы ОЗУ 4, на их вхсСды также поступают импульсы синхронизации с шины синхронизации 11. Считывание, задержанной на период Тан входной информации в последовательном коде из ОЗУ 4 или 5 осуществляется через логический элемент ИЛИ 9, выходной сигнал которого представлен на фиг.2.1,к, без учета сигнала, приходящего с выхода коммутатора 10, Коммутатор 10 работает следующим образом. С известного генератора 16 сигнал поступает на С-вход триггера 17, на обнуляющий вход которого поступает сигнал с формирователя 13. Выходной сигнал с триггера 17 через логический элемент И 1В подается

на счетный вход С счетчика 19 (оыпопненио го. например, на микросхеме 533 ИЕ15)(см. фиг.2.1,л). На выходе счетчика 19 формируются адреса опроса (n-Ч), т.е. в заданном случае 5 (п 4) (см; фиг.1.1,м), за время Тан. Эту функцию выполняют дешифратор 20, логический элемент ИЛИ 21, триггер 22 и логический элемент И 18 следующим образом. С выхода счетчика 19 (п-1-) код (в данном случае 5) приходит на дешифратор 20, на выходе которого появляется 1, которая через логический элемент ИЛИ 21 приходит на Р-вход счетчика 19, обнуляя его. а поступая на триггер 22, перебрасывает его в О (см. фиг.2.1,н), что закрывает счетный вход счетчика 19 через логический элемент И 18 до прихода импульсов обнуления (см. фиг.2.1,д), которые поступают в начале следующего периода Тан и перебрасывают триггер 22 в единичное состояние, тем самым открывая счетный вход счетчика 19 и т.д. Одновременно сигнал с выхода логического элемента И 18 подается на вход логического элемента И 23, на другой вход которого поступает сигнал синхронизации (см. фиг,2.1,б). Выходной сигнал с логического элемента И 23 представлен на фиг.2.1,п.

Сигнал с выходов триггеров 8 каждого информационного канала (см, фиг.2,1,и) приходит на информационные входы мультиплексора 24 (например, микросхему 533 КП15) и коммутатора 10. Данный сигнал свидетельствует о том, что имеются или отсутствуют единицы в анализируемом слове (если имеются, то выходной сигнал с триггера 8 - 1, отсутствуют - О). (ги-1) вход мультиплексора 24 является входом дополнительного канала и заземлен. Мультиплексор 24 последовательно опрашивает все (п+1) каналы, выходной сигнал его см. фиг.2.2,р, (масштаб эпюр увеличен для наглядности за счет увеличения масштаба периода Тан). Опросность осуществляется сменой адресов (см. фиг.2.2,м), подаваемых на адресные входы мультиплексора 24 с ахо- дов счетчика 19. Синфазное частотой смены адресов мультиплексора 24 на С-вход счетчика 25, выполненного, например, на микросхеме 533 ИЕ15, подается сигнал с триггера 17 (см. фиг.2.2,л). На вход Е - запись счетчика 25 подается сигнал с выхода формирователя 13, который записывает в счетчик 1. Это означает, что при опросе мультиплексором 24 первого канала на выходах счетчика 25 устанавливается код 0001, при опросе второго канала - 0010 и т.д. (см. фиг.2.2,с). Параллельный код с выходов счетчика 24 поступает на информационные входы регистров 26 и 27 (например, на микросхемы

155 ИР13). Сигнал с выхода мультилексора 24 через логический элемент И 31 (см. фиг.2.2,т), на вход которого также поступает сигнал с триггера 17, приходит на С-вход триггера 28 (например, микросхему 530 ТМ2), с выходов которого (см, фиг.2.2,у) сигналы через логические элементы И 32 и 33 соответственно поступают на входы S1, SO регистров 26 и 27 (см. фиг.2.2, х,ч), при этом на другие входы логических элементов И 32 и 33 подается сигнал с мультиплексора 24 (см. фиг.2.2,р).

Регистры 26 и 27 работают следующим образом.

В начальный момент времени коммутатор 10 обнуляется импульсами, приходящими с формирователя 13 (см. фиг.2.1,г), поступающими на обнуляющие входы Р регистров 26 и 27, триггера 28 и блока регистров 37. Как только на выходе мультиплексора 24 появится первая 1, что говорит о том, что в анализируемом слове данного канала нет единиц, с выходов регистра 26 считывается информация, записанная в данный регистр. Так как он был обнулен, то будет считываться код 00000000, который поступает через ключ 29 и/или 34 на входы блока дешифраторов 35, выполненного, например, на микросхемах 533 ЛАЗ, в котором срабатывает дешифратор, соответствующий дополнительному каналу. На выходе его появляется 1, которая подается на выходы S1 и SO выбора режима регистра, соответствующего дополнительному каналу блока регистров 37, выполненному, например, на микросхемах 155 ИР13, через блок формирователей 36, т.е. данный регистр переводится в режим записи. Одновременно на информационные входы блока регистров 37 поступает код со счетчика 25, соответствующий номеру своего канала, в слове которого отсутствуют единицы. Для нормальной работы блока регистров 37 предназначен блок формирователей 36. На его входы поступают сигналы с выхода триггера 22 (см. фиг.2.1,н), а также сигнал с выходов блока дешифраторов 35. Принцип работы этого формирователя заключается в том, что за все время опроса мультиплексора с 1 по (п+1) канал блок регистров 37 находится в режиме Записи, а остальное время - в режиме Сдвига. На тактовый вход С блока регистров 37 подается сигнал с выхода логического элемента ИЛИ 23 (см, фиг.2.1,п).

Одновременно со считыванием информации из регистра 26 в регистр 27 запишется код канала, в слове которого отсутствуют единицы. При обнаружении следующего канала, в слове которого отсутствуют единицы, на выходе мультиплексора 24 появится импульс, который перекинет триггер 28 в противоположное состояние и считывание записанной информации будет уже из регистра 27, а запись будет производиться в регистр 26, работа остальных элементов схемы останется без изменения. В результате чего код первого обнаруженного канала, в слове которого отсутствуют единицы,

0 запишется в регистр дополнительного канала блока регистров 37, в номер последующего канала, в анализируемых словах которого также не окажется единиц, запишется в регистр предыдущего канала блока регистров

5 37, где отсутствуют единицы и т.д. Код дополнительного канала записывается в регистр последнего канала, в слове которого отсутствуют единицы.

После того, как мультиплексором 24 бу0 дут опрошены все (п+1) каналов, регистры блока регистров 37 будут переведены в режим Сдвига путем пода чи на входы S1, SO Выбора режима соответствующих потенциалов. С приходом на вход С регистров

5 блока регистров 37 тактовых импульсов с выхода логического элемента ИЛИ 23 (см. фиг,2.1,п) записанная информация по всем п каналам (в данном случае п 4) одновременно в последовательном коде будет пода0 ваться на третий вход логических элементов ИЛИ 9 своего канала, где будет суммироваться с входной информацией (см. фиг.2.1,к).

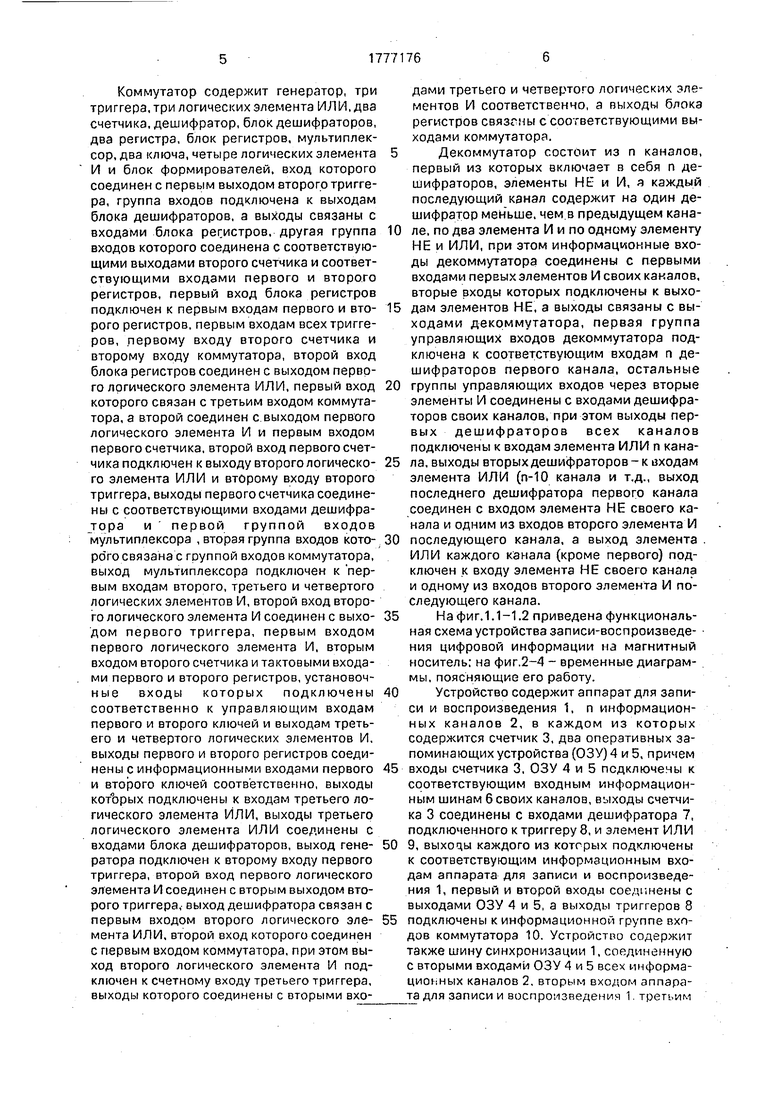

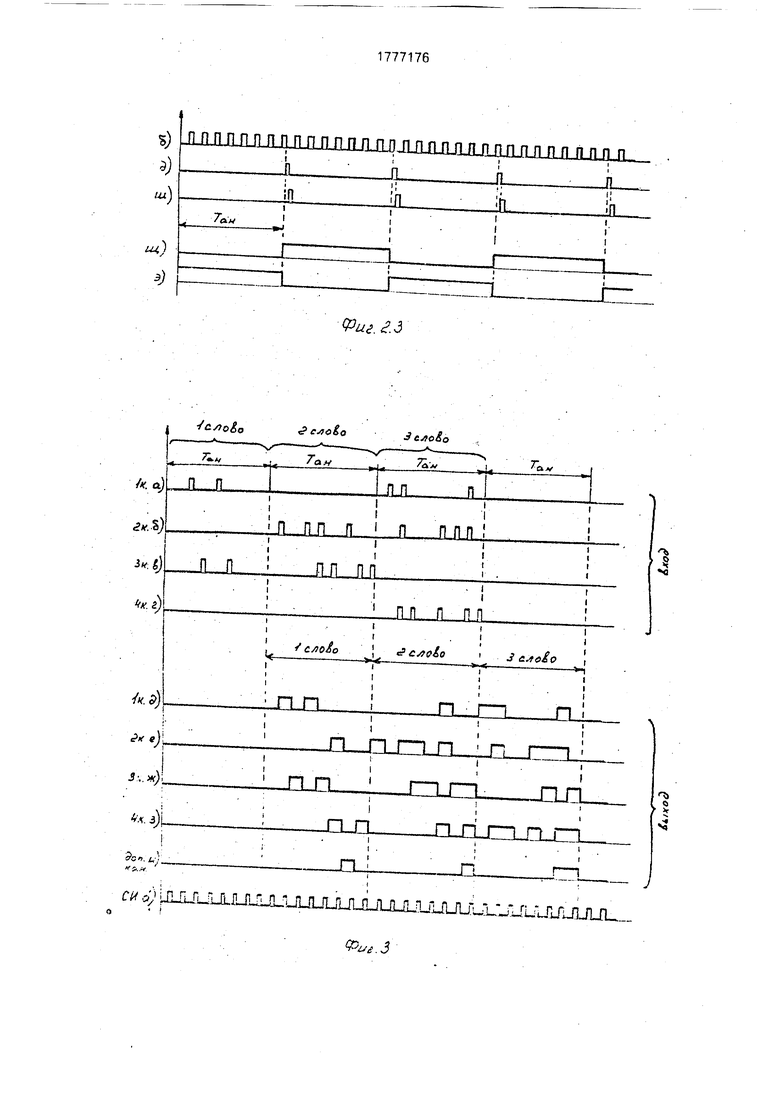

Для наглядности условно зададим; п

5 4, в каждом канале три восьмиразрядных слова, период повторения слов Тан. На фиг.З.а показан входной информационный сигнал по первому каналу, в первом и третьем словах которого имеются единицы, а во

0 втором они отсутствуют. На фиг.3,6, в, г

представлены информационные сигналы

для второго, третьего и четвертого каналов.

На фиг.З.д, е, ж, з показаны выходы с

логических элементов ИЛИ 9 для первого,

5 второго, третьего и четвертого каналов соответственно, а на фиг.З.и показан выход с регистра дополнительного канала блока регистров 37. Таким образом информация на выходе логических элементов ИЛИ 9 каждо0 го из п каналов и информация по дополнительному каналу на выходе регистра дополнительного канала блока регистров 37 сдвинута на Тан относительно входной информации.

5 Рассмотрим первые слова всех четырех каналов. В словах первого и третьего каналов имеются 1 (см. фиг.З.а,в). Следовательно, она проходит на выход со сдвигом на Тан (см. фиг.З.д.ж) (информация показана в коде БВН).

Во втором канале в первом слове отсутствуют единицы. Следовательно, в первом слове дополнительного канала запишется код второго канала два (см. фиг.З.и) и тоже со сдвигом на Тан, т.е. номер первого обна- руженного канала, в слове которого отсутствуют единицы. В слове второго канала (см. фиг.3,е) запишется номер четвертого канала четыре (т.е. следующего канала, где отсутствуют единицы), а в слове четвертого кана- ла (см. фиг.З.з) запишется код дополнительного канала, т.е. пять (т.к. в первом слове четвертого канала нет единиц и оно является последним).

Рассмотрим второе слово каждого из информационных каналов.

В словах второго и третьего каналов имеются единицы (см. фиг.З.б.в). Следовательно, информация по этим каналам проходит на выход со сдвигом на Тан (см. фиг.З.е.ж) (в коде БВН). В слове дополнительного канала (см. фиг.З.и) запишется код первого канала, т.е. единица, в слове второго канала - код четвертого канала четыре, а в слове четвертого канала (см. фиг.4,з) запишется код дополнительного канала пять.

Рассмотрим третье слово каждого из информационных каналов.

В словах первого, второго и четвертого каналов имеются единицы (см. фиг.3,а,б,г). Информация по этим каналам проходит на выход со сдвигом на Тан (см. фиг.3,д,е,з) (в коде БВН). В слове дополнительного канала (см. фиг.З.и) запишется код третьего канала три, а в слове третьего канала - код дополнительного канала пять.

Далее вся информация с выходов логических элементов ИЛИ 9 каждого канала пишется на магнитную ленту аппарата для записи и воспроизведения 1 (АЭВ) по своим дорожкам. Информация по дополнительному каналу записывается по своей дорожке с выхода регистра дополнительного канала блока регистров 37. Также записываются по своим дорожкам СИ и маркер.

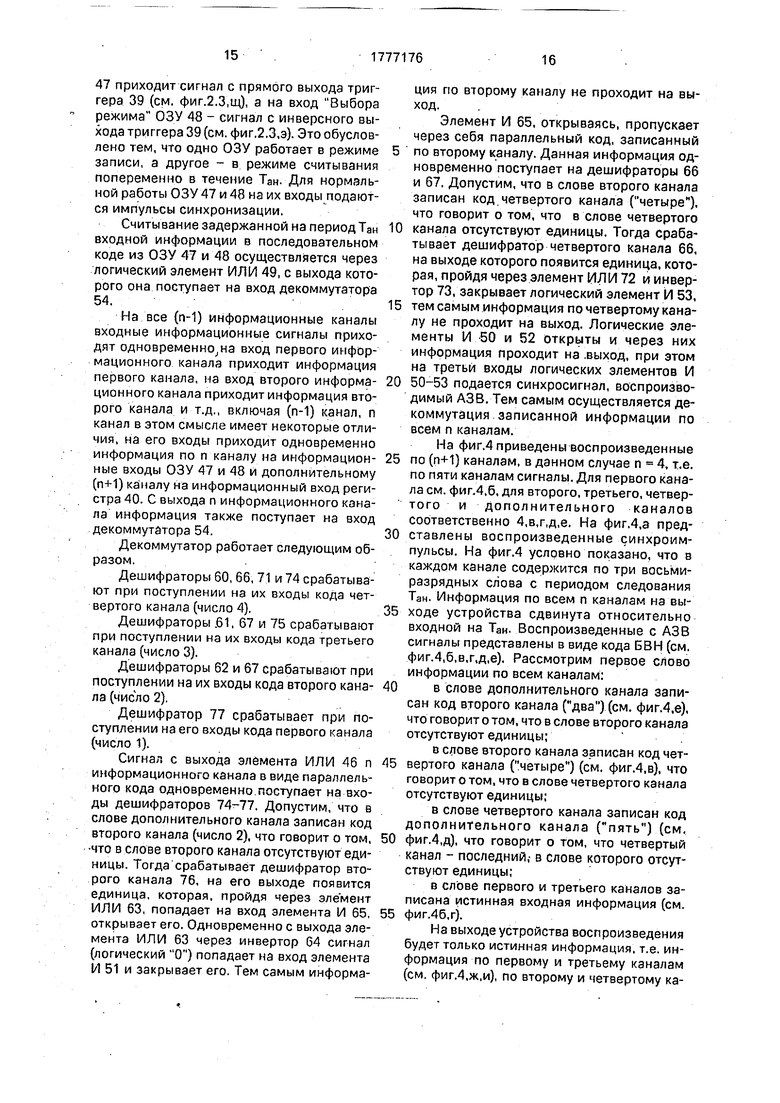

В воспроизводящей части устройства сигнал с выхода АЗВ (маркер) (см. фиг.2.1,г, 2.3,д) поступает на вход триггера 39 (например, микросхему 530 ТМ2), сигна- лы с выхода его представлены на фиг,2,3,щ,з,и поступают на входе формирователя 38 (например, на микросхему 533 АГЗ), где формируется по заднему фронту входного сигнала короткий импульс (см. фиг,2.3,ш).

Для анализа входного информационного сигнала с последующей его декоммута- цией предназначены п информационных каналов 41.

Входной информационный сигнал поступает на информационный вход регистра 30 своего канала 41 (например, на микросхему 533 ИР8), на обнуляющий вход которого поступает сигнал с выхода формирователя 38 (см. фиг.2.3,ш), а на тактовый вход поступает СИ с выхода АЗВ (см. фиг.2,1 ,б, 2.3,6).

Регистр 40 преобразовывает восьмиразрядный последовательный код в параллельный восьмиразрядный код. Параллельный восьмиразрядный код поступает на информационные входы регистров

42и 43 (например, на микросхемы 533 ИР27), которые находятся в режиме записи. На тактовый вход регистра 42 подается сигнал с прямого выхода триггера 39 (см. фиг.2.3.щ), а на тактовый вход регистра 43 подается сигнал с инверсного выхода триггера 39 (см. фиг.2.3,э), причем данные сигналы опережают импульсы обнуления на величину длительности импульса, выраба- тываемого на выходе формирователя импульсов 13. Запись в данные регистры 42 и

43производится по переднему фронту импульсов, поступающих на тактовый вход, поэтому информация сначала перепишется из регистра 40 в один из регистров 42 или 43, а затем происходит обнуление регистра 40, причем запись информации на регистры 42 и 43 будет производиться в противофазе через период Тан. Сигнал с выходов регистров 42 и 43 поступает на логические элементы И 44 и 45, при этом управляющий сигнал на логический элемент И 44 поступает с прямого выхода триггера 39 (см. фиг.2.3,щ), а на элемент И 45 - С инверсного выхода (фиг.2.3,э). Следовательно, записанная информация в регистр 42 будет проходить через логический элемент И 44 весь период Тан, весь следующий период Тан будет проходить информация, записанная в регистр 43. и т.д.

Сигнал с выходов 44 и 45 поступает на логический элемент ИЛИ 46 (например, на микросхему 533 ЛЛ1), с выходов которого в параллельном восьмиразрядном коде он поступает на вход декоммутатора.

Для задержки информации по п информационным каналам на время периода Тан использована цепочка задержки, состоящая из запоминающих устройств ОЗУ 47 и 48 и логического элемента ИЛИ 49, выполненного, например, на микросхеме 533 ЛЛ1.

Рассмотрим работу одного из информационных каналов.

Информация поступает на информационные входы ОЗУ 47 и 48, на входы Выбора режима которых приходят импульсы подсвета (см. фиг.2.3,щ,э), с ВЫХОДОР триггера 39. Причем на вход Выбора режима ОЗУ

47 приходит сигнал с прямого выхода триггера 39 (см. фиг.2.3,щ), а на вход Выбора режима ОЗУ 48 - сигнал с инверсного выхода триггера 39 (см. фиг.2.3,э). Это обусловлено тем, что одно ОЗУ работает в режиме записи, а другое - в режиме считывания попеременно в течение Тан. Для нормальной работы ОЗУ 47 и 48 на их входы подаются импульсы синхронизации.

Считывание задержанной на период Тан входной информации в последовательном коде из ОЗУ 47 и 48 осуществляется через логический элемент ИЛИ 49, с выхода которого она поступает на вход декоммутатора 54.

На все (п-1) информационные каналы входные информационные сигналы приходят одновременно, на вход первого информационного канала приходит информация первого канала, на вход второго информационного канала приходит информация второго канала и т.д., включая (п-1) канал, п канал в этом смысле имеет некоторые отличия, на его входы приходит одновременно информация по п каналу на информационные входы ОЗУ 47 и 48 и дополнительному (п+1) каналу на информационный вход регистра 40. С выхода п информационного канала информация также поступает на вход декоммутатора 54.

Декоммутатор работает следующим образом.

Дешифраторы 60, 66, 71 и 74 срабатывают при поступлении на их входы кода четвертого канала (число 4).

Дешифраторы .61, 67 и 75 срабатывают при поступлении на их входы кода третьего канала (число 3).

Дешифраторы 62 и 67 срабатывают при поступлении на их входы кода второго канала (число 2).

Дешифратор 77 срабатывает при поступлении на его входы кода первого канала (число 1).

Сигнал с выхода элемента ИЛИ 46 п информационного канала в виде параллельного кода одновременно поступает на входы дешифраторов 74-77. Допустим, что в слове дополнительного канала записан код второго канала (число 2), что говорит о том, что в слове второго канала отсутствуют единицы. Тогда срабатывает дешифратор второго канала 76, на его выходе появится единица, которая, пройдя через эле мент ИЛИ 63, попадает на вход элемента И 65, открывает его. Одновременно с выхода элемента ИЛИ 63 через инвертор 64 сигнал (логический О) попадает на вход элемента И 51 и закрывает его. Тем самым информация по второму каналу не проходит на выход.

Элемент И 65, открываясь, пропускает через себя параллельный код, записанный

по второму каналу. Данная информация одновременно поступает на дешифраторы 66 и 67. Допустим, что в слове второго канала записан код четвертого канала (четыре), что говорит о том, что в слове четвертого

канала отсутствуют единицы. Тогда срабатывает дешифратор четвертого канала 66, на выходе которого появится единица, которая, пройдя через элемент ИЛИ 72 и инвертор 73, закрывает логический элемент И 53,

тем самым информация по четвертому каналу не проходит на выход. Логические элементы И 50 и 52 открыты и через них информация проходит на .выход, при этом на третьи входы логических элементов И

50-53 подается синхросигнал, воспроизводимый A3 В. Тем самым осуществляется де- коммутация записанной информации по всем п каналам.

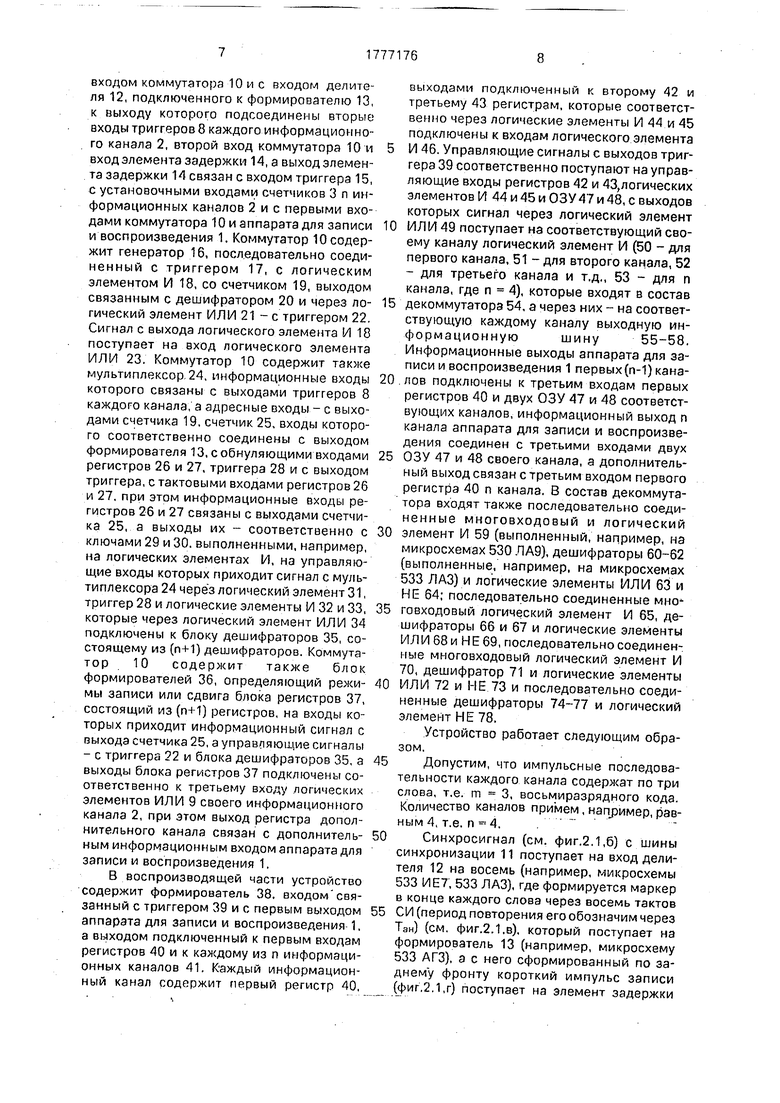

На фиг.4 приведены воспроизведенные

по (п+1) каналам, в данном случае п 4, т.е. по пяти каналам сигналы. Для первого канала см. фиг.4.б, для второго, третьего, четвертого и дополнительного каналов соответственно 4,в,г,д,е. На фиг,4,а представлены воспроизведенные синхроимпульсы. На фиг.4 условно показано, что в каждом канале содержится по три восьмиразрядных слова с периодом следования Тан. Информация по всем п каналам на выходе устройства сдвинута относительно входной на Тан. Воспроизведенные с АЗВ сигналы представлены в виде кода БВН (см. фиг.4,б,в,г,д,е). Рассмотрим первое слово информации по всем каналам:

в слове дополнительного канала записан код второго канала (два) (см. фиг.4,е), что говорит о том, что в слове второго канала отсутствуют единицы;

в слове второго канала записан код четвертого канала (четыре) (см. фиг.4,в), что говорит о том, что в слове четвертого канала отсутствуют единицы;

в слове четвертого канала записан код дополнительного канала (пять) (см.

0 фиг.4,д), что говорит о том, что четвертый канал - последний,- в слове которого отсутствуют единицы;

в слове первого и третьего каналов записана истинная входная информация (см.

5 фиг.4б,г).

На выходе устройства воспроизведения будет только истинная информация, т.е. информация по первому и третьему каналам (см. фиг.4.ж,и), по второму и четвертому каналам информационный сигнал будет отсутствовать, т.е. там будут нули (фигАз.к).

Выходной кадр устройства записи-воспроизведения (см. фиг.4,ж,з,и,к) будет аналогичен входному кадру, подаваемому на входы устройства записи-воспроизведения (см. фиг.3,а,б,в,г).

На предприятии было проведено лабораторное макетирование и зксперименталь- ные исследования предложенного устройства записи-воспроизведения многоканальной цифровой информации на магнитный носитель.

Полученные результаты подтвердили работоспособность устройства и показали, что по сравнению с прототипом за счет повышения помехоустойчивости и улучшения свойств самосинхронизации записываемых сигналов по каждому каналу достоверность восстановления цифровой информации воз- .растает в 5-7 раз.

Формула изобретения

1. Устройство запи си-воспроизведения многоканальной цифровой информации на магнитный носитель, содержащее в записывающей части входные информационные шины, шину синхронизации, соединенную с входом делителя, формирователь и п информационных каналов, в каждом из которых содержится счетчик, а в воспроизводящей части - п информационных каналов, каждый из которых включает регистр, первое оперативное запоминающее устройство, два элемента И, выходы которых соединены с входами элемента ИЛИ, и аппарат для записи и воспроизведения, отличающееся тем, что, с целью повышения помехоустойчивости путем улучшения свойств синхронизации каждого канала, в записывающую часть введены коммутатор, элемент задержки, триггер, вход которого соединен с выходом элемента задержки, с установочными входами счетчиков п каналов и первыми входами коммутатора и аппарата для записи и воспроизведения, а в каждый канал введены два оперативных запоминающих устройства, дешифратор, триггер и элемент ИЛИ. выходы каждого из которых подключены к соответствующим информационным входам аппарата для записи и воспроизведения, первый и второй входы соединены с выходами оперативного запоминающего устройства, выходы триггеров подключены к информационной группе входов коммутатора, первые входы соединены с выходами дешифраторов, а вторые входы триггеров каждого канала связаны между собой, с вторым входом коммутатора, с выходом формирователя и входом элемента задержки, входы дешифраторов соединены с соответствующими выходами счетчиков, 5 входные информационные шины подключены к первым входам оперативного запоминающего устройства и счетчика своих каналов, шина синхронизации связана с вторыми входами оперативных запоминаю- 10 щих устройств всех каналов, вторым входом аппарата для записи и воспроизведения и третьими входом коммутатора, при этом первый выход триггера подключен к управляющим входам первых оперативных запо- 15 минающих устройств всех каналов, а второй выход - к управляющим входам вторых оперативных запоминающих устройств, выход делителя связан с входом формирователя, первый выход коммутатора соединен с до20 полнительным информационным входом аппарата для записи и воспроизведения, а остальные выходы соединены с третьими входами элементов ИЛИ соответствующих каналов, в воспроизводящую часть введены

25 формирователь, триггер, декоммутатор, а в каждый канал - второе оперативное запоминающее устройство, второй и третий регистры и второй элемент ИЛИ, входы которого соединены с выходами оператив0 ных запоминающих устройств, а выходы - с соответствующими информационными входами декоммутатора, выходы первого элемента ИЛИ каждого канала подключены к соответствующим группам управляющих

5 входов декоммутатора, первые входы первых оперативных запоминающих устройств всех каналов соединены между собой и подключены к первым входам второго регистра, первого элемента И своих каналов и к лер0 вому выходу триггера, первые входы вторых оперативных запоминающих устройств всех каналов соединены между собой и подключены к первым входам третьего регистра и второго элемента И своих каналов и второму

5 выходу триггера, выход формирователя соединен с первыми входами первых регистров всех каналов, а его вход связан с входом триггера и первым выходом- ппарата для записи и воспроизведения, второй выход

0 аппарата для записи и воспроизведения подключен к вторым входам первых регистров и вторым входам обоих оперативных запоминающих устройств всех каналов и выходной шине синхронизации, информа5 ционные выходы аппарата для записи и вос- произведения первых (п-1)-х каналов подключены к третьим входам первых регистров и двух оперативных запоминающих устройств соответствующих каналов, информационный выход последнего канала

аппарата для записи и воспроизведения соединен с третьими входами двух оператив- иых запоминающих устройств своего канала, а дополнительный информационный выход связан с третьим входом первого регистра п канала, при этом в каждом канале выходы первого регистра соединены с соответствующими входами второго и третьего регистров, выходы второго и третьего регистров подключены к входам первого и второго логических элементов И, а выходы декоммутатора связаны с выходными информационными шинами.

2. Устройство поп.1,отличающее- с я тем, что коммутатор содержит генератор, три триггера, три элемента ИЛИ, два счетчика, дешифратор, блок дешифраторов, два регистра, блок регистров, мультиплексор, два ключа, четыре элемента И и блок формирователей, вход которого соединен с первым выходом второго триггера, группа входов подключена к выходам блока дешифраторов, а выходы связаны с входами блока регистров, другая группа входов которого соединена с соответствующими выходами второго счетчика и соответствующими входами первого и второго регистров, первый вход блока регистров подключен к первым входам первого и второго регистров, первым входам всех триггеров, первому входу второго счетчика и второму входу коммутатора, второй вход блока регистров соединен с выходом первого элемента ИЛИ, первый вход которого связан с третьим входом коммутатора, а второй - соединен с выходом первого элемента И и первым входом первого счетчика, второй вход первого счетчика подключен к выходу второго элемента ИЛИ и второму входу второго триггера, выходы первого счетчика соединены с соответствующими входами дешифратора и первой группой входов мультиплексора, вторая группа входов которого связана с группой входов коммутатора, выход мультиплексора подключен к первым входам второго, третьего и четвертого элементов И, второй вход второго элемента И соединен с выходом первого триггера, первым входом первого элемента И, вторым входом второго счетчика и тактовыми входами первого и второго регистров, установочные входы которых подключены соответственно к управляющим входам первого и второго ключей и выходам третьего и четвертого элементов И, выходы первого и второго регистров соединены с информационными входами первого

и второго ключей соответственно, выходы которых подключены к входам третьего элемента ИЛИ, выходы третьего элемента ИЛИ соединены с входами блока дешифраторов, выход генератора подключен к второму вхо0 ду первого триггера, второй вход первого элемента И соединен с вторым выходом второго триггера, выход дешифратора связан с первым входом второго элемента ИЛИ, второй вход которого соединен с первым вхо5 дом коммутатора, при этом выход второго элемента И подключен к счетному входу третьего триггера, выходы которого соединены с вторыми входами третьего и четвертого элементов И соответственно, а выходы

0 блока регистров связан с соответствующими выходами коммутатора.

3. Устройство поп.1,отличающее- с я тем, что декоммутатор состоит из п каналов, первый из которых включает в себя п

5 дешифраторов, элементы НЕ и И, а каждый последующий канал содержит на один дешифратор меньше, чем в предыдущем канале, по два элемента И и по одному элементу НЕ и ИЛИ, при этом информационные вхоQ ды декоммутатора соединены с первыми входами первых элементов И своихканалов, вторые входы которых подключены к выходам элементов НЕ, а выходы связаны с выходами декоммутатора, первая группа управляющих входов декоммутатора под5 ключена к соответствующим входам п дешифраторов первого канала, остальные группы управляющих входов через вторые элементы И соединены с входами дешифраторов своих каналов, при этом выходы пер0 вых дешифраторов всех каналов подключены к входам элемента ИЛИ п канала, выходы вторых дешифраторов-к входам элемента ИЛИ (п-1)-го канала, выход последнего дешифратора первого канала сое5 динен с входом элемента НЕ своего канала и одним из входов второго элемента И последующего канала, а выход элемента ИЛИ каждого канала, кроме первого, подключен к входу элемента НЕ своего канала и одному

Q из входов второго элемента И последующего канала,

to rr- r- t-

$W/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для ввода информации | 1979 |

|

SU855649A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство оперативной связи с управляющими программами | 1981 |

|

SU970351A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для воспроизведения информации с магнитного носителя | 1981 |

|

SU1014017A1 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

Использование: точная магнитная запись цифровой информации, а также смежная с ней отрасль народного хозяйства - приборостроение. Устройство позволило повысить помехоустойчивость за счет улучшения свойств синхронизации каждого канала. Устройство содержит аппарат для записи и воспроизведения, п информационных каналов, каждый из которых содержит датчик, два ОЗУ, дешифратор, триггер и элемент ИЛИ, коммутатор, содержащий генератор, три триггера, шесть элементов И, два счетчика, три элемента ИЛИ, дешифратор, два регистра, блок дешифраторов, блок 36 формирователей и блок регистров, делитель, формирователь, элемент задержки, триггер. В воспроизводящей части устройство содержит формирователь 38, триггер, п информационных каналов, каждый из которых состоит из трех регистров, двух ОЗУ, двух элементов И и двух элементов ИЛИ, декоммутатор, состоящий из п каналов, первый из которых содержит п дешифраторов, элементы НЕ и И, а каждый последующий - на один дешифратор меньше, чем предыдущий, т.е. во втором канале - три в третьем - два. в четвертом - один, по два элемента И и по одному элементу НЕ и И Л И, Устройство позволило повысить достоверность восстановленной информации в 5-7 раз. 2 з.п. ф-лы. 4 ил. сл с

ГП ГП ГП ГП .n

,e&2

ZL

JL

СИ о) LOIuJlJLLO lЈJJU

Фш 3

Фм.4

| Авторское свидетельство СССР № 1507092,кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ записи и воспроизведения цифровой информации и устройство для его осуществления | 1986 |

|

SU1422241A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-11-23—Публикация

1991-02-25—Подача