« . Изобретение относится к вычислительной технике, в частности к запоминающим устройствам(ЗУ) , выполненным на полупроводниковых динамических элементах. Известны ЗУ, содержащие полупроводниковые динамические блоки памяти схему контроля, регистр адресаj счетчик5дешифраторы и генератор ГН Недостатком устройства является отсутствие исправления,ошибок, возникающих при хранении информации в памяти, и, вследствие этого, высокая надежность работы устройства. Наиболее близким к изобретению является динамическое ЗУ с самоконтролем, содержащее накопители на полу проводник овых динамических элементах памяти, информационные входы и выходы которых через регистр числа соединены с числовыми шинами и входом блока контроля, входы выборки накопителей соединены свыходами дешифратора, входы которого через дополнительный селектор связаны с выходами дополнительного счетчика и одними выходами регистра адреса, входы обра щения - регенерации через основной селектор - с выходами основного счетчика и другими выходами регистра адреса, входы которого соединены с адресными шинам -, тактовый генератор, первые выходы которого соединены со стробирующим входом дешифратора и входом дешифратора и входом режима накопителей, вторые - с управ ляющими входами основного и дополнительного селекторов, и счетным входом основного счетчика, а вход такто вого генератора соединен с входной управляюа1,ей шиной, счетный вход дополнительного счетчика соединен с выходом переноса основного счетчика 2 . , Однако в известном устройстве происходит лишь обнаружение самого факта появления ошибок, возникающих в процессе работы и не предусмотрено исправление ошибок аппаратным спосо бом. Цель изобретения - повышение надежности устройства путем совмещения регенерации информации, которая в памяти динамического типа производится непрерывно, со считыванием., контролем и исправлением информации Поставленная цель достигается тем, что в динамическое запоминающее устройство с коррекцией ошибок, со252держащее накопитель, регистр адреса, счетчик, дешифратор, первый коммутатор, одни выходы которого соединены с первым входом накопителя, другие с входом дешифратора,, выход которого подключен к второму входу накопителя, первый вход первого коммутатора соединен с выходом регистра адреса, вход которого является адресным входом устройства, выход счетчика соединен с вторым входом первого коммутатора, введены формирователь корректирующих сигналов, регистр регенерации, второй ком1-{утатор, блок коррекции, блок управления, причем первый вход второго коммутатора соединен с выходом формирователя корpeктиJ yющиx сигналов, вход которого является информационным входом устройства, выход регистра регенерации соединен с вторыг- входом второго коммутатора, выход которого подключен к третьему входу накопителя, выход которого соединен с входом блока коррекции, один выход которого подключен к входу регистра регенерации и является информационным выходом устройства, а другой выход к одному входу блока управления. первый и второй выходы которого соединены с третьи}.- и четвертым входами накопителя, третий выход блока управления подключен к входу счетчика и третьим входам коммутаторов друт--ие входы блока управления являются управляющшчи входами устройства. Причем блок управления содержит регистр сдвига, элементы И элементы ИЛИ, триггер, первый выход регистра сдвига соединен с вторыми входами триггера, первого н третьего элементов И и является третьим выходом блока управления, второй вых,од регистра сдвига соединен с первым входом второго элемента ИЛИ, третий выход регистра сдвига -соединен с первым входом второго элемента И, второй вход, которого под слючен к выходу триггера, выход первого элемента И соединен с первым входом первого злемента ИЛИ, второй вход которого подключен к выходу второго элемента И к второму в-ходу второго элемента ИЛИ третий вход которого соединен с выходом третьего элемента И, выходы первого и второго элементов ИЛИ являются соответственно пер вым к вторым выходами блока управле311

ия, третий вход первого элемента И оединен с первым входом третьего лемента И и вторым входом регистра двига, первый вход триггера, первый ход регистра сдвига, первый и третий входы первого элемента И являютя входами блока управления.

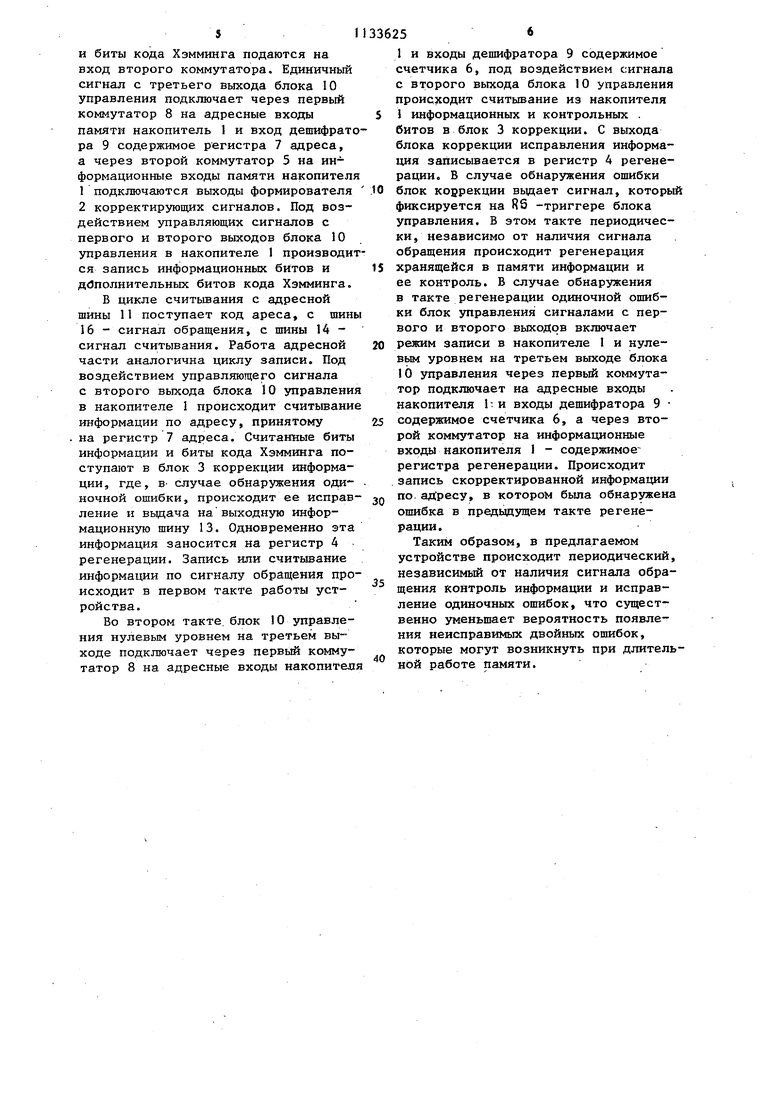

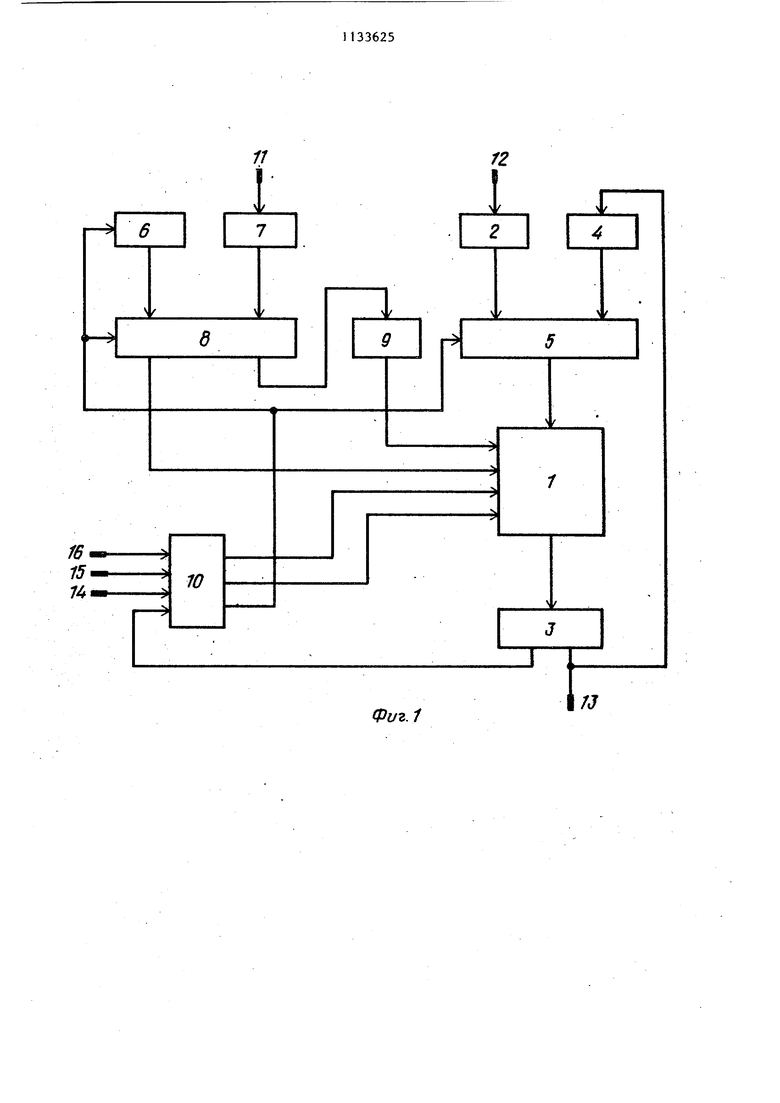

На фиг, 1 приведена структурная схема устройства; на фиг. 2 - скема лока управления.

Запоминающее устройство содержит акопитель 1 на полупроводниковых элементах памяти 1, формирователь 2 корректирующих сигналов, блок3 коррекции, регистр 4 регенерации, второй коммутатор 5, счетчик 6, регистр 7 адреса, первый коммутатор 8, дешифратор 9, блок 10 управления.

Блок 10 управления содержит регистр 10.1 сдвига, три элемента И 10.2 - 10.4J два элемента ИЛИ 10.5 и 10.6, R5 -триггер 10.7.

Вход 11 являетвя адресным входом уст|войства, входы 12 и 13 информационными входами и выходами устройства , входы 14 - 16 - управляющими входами устройства.

Устройство работает следующим образом.

По шине 15 на второй вход блока управления поступает синхронизирующая серия. Сигнал обращения к памяти поступает по шине 16 на первый вход узла управления и совпадает по времени с импульсами синхронизирующей серии. Частота синхросерии в три раза больше частоты сигналов обращения. При поступлении по шине 16 сигнала обращения на первом выходе регистра 10.1 устанавливается единич ный уровень, а на втором и третьем нулевые. Если по шине 14 в это время подается единичный уровень (сигнал Запись), то открываются элементы И 10.2 и 10..4, и на выходах элементов ИЛИ 10,5 и появляются единичные уровни, под воздействием которых-в накопителе производится запись информации. Если при наличии сигнала обра1цения по шине 14 подается нулевой уровень, то открывается только элемент И 10,4 и единичный уровень появляется только на выходе элемента ИЛИ 10, воздействием которого в накопителе происходит считывание информации.

По второму синхроимпульсу единичный уровень переписывается на втррой выход регистра 10,1 и через

36254

элемент ИЛИ 10.6 подается в накопитель , где вызывает считывание информации. В этом такте происходит регенерация, считывание и контроль

5 информации. В случае обнаружения ошибки в этом такте управляющим сигналом, поступающим на S -вход, взводится R5 -триггер 10.7.

Третий синхроимпульс переписьшает

fQ единичный уровень на третий выход регистра, если R5 -триггер находится в единичном состоянии, и появляются единичные уровни на выходах элементов ИЛИ 10.5 и 10,,6. Произво г дится запись в накопитель. Четвертый синхроимпульс/совпадающий с сигналом обращения)устанавливает единичный уровень на первом выходе регистра 10.1.

Таким образом, промежуток времени между сигналами обращения регистром 10.1 делится на три такта. В первом такте при наличии сигнала обращения происходит запись или считывание „ информации, во втором - регенерация и чтение информации для ее контроля, в третьем - запись в память скорректированной информации, если в предыдущем такте обнаружена ошибка. Сигналом первого такта производится сброс RS -триггера 10,7, фиксирующего ошибку в слове, считанном во втором такте, кроме того, единичный уровень этого сигна-ча подключает через первый коммутатор 8 на адресные шины

35 памяти и входы дешифратора выходы регистра адреса, а на информационные входы памяти через второй коммутатор - выходы формирователя корректирующих сигналов. Нулевой уровень

40 этого сигнала подключает на соответствующие входы памяти выходы счетчика и регистра регенерации. Передним фронтом этого сигнала производится добавление единицы к содержимому

45 счетчика.

В цикле записи на информационную шину 12 подается информация, подлежащая записи в память, с адресной шины 11 на регистр 7 адреса поступает код адреса, по шине 16 на вход блока 10 управления поступает сигнал обращения, а по шине 14 - сигнал записи. В формирователе 2 корректирующих сигналов происходит формиро55 ванне дополнительных битов Хэмминга,позволяющих обнаруживать и исправлять одиночные ошибки. С выхода блока 2 информационные биты 5 и биты кода Хэмминга подаются на вход второго коммутатора. Единичный сигнал с третьего выхода блока 10 управления подключает через первый коммутатор 8 на адресные входы памяти накопитель 1 и вход депгафрат ра 9 содержимое регистра 7 адреса, а через второй коммутатор 5 на информационные входы памяти накопител 1подключаются выходы формирователя 2корректирующих сигналов. Под воздействием управляющих сигналов с первого и второго выходов блока 10 управления в накопителе 1 производи ся запись информационных битов и дйполнительных битов кода Хэмминга. В цикле считывания с адресной шины 11 поступает код ареса, с шин 16 - сигнал обращения, с шины 14 сигнал считывания. Работа адресной части аналогична циклу записи. Под воздействием управляющего сигнала с второго выхода блока 10 управлени в накопителе 1 происходит считывани информации по адресу, принятому на регистр 7 адреса. Считанные биты информации и биты кода Хэмминга поступают в блок 3 коррекции информации, где. В случае обнаружения одиночной ошибки, происходит ее исправ ление и вьщача навыходную информационную шину 13. Одновременно эта информация заносится на регистр 4 регенерации. Запись или считывание информации по сигналу обращения про исходит в первом такте работы устройства. Во втором такте, блок 10 управления нулевым уровнем на третьем выходе подключает через первый коммутатор 8 на адресные входы накопител 56 1 и входы дешифратора 9 содержимое счетчика 6, под воздействием сигнала с второго выхода блока 10 управления происходит считывание из накопителя 1 информационных и контрольных . битов в блок 3 коррекции. С выхода блока коррекции исправления информа1ЩЯ записывается в регистр 4 регенерации. В случае обнаружения ошибки блок коррекции вьщает сигнал, который фиксируется на RS -триггере блока управления. В этом такте периодически, независимо от наличия сигнала обращения происходит регенерация хранящейся в памяти информации и ее контроль. В случае обнаружения в такте регенерации одиночной ошибки блок управления сигналами с первого и второго выходов включает режим записи в накопителе 1 и нулевым уровнем на третьем выходе блока 10 управления через первый коммутатор подключает на адресные входы накопителя 1- и входы дешифратора 9 содержимое счетчика 6, а через второй коммутатор на информационные входы накопителя 1 - содержимоерегистра регенерации. Происходит запись скорректированной информации по адресу, в котором бьта обнаружена ошибка в предьщущем такте регенерации . Таким образом, в предлагаемом устройстве происходит периодический, независимый от наличия сигнала обращения контроль информации и исправление одиночных ошибок, что существенно уменьшает вероятность появления неисправимых двойных ошибок, которые могут возникнуть при длительНОЙ работе памяти.

//

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1587600A2 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Запоминающее устройство | 1982 |

|

SU1084903A1 |

1, ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ . УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК, содержащее накопитель, регистр адреса, счетчик, дешифратор, первый коммутатор, одни выходы которого соединены с первым входом накопителя, другие - с входом дешифратора, выходкоторого подключен к второму входу накопителя, первый вход первого коммутатора соединен с выходом регистра адреса, вход которого является адресным входом устройства, выход счетчика соединен с вторым входом первого коммутатора, о т л ич а ю щ е е ,с я тем, что, с целью повьш1ения надежности устройства, в него введены формирователь корректирующих сигналов, регистр регенера-. ции, второй коммутатор, блок коррекции, блок управления, причем первый вход второго коммутатора соединен с выходом формирователя корректирующих сигналов, вход которого является информационным входом устройства, выход регистра регенерации соединен с вторым входом второго коммутатора, выход которого подключен к третьему входу накопителя, выход которого соединен с входом блока коррекции, один вход которого подключен к входу регистра регенерации и является информационным выходом устройства, а другой выход - к одному входу блока управления, первый и второй выходы которого соединены с третьим и четвертым входами накопителя, третий выход блока управления подключен к входу счетчика и третьим входам коммутаторов, другие входы блока управления являются управляющими входами устройства. 2. Устройство по п. 1, о т л ичающееся тем, что блок управления содержит регистр сдвига, элементы И, элементы ИЛИ, триггер, первый выход регистра сдвига соединен с вторыми входами триггера, пер(Л вого и третьего элементов И и является третьим выходом блока управления, второй выход регистра сдвига соединен с первым входом второго элемента ИЛИ, третий выход регистра сдвига соединен с первым входом второго элемента И, второй вход которого соединен с выходом триггера, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу второго элемента И и второму входу второго элемента ИЛИ, третий вход которого соединен с выходом третьего элемента И, выходы первого и второго элементов ИЛИ являются соответственно первым и вторым выходами блока управления, третий вход первого элемента И соединен с первым входом третьего элемента И и вторым входом регистра сдвиг а, первый вход три1ггера,первый вход регистра сдвига,первый и третий входы первого элемента И являются входами блока управления .

16

15

10

74

/J

Фиг. 1

RG

Г0.1

J

ОтЗ

HI

5 W.Z

w.s

L

К1

а

М5,6,в

Ф(/г.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Журнал Data Report, 1976, 11, 11, с | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 760194, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-01-07—Публикация

1983-11-17—Подача