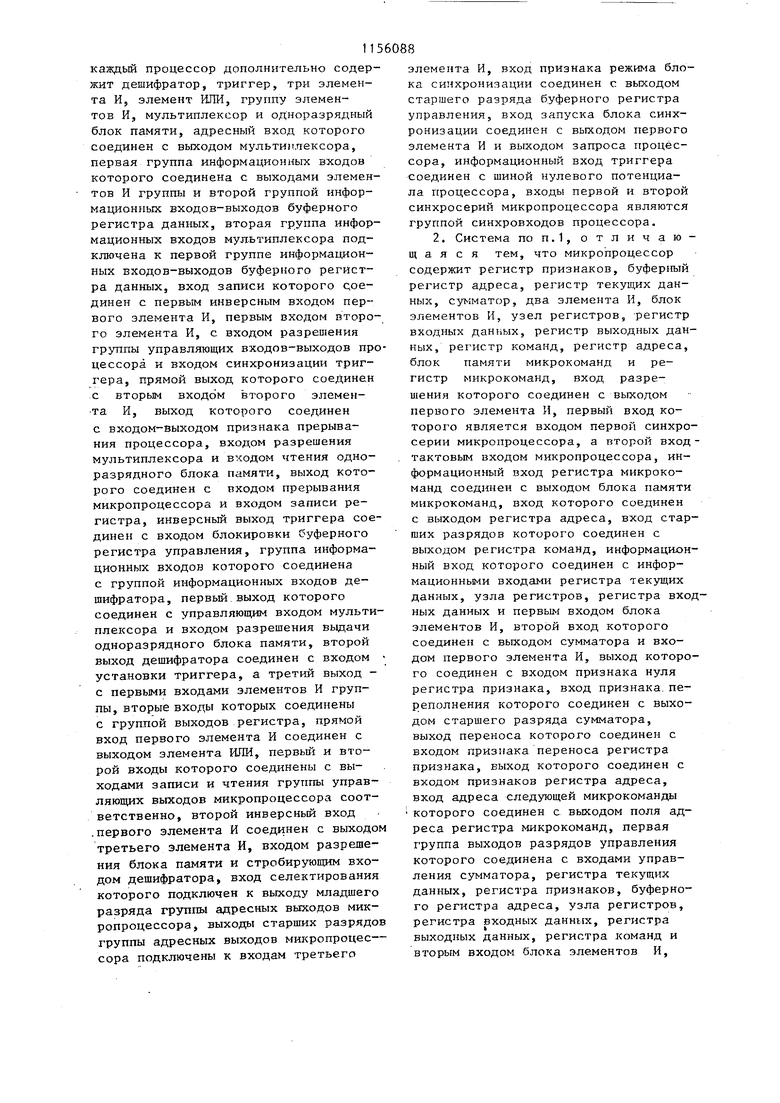

каждый процессор дополнительно содержит дешифратор, триггер, три элемента И, элемент ИЛИ, группу элементов И, мультиплексор и одноразрядный блок памяти, адресный вход которого соединен с выходом мультиплексора, первая группа информационных входов которого соединена с выходами элементов И группы и второй группой информационных входов-выходов буферного регистра данных, вторая группа информационных входов мультиплексора подключена к первой группе информационных входов-выходов буферного регистра данных, вход записи которого соединен с первым инверсным входом первого элемента И, первым входом второго элемента И, с входом разрешения группы управляющих входов-выходов прцессора и входом синхронизации триггера, прямой выход которого соединен с вторым входом второго элемента И, выход которого соединен с входом-выходом признака прерывания процессора, входом разрешения мультиплексора и входом чтения одноразрядного блока памяти, выход которого соединен с входом прерывания микропроцессора и входом записи регистра, инверсный выход триггера соединен с входом блокировки буферного регистра управления, группа информационных входов которого соединена с группой информационных входов дешифратора, первый выход которого соединен с управляющим входом мультиплексора и входом разрешения выдачи одноразрядного блока памяти, второй выход дешифратора соединен с входом установки триггера, а третий выход с первыми входами элементов И группы, вторые входы которых соединены с группой выходов регистра, прямой вход первого элемента И соединен с выходом элемента ИЛИ, первьш и второй входы которого соединены с выходами записи и чтения группы управляющих выходов микропроцессора соответственно, второй инверсный вход .первого элемента И соединен с выходо третьего элемента И, входом разрешения блока памяти и стробирующим входом дешифратора, вход селектирования которого подключен к выходу младшего разряда группы адресных выходов микропроцессора, выходы старших разрядо группы адресных выходов микропроцес- сора подключены к входам третьего

элемента И, вход признака режима блока синхронизации соединен с выходом старшего разряда буферного регистра управления, вход запуска блока синхронизации соединен с выходом первого элемента И и выходом запроса процессора, информационный вход триггера соединен с шиной нулевого потенциала процессора, входы первой и второй синхросерий микропроцессора являются группой синхровходов процессора.

2. Система поп.1, отличающаяся тем, что микропроцессор содержит регистр признаков, буферный регистр адреса, регистр текущих данных, сумматор, два элемента И, блок элементов И, узел регистров, регистр входных данных, регистр выходных данных, регистр команд, регистр адреса, блок памяти микрокоманд и регистр микрокоманд, вход разрешения которого соединен с выходом первого элемента И, первый вход которого является входом первой синхросерий микропроцессора, а второй входтактовым входом микропроцессора, информационный вход регистра микрокоманд соединен с выходом блока памяти микрокоманд, вход которого соединен с выходом регистра адреса, вход старших разрядов которого соединен с выходом регистра команд, информационный вход которого соединен с информационными входами регистра текущих данных, узла регистров, регистра входных данных и первым входом блока элементов И, второй вход которого соединен с выходом сумматора и входом первого элемента И, выход которого соединен с входом признака нуля регистра признака, вход признака, переполнения которого соединен с выходом старшего разряда сумматора, выход переноса которого соединен с входом признака переноса регистра признака, выход которого соединен с входом признаков регистра адреса, вход адреса следующей микрокоманды которого соединен с выходом поля адреса регистра микрокоманд, первая группа выходов разрядов управления которого соединена с входами управления сумматора, регистра текущих данных, регистра признаков, буферного регистра адреса, узла регистров, регистра входных данных, регистра выходных данных, регистра команд и вторым входом блока элементов И,

Btjxo,n y:i.Ti,3 регистроя соединен с входом первого операнда сумматора, ииф(.1рмапночным HXCVUIMH регистр, выходных данных и буферного регистра адреса, выход которого является адресным выходом микропроцессора, пход второй синхросерии которо1 о со дннен с сннхрокходами буферттого регистра адреса, узла регистров, регистра признаков, регистра команд

88

и pei-ruvrpa текущих данных, рыход которого соединен с входом RTopoio операнда сумматора, группа выходов регистра выходных данных соединена с группой входов регистра входных данных и является группой информационных входов-выходов микропроцессора, группа управлянлдих выходов которого соединена с группой выходов признаков регистра микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Многопроцессорная система | 1987 |

|

SU1464168A1 |

| Процессор для мультипроцессорной системы | 1989 |

|

SU1688252A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

1. МУЛЬТИПРОЦЕССОРНАЯ СИСТЕМА, содержащая процессоры, общее запоминающее устройство, коммутатор общих устройств ввода-вывода и блок приоритета, группа выходов разрешения которого подключена к входам разрешения калсдого процессора, выходы запросов которых подключены к группе входов запросов блока приоритета,, адресные выходы каждого процессора подключены к группе адресных входов общего запоминающего устройства и к группе входов управления коммутатора общих устройств ввода-вывода, группа входов стробирования которого подключена к выходам стробирования группы управляю1цих выходов каждого процессора, информационные входы-выходы каждого процессора подключены к группе информационных входов-выходов общего запоминающего устройства и к группе информационных входов-выходов коммутатора общих устройств ввода-вывода, выходы управления памятью rpynnbi управляющих входов-выходов каждого процессора подключены к группе входов управления общего запоминающего устройства, группы синхровходов процессоров объединены между собой и являются входом синхронизации системы, причем каждый процессор содержит микропроцессор, блок синхронизации, регистр, буферные регистры адреса, данных,управления и блок памяти, адресный вход которого соединен с адресным выходом микропроцессора и информационным входом буферного регистра адреса, выход которого является адресным выходом про цессора, входы записи буферного регистра управления, буферного регистра адреса и буферного регистра данных объединены между собой, первая сл группа информационных входов-выходов буферного регистра данных подключена . к информационным входам-выходам процессора и к группе информационных входов регистра, вторая группа инфор- 1мационных входов-выходов буферного регистра данных соединена с группой сд информационных входов блока памяти 0 и группой информационных входов-выо ходов микропроцессора, тактовый вход 00 00 которого соединен с выходом блока синхронизации, группа управляющих выходов микропроцессора соединена с группой информационных входов буферного регистра управления и группой входов упранпення записью блока ти, выходы разрядов буферного регистра управления подключены к группе управляющих входов-выходов процессора, отличающаяся тем, что, с целью повышения производительности, входы-выходы признака прерывания про, цессоров объединены меяоду собой, а

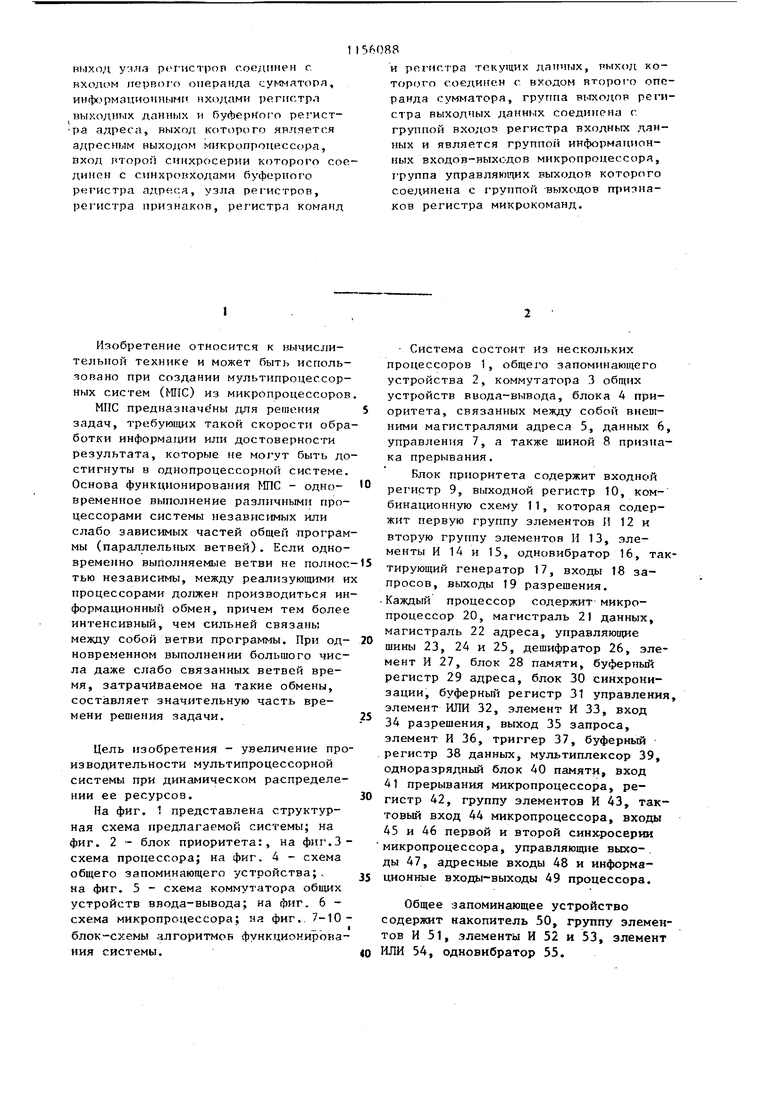

Изобретение откосится к вычислительной технике и может быть использовано при создании мультипроцессорных систем (MIIC) из микропроцессоров

МПС предназпачены цля решения задач, требующих такой скорости обработки информации или достоверности результата, которые не могут быть достигнуты в однопроцессорной системе. Основа функционирования МПС - одновременное выполнение различными процессорами системы независимых или слабо зависимых частей общей -программы (параллельных ветвей). Если одновременно выполняемые ветви не полное тью независимы, между реализующими и процессорами должен производиться информационный обмен, причем тем более интенсивный, чем сильней связаны между собой ветви программы. При одновременном выполнении большого числа даже слабо связанных ветвей время, затрачиваемое на такие обмены, составляет значительную часть времени решения задачи.

Цель изобретения - увеличение производительности мультипроцессорной системы при динамическом распределении ее ресурсов.

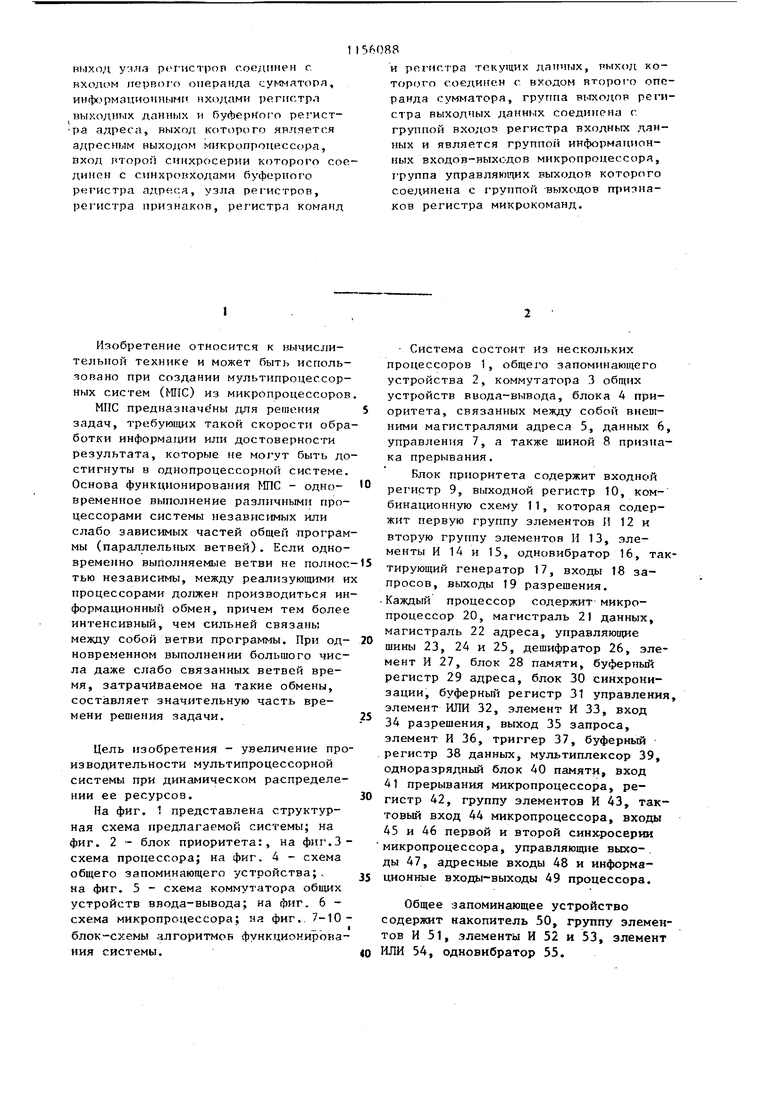

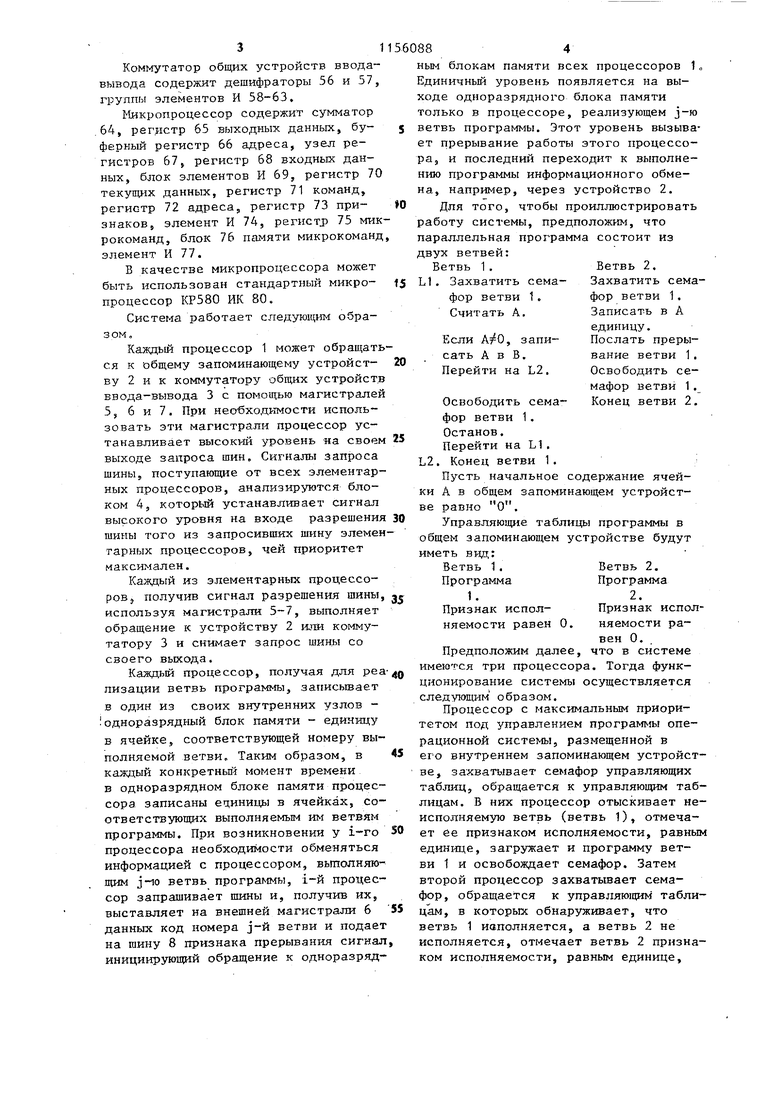

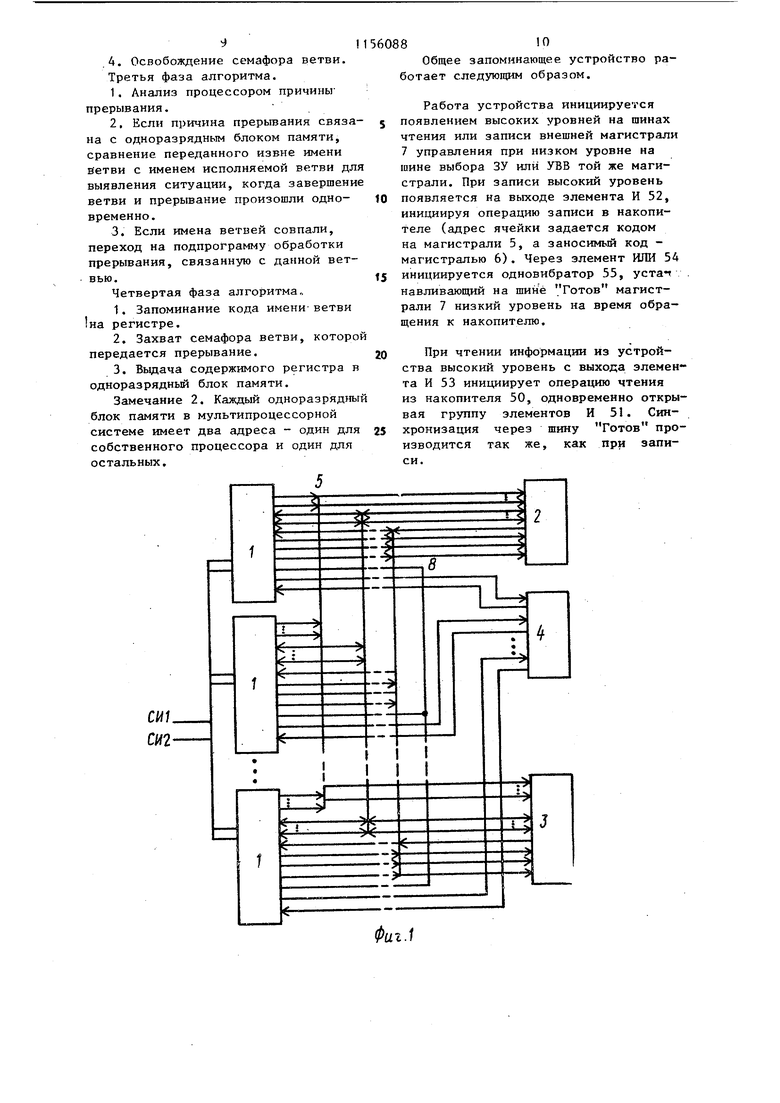

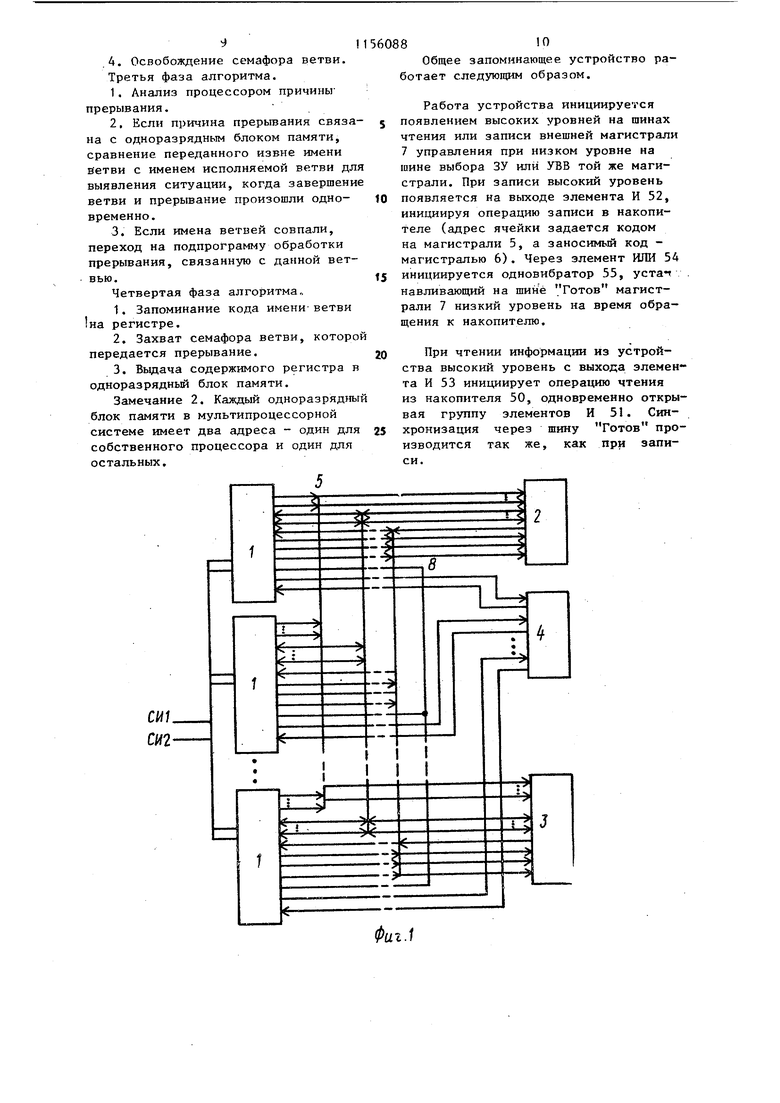

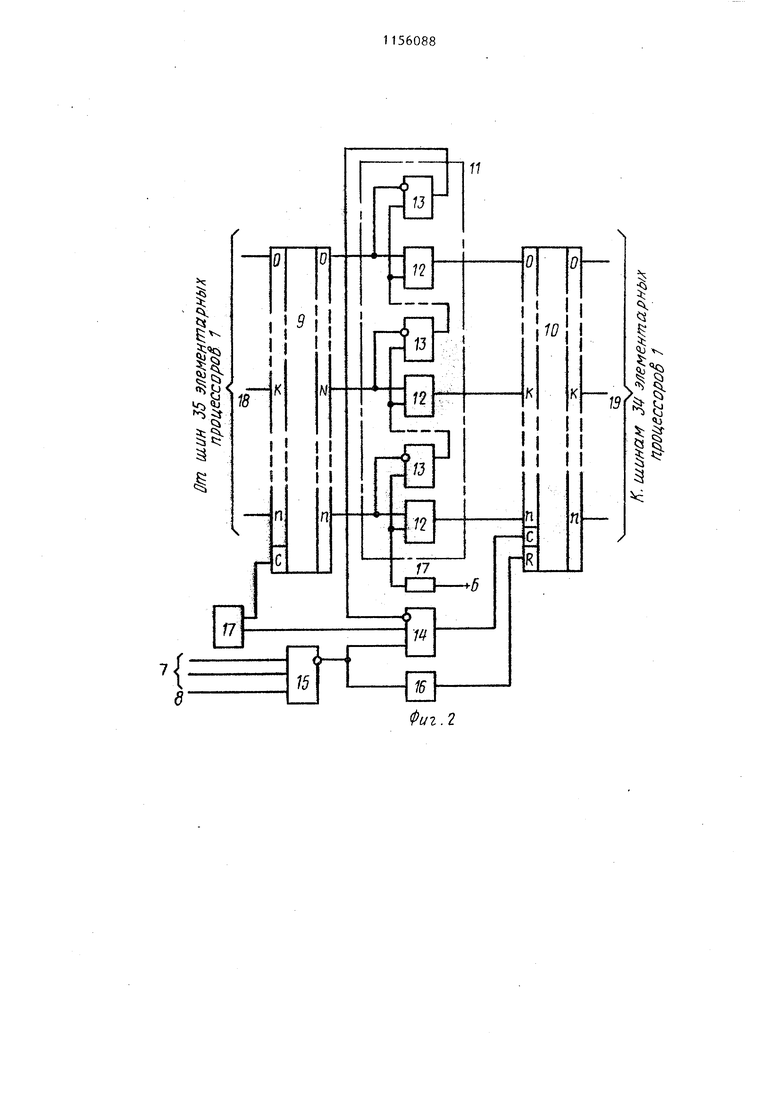

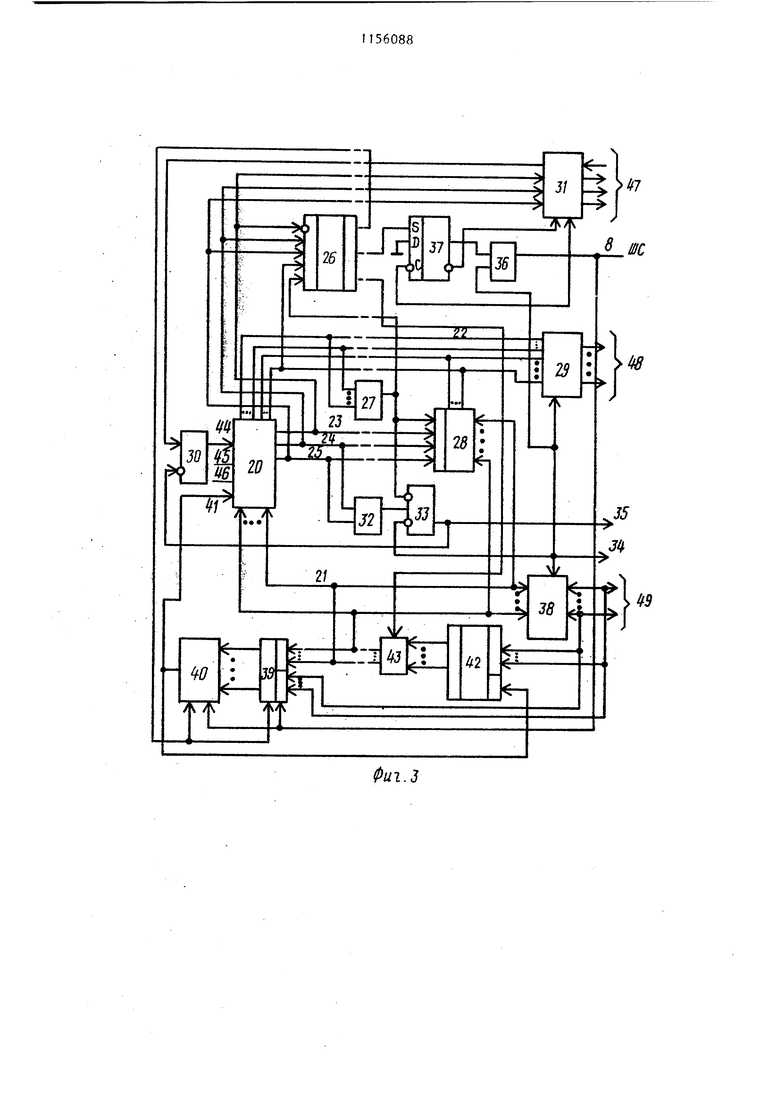

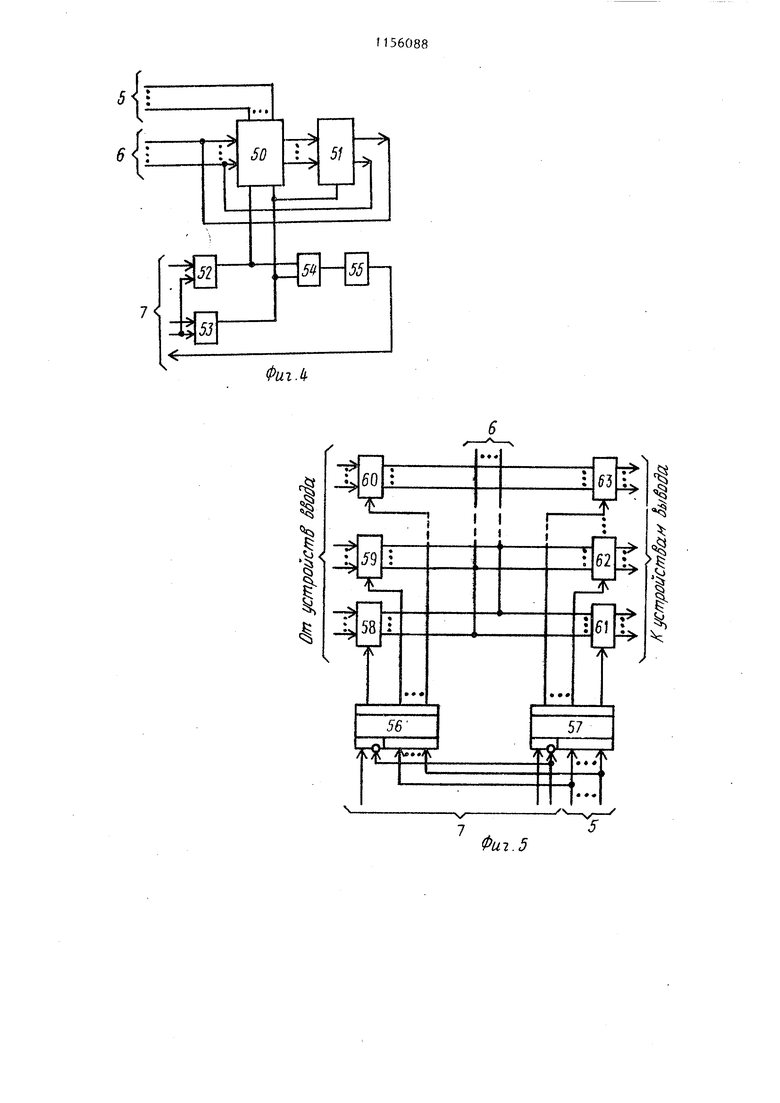

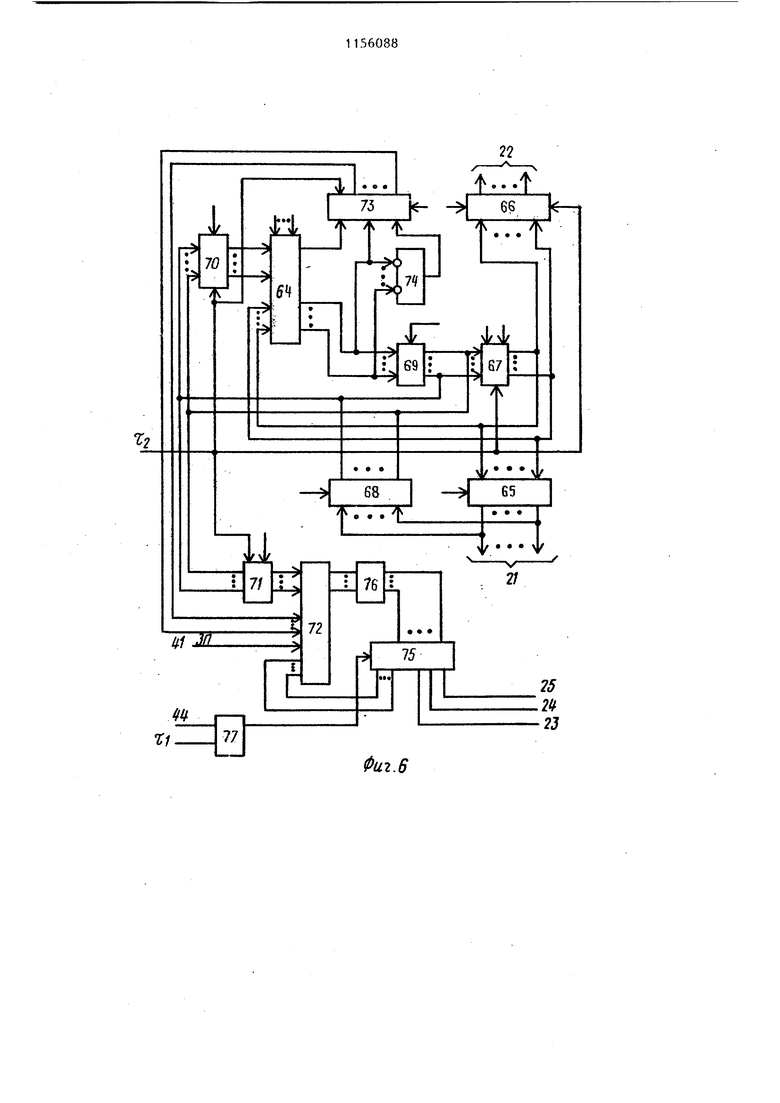

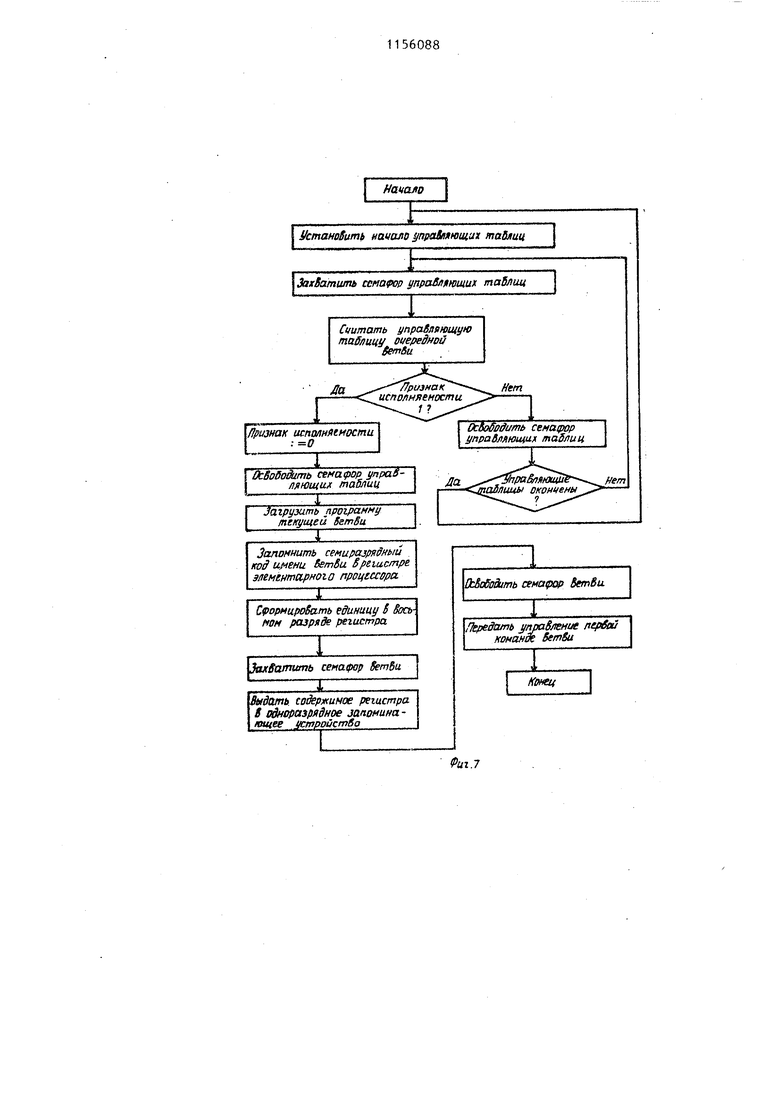

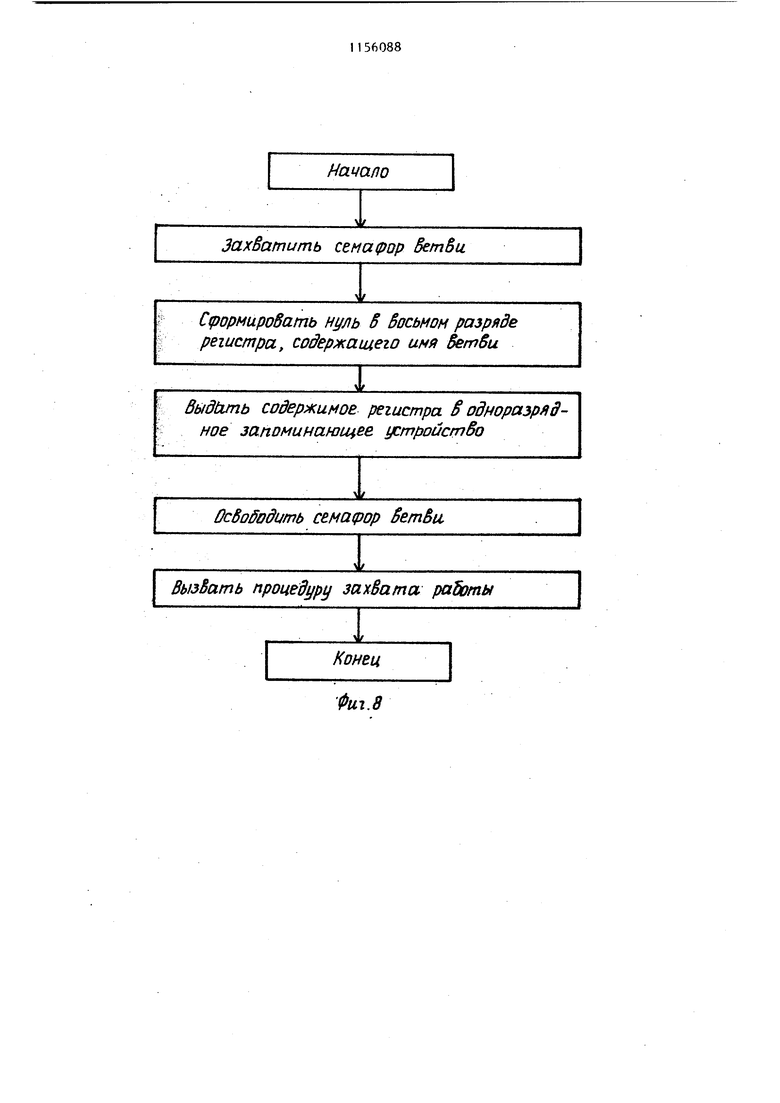

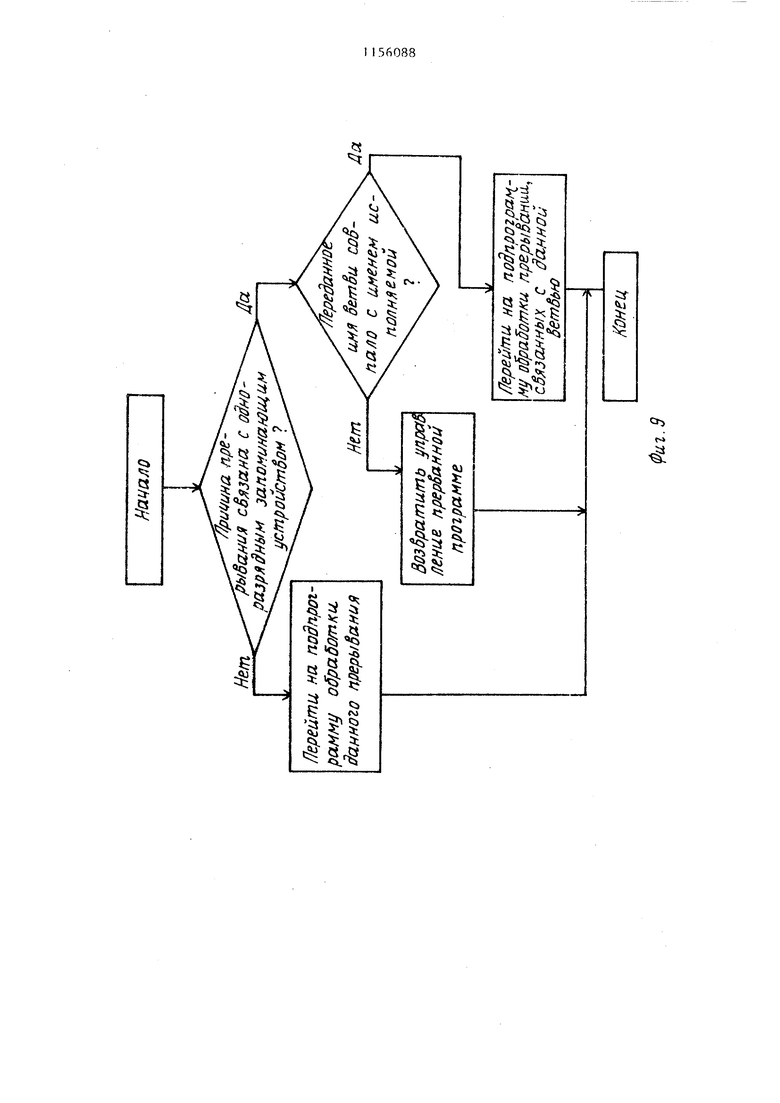

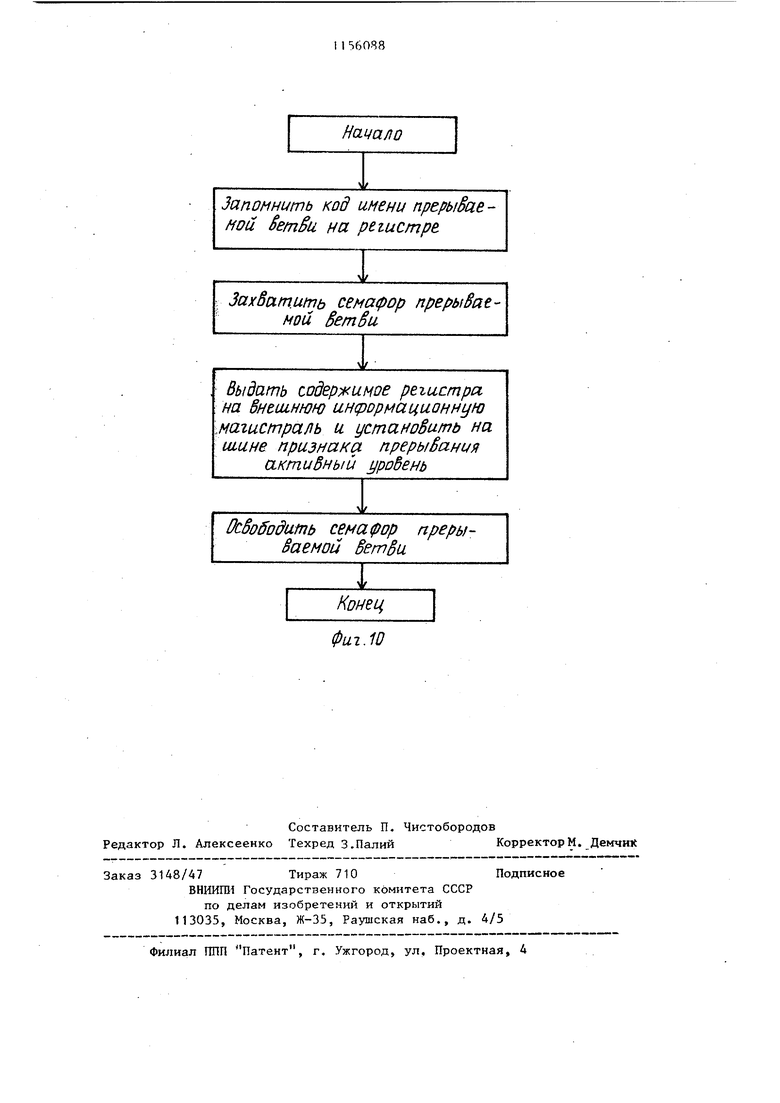

На фиг. 1 представлена структурная схема предлагаемой системы; на фиг. 2 - блок приоритета:, на фиг.Зсхема процессора; на фиг. 4 - схема общего запоминающего устройства;. на фиг. 5 - схема коммутатора общих устройств ввода-вывода; на фиг. 6 схема микропроцессора; на фиг.. 7-10блок-схемы алгоритмов функционирования системы.

Система состоит из нескольких процессоров 1, общего запоминающего устройства 2, коммутатора 3 общих устройств ввода-вывода, блока 4 приоритета, связанных между собой внешними магистралями адреса 5, данных 6 управления 7, а также щиной 8 признака прерывания.

Блок приоритета содержит входной регистр 9, выходной регистр 10, комбинационную схему 11, которая содержит первую группу элементов II 12 и вторую группу элементов И 13, элементы И 14 и 15, одновибратор 16, тактирующий генератор 17, входы 18 запросов, выходы 19 разрешения. Каждый процессор содержит микропроцессор 20, магистраль 21 данных, магистраль 22 адреса, управляющие шины 23, 24 и 25, дешифратор 26, элемент И 27, блок 28 памяти, буферт1ый регистр 29 адреса, блок 30 синхронизации, буферный регистр 31 управления элемент ИЛИ 32, элемент И 33, вход 34 разрешения, выход 35 запроса, элемент И 36, триггер 37, буферный регистр 38 данных, мультиплексор 39, одноразрядный блок 40 памяти, вход 41 прерывания микропроцессора, регистр 42, группу элементов И 43, тактовый вход 44 микропроцессора, входы 45 и 46 первой и второй синхросерии микропроцессора, управляющие выходы 47, адресные входы 48 и информационные входы-выходы 49 процессора.

Общее запоминающее устройство содержит накопитель 50, группу элементов И 51, элементы И 52 и 53, элемент ИЛИ 54, одновибратор 55. Коммутатор общих устройств вводавывода содержит дешифраторы 56 и 57, группы элементов И 58-63, Микропроцессор содержит сумматор .64, регистр 65 выходных даннык, буферный регистр 66 адреса, узел регистров 67, регистр 68 входных данных, блок элементов И 69, регистр 70 текущих данных, регистр 71 команд, регистр 72 адреса, регистр 73 признаков, элемент И 74, регистр 75 мик рокоманд, блок 76 памяти микрокоманд элемент И 77. Б качестве микропроцессора может быть использован стандартный микропроцессор КР580 ИК 80. Система работает следующим образом. Каждый процессор 1 может обращат ся к общему запоминающему устройству 2 и к коммутатору общих устройст ввода-вывода 3 с помощью магистрале 5, 6 и 7. При необходимости использовать эти магистрали процессор устанавливает высокуй уровень -на своем выходе запроса шин. Сигналы запроса шины, поступающие от всех элементар ных процессоров, анализируются блоком 4, который устанавливает сигнал высокого уровня на входе разрешени шины того из запросивших шину элеме тарных процессоров, чей приоритет максимален. Каждый из элементарных процессоров, получив сигнал разрешения шины используя магистрали 5-7, выполняет обращение к устройству 2 или коммутатору 3 и снимает запрос шины со своего выхода. Каждый процессор, получая для pea лизации ветвь программы, записьшает в один из своих внутренних узлов одноразрядный блок памяти - единицу в ячейке, соответствующей номеру выполняемой ветви. Таким образом, в каждый конкретны момент времени в одноразрядном блоке памяти процессора записаны ециниць в ячейках, соответствующих выполняемым им ветвям программы. При возникновении у процессора необходимости обменяться информацией с процессором, вьтолняющим J-10 ветвь программы, i-й процессор запрашивает шины и, получив их, выставляет на внешней магистрали 6 данных код номера j-й ветви и подает на шину 8 признака прерывания сигнал инициирующий обращение к одноразрядным блокам памяти всех процессоров 1 Единичный уровень появляется на выходе одноразрядного блока памяти только в процессоре, реализующем j-ю ветвь программы. Этот уровень вызывает прерывание работы этого процессора, и последний переходит к выполнению программы информационного обмена, например, через устройство 2. Для того, чтобы проиллюстрировать работу системы, предположим, что параллельная программа состоит из двух ветвей: Ветвь 2. Ветвь 1. Захватить семаL1, Захватить семафор ветви 1, фор ветви 1, Записать в А Считать А, единицу. Если , запиПослать прерысать А в В. вание ветви 1. Перейти на L2. Освободить семафор ветви 1, Освободить семаКонец ветви 2, фор ветви 1, Останов, Перейти на L1, Конец ветви 1 . Пусть начальное содержание ячейки А в общем запоминающем устройстве равно О, Управляющие таблицы программы в общем запоминающем устройстве будут иметь вид: Ветвь 1.Ветвь 2, Программа Программа 1.2. Признак испол- Признак исполняемости равен О, няемости равен О, Предположим далее, что в системе имеются три процессора. Тогда функционирование системы осуществляется следующим образом. Процессор с максимальным приоритетом под управлением программы операционной системы, размещенной в его внутреннем запоминающем устройстве, закватывает семафор управляющих таблиц, обращается к управляющим таблицам. В них процессор отыскивает не- исполняемую ветвь (ветвь 1), отмечает ее признаком исполняемости, равным единице, загружает и программу ветви 1 и освобождает семафор. Затем второй процессор захватывает семафор, обращается к управляющим таблицам, в которых обнаруживает, что ветвь 1 исполняется, а ветвь 2 не исполняется, отмечает ветвь 2 признаком исполняемости, равным единице. загружает программу ветви 2 и освобождает семафор. Третий процессор также обращается к таблицам, но обнаружив, что все ветви исполняются, переходит в режим ожидания. Первый и второй процессоры после загрузки программ переходят к их исполнению. Исполнение программы ветви начинается обращением к операционной системе соответствующего процессора, которая осуществляет запись единицы в ячейку одноразрядного блока памяти. Так, первый процессор записывает единицу в ячейку, соответствующую ветви 1, а второй процессор - в ячейку, соответствующую ветви 2. Одноразрядный блок памяти третьего процессора не содержит единиц. Затем первый и второй процессоры начинают выполнениесвоих программ. Если первым семафор ветви 1 захватывает процессор, выполняющий ветвь 1, то он обнаруживает, что ячейка А содержит нуль, и переходит к команде останова, после чего семафор захватывает второй процессор. Этот процессор записывает в А единицу, посылает прерывание ветви 1 и завершает выпол нение своей программы. Сообщение о прерывании проступает на входы всех процессоров, но на него реаги-рует лишь перв.ый, так как только в его од норазрядном блоке памяти имеется единица в ячейке, соответствующей ве ви 1. Первый процессор в момент пре- рывания либо находится перед первой командой программы, либо в состоянии останова, что обеспечивается защитой остальной программы семафором и особенностью быдачи прерывания. В том и в другомслучае управление передается операционной системе, которая лишь увеличивает содержимое счетчика команд на единицу, т.е. передает управление следующей команде программы В первом случае управление непосредственно передается на метку 1, а во втором - на команду перехода на метку 1 . Поэтому в любом случае первый процессор считает единичное значе ние из ячейки А, записьшает его в ячейку В и переходит на метку 2 конца своей программы. Если же второй процессор захватывает семафор ветви 1 прежде, чем пер-55 вый процессор записывает единицу в свой одноразрядный блок памяти, то посланное им прерывание не воспринимают ни первый, ни третий процессоры, и после того, как он закончит выполнение своей программы, первый процессор записьшает единицу в свой одноразрядный блок памяти, считывает содержимое ячейки А, где уже находится единица, записывает его в ячейку В и заверщает выполнение своей программы. Таким образом, при любом ходе вычислительного процесса результатом параллельной программы будет , , на что не требуется ни циклического опроса ячейки, ни дополнительного блокирования шины. Процессор работает следующим образом. При всяком обращении микропроцессор 20 устанавливает на внутренней магистрали 22 адреса код адреса, на щинах 23 и 24 - сигнал, определяющий направление передачи информации по магистрали 21 данных (в микропроцессор - чтение, из микропроцессора - запись), а на шине признака ЗУ или УВВ - сигнал, интерпретирующий код, выставленный на магистрали адреса, в качестве ячейки ЗУ или номера устройства ввода-вывода. При записи микропроцессор выдает информацию на внутреннюю магистраль данных, а при чтении принимает. При обращении к блоку 28 памяти микропроцессор выставляет на магистрали 22 адреса код, старшие разряды которого, воздействуя на элемент И 27, вызывают появление на выходе последнего сигнала, разрешающего работу блока 28 и дешифратора 26, Сигнал на управляющей шине 25 ЗУ или УВВ выбирает один из названных блоков, запрещая другой. Работа выбранного устройства инициируется появлением сигнала на шинах 23 или 24. Младшая часть адреса при этом опр. номер ячейки в ЗУ, к которой производится обращение, или тот выход дешифратора 26, на котором появ-ляется разрешающий сигнал. При обращении к общему запоминающему устройству 2 или коммутатору 3 общих устройств ввода-вывода (фиг. 1) микропроцессор 20 выставляет на п внутренней магистрали 22 адреса код, старшая часть которого не вызывает появления на выходе элемента И 27 сигнала лог. 1 . Поэтому появление сигналов записи или чтения на шинах 23 или 24 вызывает появление сигнала уровня лог.1 на выходе элемента И 33, Этот сигнал приостанавливает работу микропроцессора, воздействуя на него через блок 30 синхронизации, и поступает на выход 35 saпроса шин, взаимодействующий с блоком 4, Сигнал блока 4 по входу 34 разрешения шин подключает регистры 29, 31 и 38 к внешней магистрали системы. Регистры открыты до тех пор пока микропроцессор не закончит цикл обращения к общему запомина:ющему устройству или коммутатору общих УВВ Время цикла обращения в этом случае задается сигналом Готов внешней магистрали, который воздействует на вход 44 микропроцессора 20 через регистр 31 и блок 30 синхронизации. Момент окончания цикла определяется микропроцессором 20, который снимает сигналы записи vism чтения, вследстви чего блок.4 устанавливает на входе 34 уровень лог.О, закрывая регистры 29, 31 и 38 и отключая внутренние магистрали процессора от внешних.

При записи информации в одноразрядный блок 40 памяти микропроцессор выставляет на шине признака ЗУ шш УВВ (Сигнал лог. О, на магистрали адреса - код, вызывающий появление сигнала на втором выходе дешифратора 26. Этот сигнал переключает мультиплексор 39 таким образом, что информация с внутренней магистрали 21 данных поступает на адресные и информационные входы блока 40. Код, выставляемый микропроцессором 20 на магистрали 21 данных, определяет адрес ячейки в блоке 40 и записываемый в эту ячейку код.

Для передачи прерывания на какойлибо процессор системы микропроцессор 20 устанавливает триггер 37 в состояние 1, выполняя цикл записи в УВВ. Триггер 37 своим нулевым выхо дом блокирует регистр 31. Далее описанным способом инициируется цикл, аналогичшлй записи в общее запоминающее устройство. Однако при получении с внешней магистрали сигнала разреше ния открьшаются регистры 29 и 38 (регистр 31 блокирован) и элемент И 36, который выставляет на внешней магистрали сигнал на шине 8 признака прерывания. Сигналы чтения и записи на внешнюю магистраль через блокированный регистр 31 не поступают. Таки образом, на внешней магистрали 6 данных оказывается код номера прерываемой ветви, сопровождаемый сигналом ня шине 8 признака прерывания.

Этот сигнал воздействует на входы чтения одноразрядных блоков 40 памяти всех процессоров. Код с внешней магистрали данных выбирает в блоке 40 ячейку, к которой производится обращение. Если в данном процессоре из блока 40 прочитана единица, на микропроцессор 20 поступает запрос прерывания и в регистр 42 записывается с внешней магистрали 6 данных код вызвавший это прерывание. Реагируя на сигнал запроса прерывания, микропроцессор 20 принимает информацию из регистра 42, производит операцию обращения , при которой на дешифраторе 26 оказывается в состоянии лог. 1 выход, управляющий группой 43. Анализируя эту информацию, микропроцессор выясняет, по какой из выполняемых им ветвей программы произошло прерывание, и производит действия, предусмотренные программой реакции на прерывание.

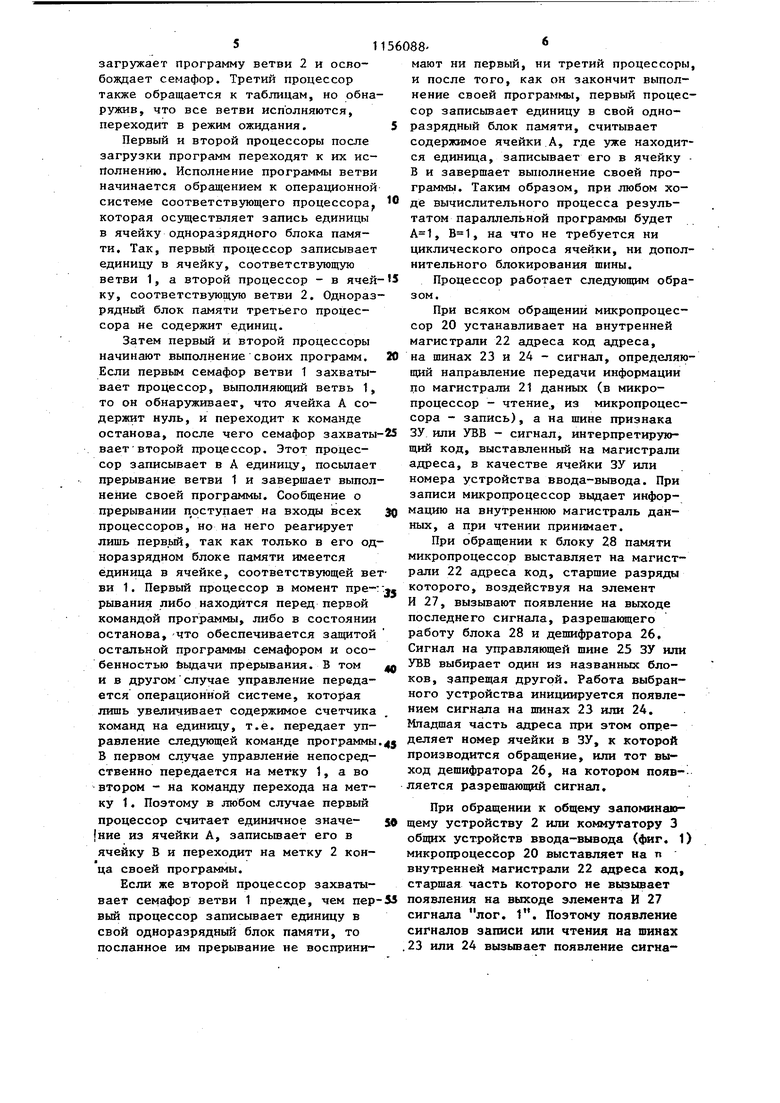

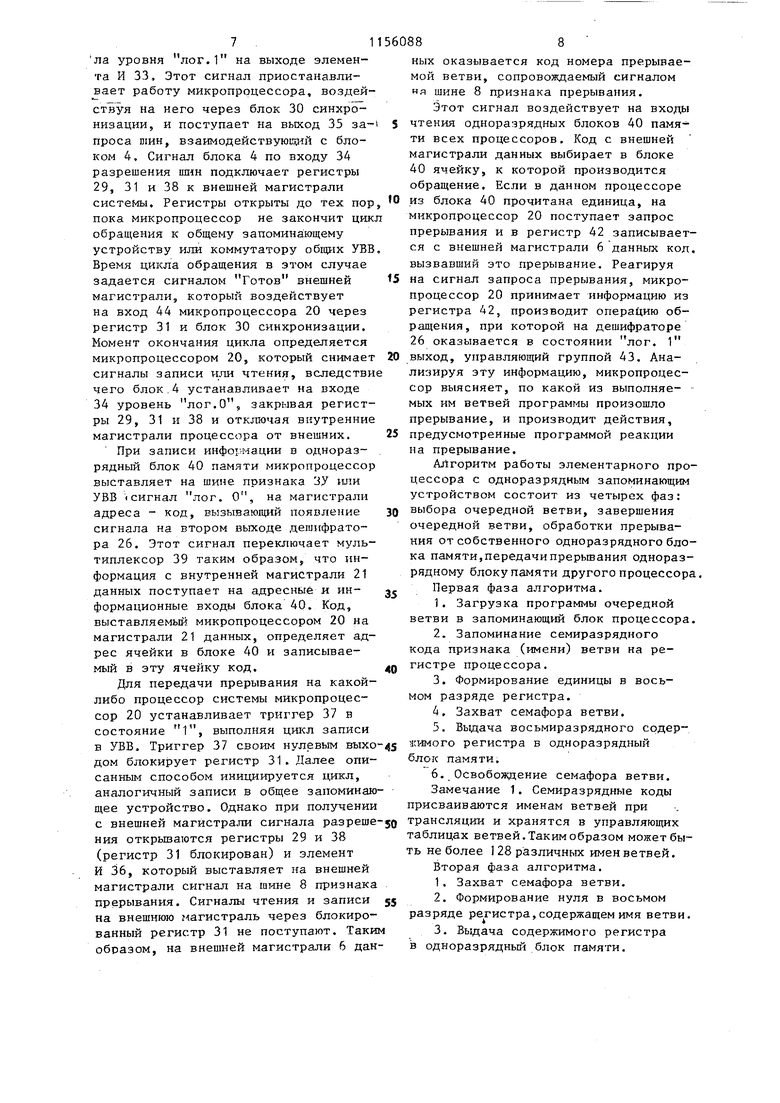

Алгоритм работы элементарного процессора с одноразрядным запоминающим устройством состоит из четырех фаз: выбора очередной ветви, завершения очередной ветви, обработки прерывания от собственного одноразрядного блока памяти,передачипрерьшания одноразрядному блоку памяти другого процессор

Первая фаза алгоритма.

присваиваются именам ветвей при трансляции и хранятся в управляющих таблицах ветвей. Таким образом может быть не более I 28 различных имен ветвей. Вторая фаза алгоритма.

СИ1.

сиг810Общее запоминающее устройство работает следующим образом. Работа устройства инициируется появлением высоких уровней на шинах чтения или записи внешней магистрали 7 управления при низком уровне на шине выбора ЗУ или УВВ той же магистрали. При записи высокий уровень появляется на выходе элемента И 52, инициируя операцию записи в накопителе (адрес ячейки задается кодом на магистрали 5, а заносимый код магистралью 6). Через элемент ИЛИ 54 инициируется одновибратор 55, устат . навливающий на шине Готов магистрали 7 низкий уровень на время обращения к накопителю. При чтении информации из устройства высокий уровень с выхода элемента И 53 инициирует операцию чтения из накопителя 50, одновременно открывая группу элементов И 51. Синхронизация через шину Готов производится так же, как при записи.

Фиг.г

0U1.3

Фи1.5

Фиг.6

Устано1ить нача/ю npaSaii№U4ux таблиц

Захватить ccMOfop угграЛ/тюших таблиц паВлицу очередной

Запоннить семиразрядна/и код имени SemSu Sptmcmpt элементарного процессора

CfopHupoSamb единицу S Sonнон разряде регистра

Считать упраВяяющую бетби

Ma. „„ paSnxtauSie -,, иет 11Сшлииы окончены

IkSoSodumb txnayjop SemSu

1

kpedamb i/праВлемие nefifyu команх BemSu

3ttxSaJTntmb семафор SemBu

Выдать todeptKuHoe регистра В аЗноразрядное запоминаittUtee Jfcmpoucmea

Фиг.8

гГ W §r

ill

i titt

Q

1

t

СГ5

f-

Начало

Запомнить код имени прерывав ной SemBu на регистре.

Захватить семафор прерыВаемой §етёи

Выдать содер кимое регистра.

на eHtuiHHjH) информационную

магистраль и установить на

илине признака прерыёан(.я

актибный t/родень

Oc8o6odufnb сен а (pop прерываемой ёетёи

Коищ

фт.Ю

| Прангишвили И.В | |||

| и др | |||

| Микропроцессорные системы | |||

| М., Наука, 1980, с | |||

| Прибор для корчевания пней | 1921 |

|

SU237A1 |

| Computer Design, March, 1978, p | |||

| Горный компас | 0 |

|

SU81A1 |

| . | |||

Авторы

Даты

1985-05-15—Публикация

1983-11-16—Подача