Z

да

со 00

4:

Фи9.1

. Изобретение относится к импульсной технике и предназначено для использования в счетчиках и формирователях импульсов.

Известен делитель частоты на три, содержащий три D -триггера, первый и второй элементы И-НЕ и инвертор,, причем объединенные тактовые входы первых двух триггеров соединены с тактовым входом третьего триггера через инвертор, выход первого.триггера соединен с 1)-входом второго триггера и первым входом первого элемента И-НЕ,. выход второго D-триггера соединен с D -входом третьего триггера, вторым входом первого элемента И-НЕ и первым входом второго элемента И-НЕ, второй вход которого соединен с выходом третьего триггера, причем выход первого элемента И-НЕ соединен с D твходом первого триггера 1J,

Недостатком известного устройства является сложность.

Наиболее близким к. предлагаемому по технической сущности является устройство, содержавшее первый и второй I)-триггеры, инвертор и элемент И-НЕ, причем тактовый вход первого D -триггера соединен с входом инвертора , выход которого подключен к тактовому входу второго D -триггера, а неинверсный выход первого триггера подключен к первому входу элемента И-НЕ 2 J.

Однако устройство характеризуется сложностью, так как для организации делителя используются дополни-- тельные входы триггеров, а также низкой надежностью, связанной с состояниями по фронтам.

Цель изобретения - повышение надежности функционирования устройства и его упрощение.

Поставленная цель достигается тем, что в делителе частоты на три, содержащем первый и второй D -триггеры, инвертор и элемент И-НЕ, причем тактовый вход первого 5-триггера соединен с входом инвертора, выход которого подключен к тактовому входу второго I)-триггера, а неинверсный выход первого Р-триггера подключен к первому входу элемента И-НЕ, второй вход элемента И-НЕ подключен к прямому выходу второго D -триггера, а выход - к D-входам первого и второго D-триггеров.

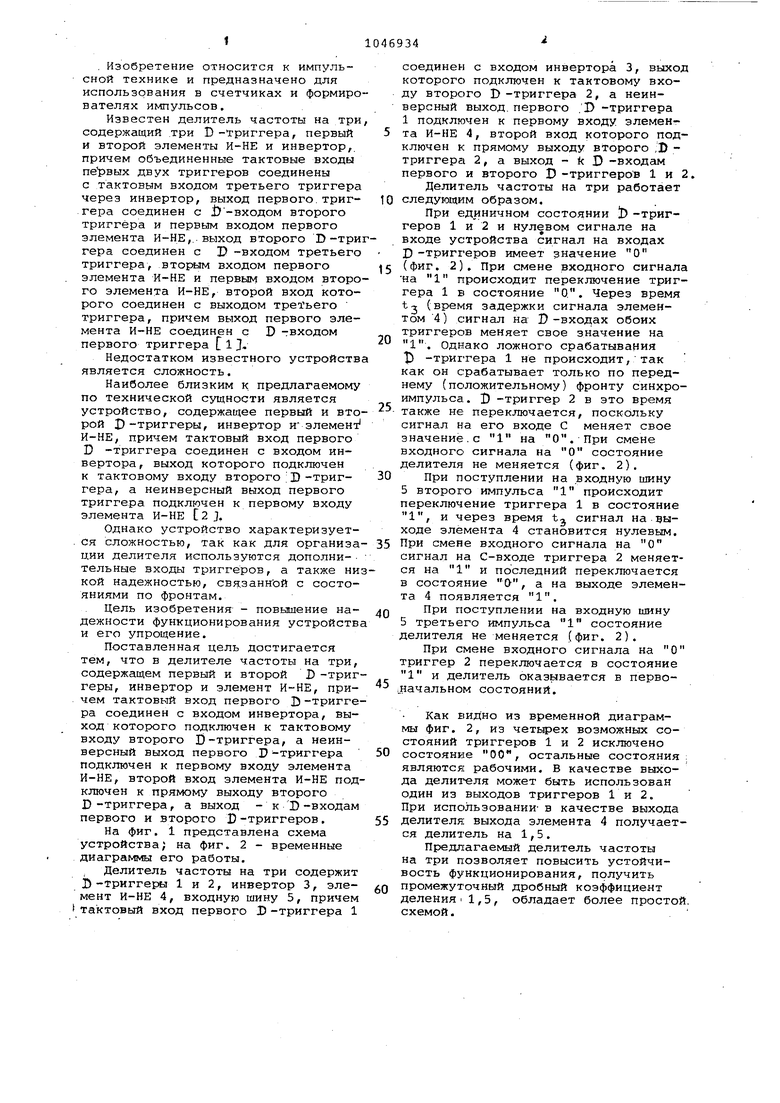

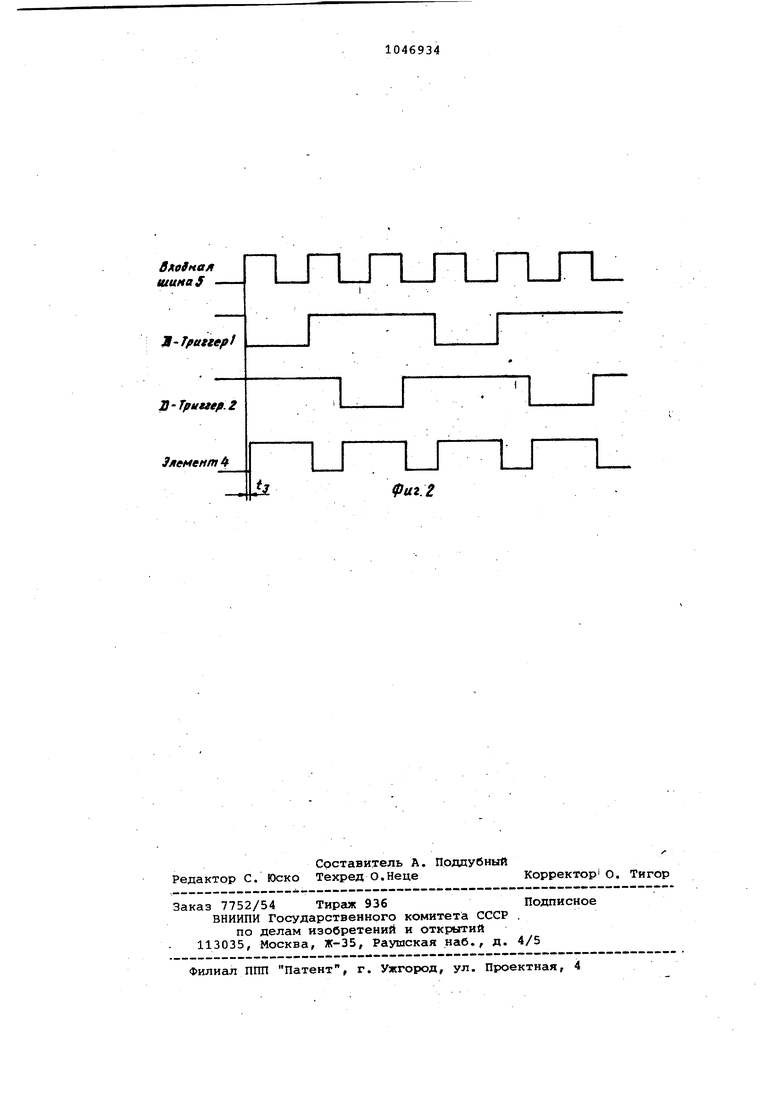

На фиг. 1 представлена схема устройства; на фиг. 2 - временные диаграммы его работы.

Делитель частоты на три содержит i)-триггеры 1 и 2, инвертор 3, элемент И-НЕ 4, входную шину 5, причем тактовый вход первого .D -триггера 1

соединен с входом инвертора 3, выход которого подключен к тактовому входу второго D -триггера 2, а неинверсный выход, первого .D -триггера 1 подключен к первому входу элемента И-НЕ 4, второй вход которого подключен к прямому выходу второго ,D триггерг1 2, а выход - k D -входам первого и второго D -триггеров 1 и 2, Делитель частоты на три работает

0 следующим образом.

При единичном состоянии 1) -триггеров 1 и 2 и нулевом сигнале на входе устройства сигнал на входах D -триггеров имеет значение О

с (фиг. 2), При смене входного сигнала

л

на

происходит переключение триггера 1 в состояние О.. Через время t3 (время задержки сигнала элементом 4) сигнал на D -входах обоих триггеров меняет свое значение на Ч. Однако ложного срабатывания

X) -триггера 1 не происходит, так как он срабатывает только по переднему (положительному) фронту синхроимпульса. 1) -триггер 2 в это время

5 также не переключается, поскольку сигнал на его входе С меняет свое значение.с 1 на О. При смене входного сигнала на О состояние делителя не меняется (фиг. 2).

0 При поступлении на .входную шину 5 второго импульса 1 происходит переключение триггера 1 в состояние 1, и через время t сигнал на выходе элемента 4 становится нулевым.

5 При смене входного сигнала на О сигнал на С-входе триггера 2 меняется на 1 и последний переключается в состояние О, а на выходе элемента 4 появляется 1.

Q При поступлении на входную шину 5 третьего импульса 1 состояние делителя не меняется (фиг. 2).

При смене входного сигнала на О триггер 2 переключается в состояние

1 и делитель оказывается в перво..начальном состояний.

Как видно из временной диаграммы фиг. 2, из четырех возможных состояний триггеров 1 и 2 исключено

состояние 00, остальные состояния : являются рабочими. В качестве выхода делителя может быть использован один из выходов триггеров 1 и 2. При использовании- в качестве выхода

делителя выхода элемента 4 получается делитель на 1,5.

Предлагаемый делитель частоты на три позволяет повысить устойчивость функционирования, получить

промежуточный дробный коэффициент деления1,5, обладает более простой. схемой.

Вкавмал шина 5 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой синхронизации | 1985 |

|

SU1332553A1 |

| Делитель частоты следования импульсов на 1,5 | 1980 |

|

SU926767A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2444123C1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1471315A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1775854A1 |

| Д-триггер | 1985 |

|

SU1248034A1 |

| ПРЕЦИЗИОННЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ИЗМЕРИТЕЛЬ | 2001 |

|

RU2208797C1 |

| ДВУХТАКТНЫЙ ТРАНЗИСТОРНЫЙ ИНВЕРТОР | 1993 |

|

RU2046527C1 |

| Устройство для приема биимпульсных сигналов | 1990 |

|

SU1741282A2 |

| Многоканальный формирователь одиночных импульсов | 1985 |

|

SU1243115A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ НА ТРИ, содержащий первый и второй D-триггеры, инвертор и элемент И-НЕ, причем тактовый вход первого D-триггера соединен с входом инвертора, выход которого подключен к тактовому входу второго D -триггера, а неинверсный выход первого Л)-триггера подключен к.первому входу элемента И-НЕ, отличающийся тем, что, с целью повьшения надежности и упрощения устройства, второй вход элемента И-НЕ подключен к пря мому выходу второго I)- триггера, а выход - к /D -входам первого и второго D-триггеров.

Ji-Tftttiept

S-Tpiftfef.Z

Зяемент

f,

Г

фиг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент aiJA 3943379, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Делитель частоты импульсов | 1977 |

|

SU646444A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-10-07—Публикация

1982-01-05—Подача