(54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Делитель частоты с переменным коэффициентом деления | 2020 |

|

RU2752485C1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Устройство для коррекции числа импульсов по входному параметру | 1984 |

|

SU1187146A2 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1732465A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 1993 |

|

RU2041562C1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1328937A1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2086437C1 |

Изобретение-ОТНОСИТСЯ к импульсной технике.

Иэв.естен -делитель частоты импуль сов, содержащий делитель частоты нд Т-ри-, состоящий из двух Э -триггеров и блока Формирования, состоящего из триггера и четырех элементов И-НЕ 11 .

ётот де.питель частоты относитель,нр .сложен. .- Наиболее близок к предлагаемому .делитель частоты .импульсов, сбдёржа щий делитель частоты ва три, состо ящий из двух) -триггеров и элемента И-НЕ, один вход которого соединен с С-входом триггера и входной тиной, второй вход элемента Й-НЕ соединен с ПР.ЯМЫМ выходом первого триггера, выход элемента И-НЕ связан с С-входом второго триггера, инверсный выход которого подключен к5 входу первого триггера и;0-входом .второго, причем) -:вход первого триГ гера соединён с его инверсным выходом . . . ...

Данный делитель частоты не позврляет получить дополнительный коэффициент деления. .

Цель Изобретения - повышение стаби.льности деления и получение допол.нительного коэффициента деления.

Поставленная цель достигается тем, чти в де.питель частоты импульсов, содержащийделитель, частоты на три, состоящий из двух D-триггеров и элемента И-НЕ, одинвход которого соединен с С-входом первого триггера и входной шиной, другой вход элемент та И-НЁ соединен с прямым выходом первого триггера, 6ыходэ.лемента И-НЕ соединей с С-входом второго триггера, инверсный выход которого подключен к 5-входу . первого триггера и второго, причем С-вход первого триггера соединен с его инBepcHEJM выходом, введен дополнительный элемент И-НЕ, один вход которого соединен с прямым .выходом первого триггера, а другой подключен к инйёрсному выходу.второго триггера.

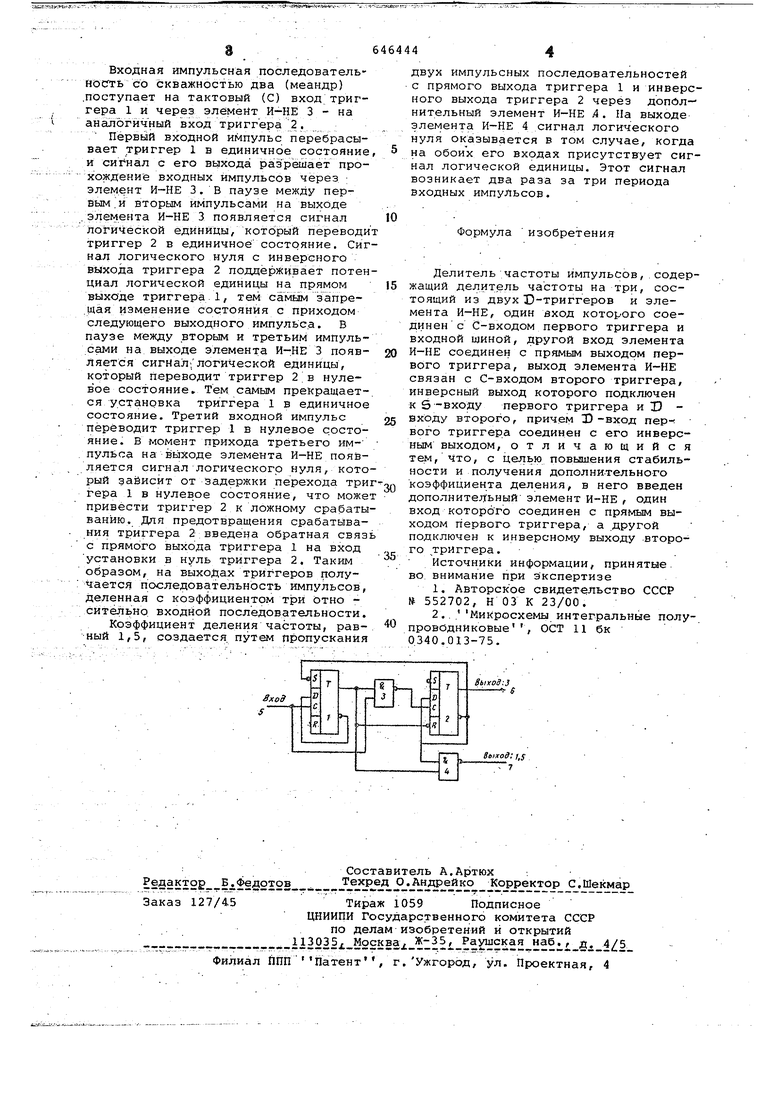

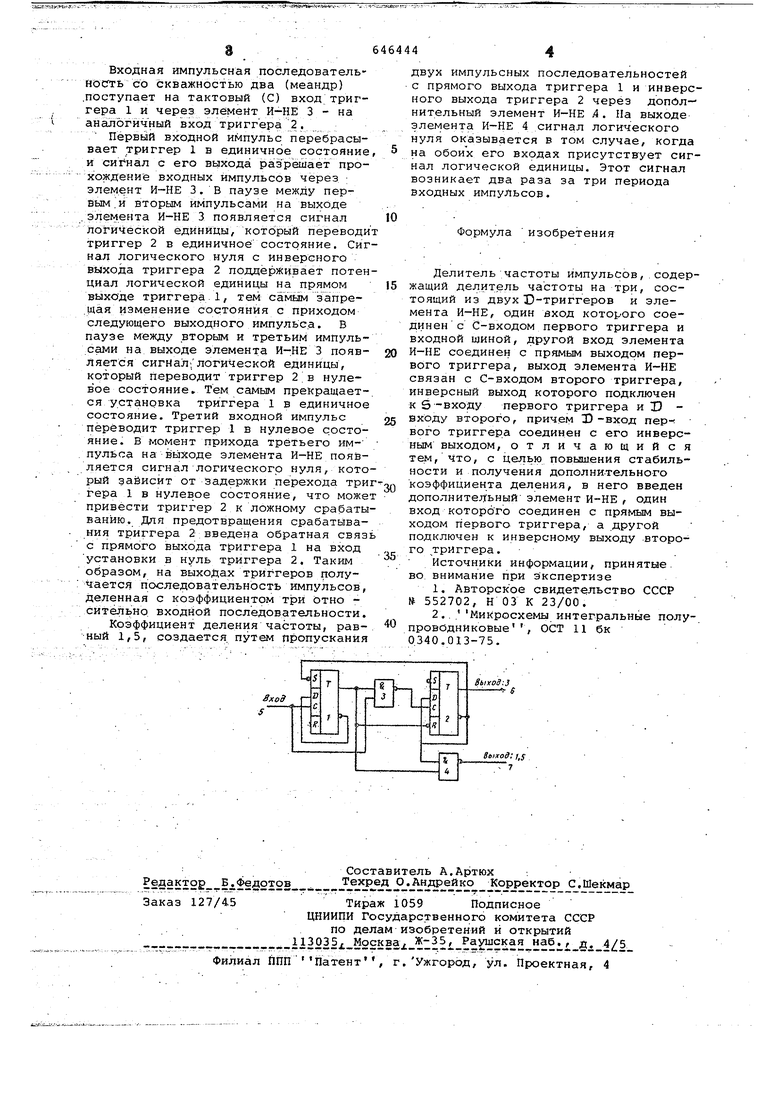

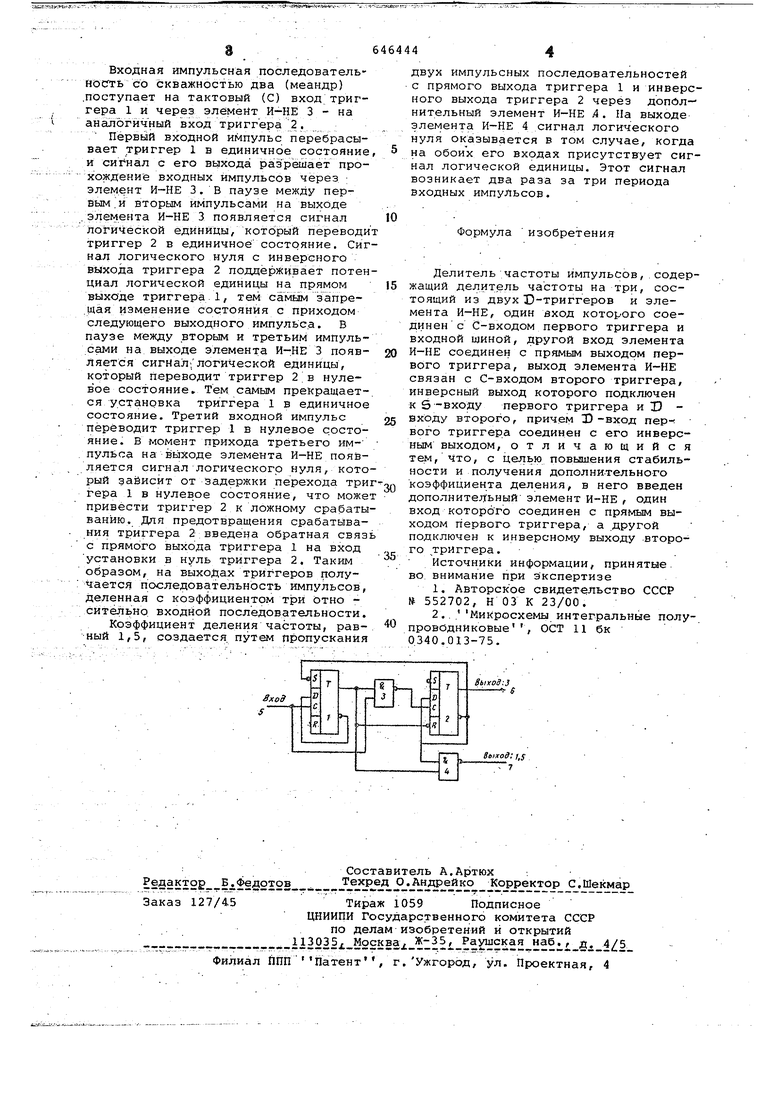

Структурная электрическая схема описываемого делителя час,тоты приведена начертеже. .

Делитель содержит D-триггеры; 1, 2 и элементы И-НЕ 3,-4.-.

Принцип работы делителя закях) чается в слеДуквдем. Входная импульсная последовательноэть со скважностью два (меандр) .поступает на тактовый (С) вход триггера 1 и через элемент И-НЕ 3 - на аналогичный вход триггера2. Первый входной импульс перебрасывает триггер 1 в единичное состояние и сигнал с его выхода ра:зрёшает прохождение входных импульсов через ; элемент И-НЕ З.В паузе между первым.и вторым импульсами на выходе .элемента И-НЕ 3 появляется сигнал Логической единицы, котбрый переводи триггер 2 в единичное состояние. Сиг нал логического нуля с инверсного выхода триггера 2 поддерживает потен циал логической единицы на прямом выходе триггера 1, тем самьом Запрещая изменение состояния с приходом следующего выходного импульс.а. В паузе между вторым и третьим импульсами на выходе элемента И-НЕ 3 появляется сигнал;логической единицы, который переводит триггер 2 в нулевое состояние. Тем самым прекращается установка триггера 1 в единичное состояние. Третий входной импульс переводит триггер 1 в нулевое состояние. В момент прихода третьего импульса на ёыходе элемента И-НЕ появляется сигнал логического нуля, кото рый заёисит от задержки перехода три гера 1 в нулевое состояние, что може привести триггер 2 к ложному срабаты ванию. Для предотвращения срабатывания триггера 2,введена обратная связ с прямого выхода триггера 1 на вход установки в нуль триггера 2. Таким образом, на выходах триггеров полу: чается п оследовательность импульсов, деленная с коэффициентом три Отно ситёльно входной последовательности. Коэффициент деления частоты, равный 1,5, создается, путем пропускания двух импульсных последовательностей с прямого выхода триггера 1 и инверсного выхода триггера 2 через допил-нительный элемент И-НЕ .4 . На выходе элемента И-НЕ 4 сигнал логического нуля оказывается в том случае, когда на обоих его входах присутствует сигнал логической единицы. Этот сигнал возникает два раза за три периода Входных импульсов. Формула изобретения Делитель .частоты импульсов,.содержащий делитель частоты на три, состоящий из двух D-триггеров и элемента И-НЕ, один вход которого соединен с С-входом первого триггера и входной щиной, другой вход элемента И-НЕ соединен с прямым выходом первого триггера, выход элемента И-НЕ связан с С-входом второго триггера, инверсный выход которого подключен к S -входу первого триггера и D входу второго, причем D-вход пер-: вого триггера соединен с его инверсным выходом, отличающийся тем. Что, с целью повышения стабильности и получения дополнительного коэффициента деления, в него введен дополнительный элемент И-НЕ , один вход которого соединен с прямым выходом первого триггера, а другой подключен к инверсному выходу .второго триггера. Источники информации, принятые, во внимание при экспертизе 1, Авторское свидетельство СССР 552702, Н 03 К 23/00. 2.. . Микросхемы интегральные полупроводниковые , ОСТ 11 бк 0340.013-75.

Авторы

Даты

1979-02-05—Публикация

1977-09-30—Подача