1

(21)4499244/21

(22)01.07.88

(46)07.05.91. Бюл. № 17

(72) В.И.Назаренко

(53)621.317.2(088.8)

(56) Авторское свидетельство СССР

NJ 1226338, кл, G 01 R 25/04, 1984.

(54) КАЛИБРАТОР ФАЗЫ (57) Изобретение относится к фазомзмери- тельной технике и позволяет повысить рабочую частоту, уменьшить дискретное. ь воспроизведения фазовых сдвигов на верхних частотах и нелинейные искажения выходных сигналов. Калибратор фазы

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ | 2008 |

|

RU2381549C2 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕГРАФНЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2009615C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для управления энергопитанием микропроцессорной системы | 1983 |

|

SU1201829A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

Вых

(Л

с

о

X Ј 4 О

содержит задающий генератор 1, регистры 2, 6, 10 хранения управляющих кодов, блок 3 управления, вычислительный блок 4, ключ 5, адресный счетчик 9, шину 39 управления, шину 41 данных, шину 40 адреса, два идентичных канала 7, 8 формирования выходных сигналов. Каждый из каналов содержит циклический счетчик 11, регистры 12, 35, 38 управляющих кодов, дополнительный адИзобретение относится к фозоизмери- тельной техника и может быть использовано в устройствах для формирования в широком лиапазоне частот двух синхронных периодических напряжений произооль- иой формы и воспроизведения точных фазовых сдвигов между ними.

Цель изобретения - расширение частотного диапазона,

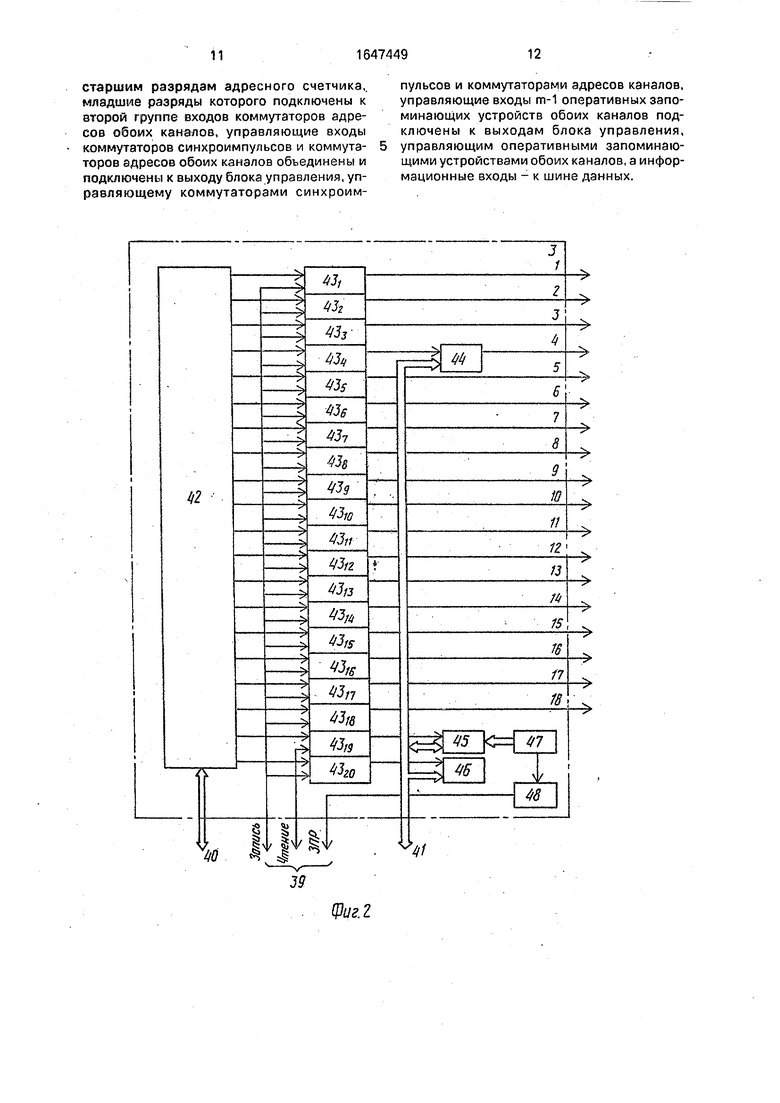

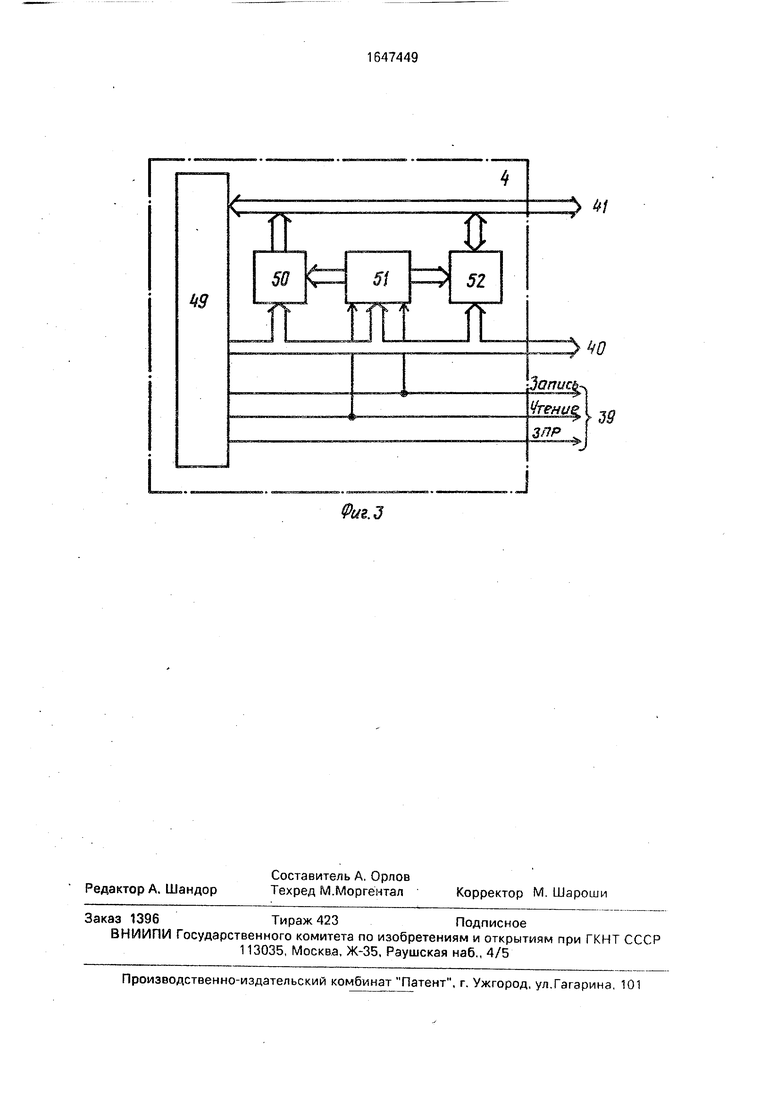

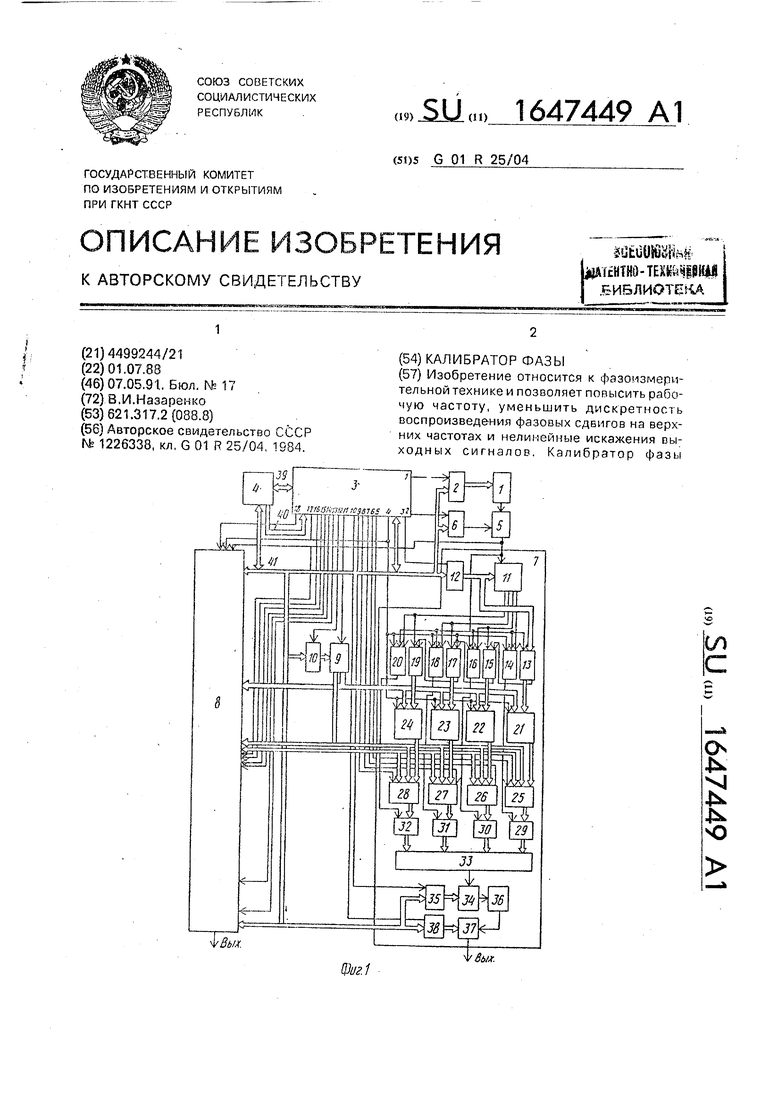

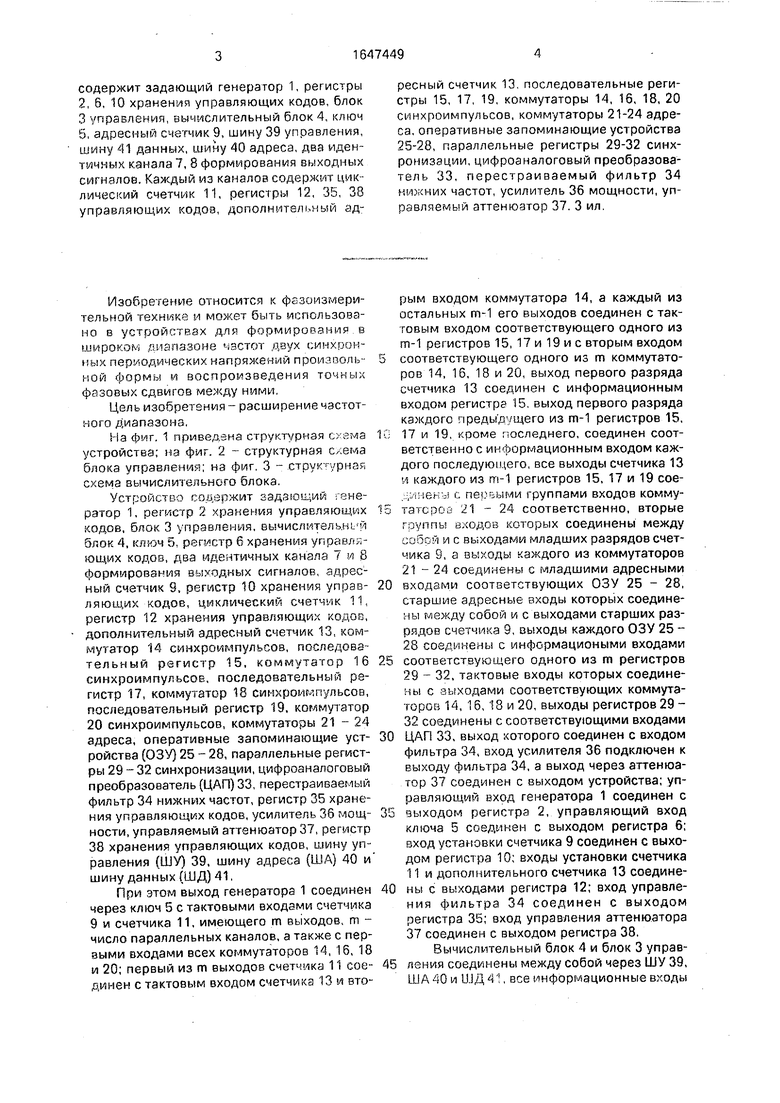

На фиг. 1 приведена структурная оама устройства; на фиг. 2 - структурная с.ема блока управления; на фиг. 3 - структурная схема вычислительного блока.

Устройство содержит задающий генератор 1, регистр 2 хранения управляющих кодов, блок 3 управления, вычислительной блок 4, ключ 5. регистр 6 хранения управляющих кодов, два идентичных канала 7 и 8 формирования ВУУОДНЫХ сигналов, адресный счетчик 9, регистр 10 хранения управ- ляющих кодов, циклический счетчик 11. регистр 12 хранения управляющих кодов, дополнительный адресный счетчик 13, коммутатор 14 синхроимпульсов, последовательный регистр 15, коммутатор 16 синхроимпульсов, последовательный регистр 17, коммутатор 18 синхроимпульсов, последовательный регистр 19, коммутатор 20 синхроимпульсов, коммутаторы 21-24 адреса, оперативные запоминающие уст- ройства (ОЗУ) 25 - 28, параллельные регистры 29 - 32 синхронизации, цифроаналоговый преобразователь (ЦАП) 33, перестраиваемый фильтр 34 нижних частот, регистр 35 хранения управляющих кодов, усилитель 36 мощ- ности, управляемый аттенюатор 37, регистр 38 хранения управляющих кодов, шину управления (ШУ) 39, шину адреса (ША) 40 и шину данных (ШД) 41,

При этом выход генератора 1 соединен через ключ 5 с тактовыми входами счетчика 9 и счетчика 11, имеющего m выходов, m - число параллельных каналов, а также с первыми входами всех коммутаторов 14, 16, 18 и 20; первый из m выходов счетчика 11 сое- динен с тактовым входом счетчика 13 м вторесный счетчик 13. последовательные регистры 15, 17, 19, коммутаторы 14, 16, 18, 20 синхроимпульсов, коммутаторы 21-24 адреса, оперативные запоминающие устройства 25-28, параллельные регистры 29-32 синхронизации, цифроаналоговый преобразователь 33, перестраиваемый фильтр 34 нижних частот, усилитель 36 мощности, управляемый аттенюатор 37. 3 ил.

рым входом коммутатора 14, а каждый из остальных т-1 его выходов соединен с тактовым входом соответствующего одного из т-1 регистров 15, 17 и 19 и с вторым входом соответствующего одного из m коммутаторов 14, 16, 18 и 20, выход первого разряда счетчика 13 соединен с информационным входом регистре 15, выход первого разряда каждого предыдущего из т-1 регистров 15, 17 и 19, кроме последнего, соединен соответственно с информационным входом каждого последующего, все выходы счетчика 13 и каждого из т-1 регистров 15, 17 и 19 сое- ,„.: е«- :и г. паевыми группами входов комму- 21 - 24 соответственно, вторые гсуппы входов которых соединены между „;у5сй и с выходами младших разрядов счетчика 9, и выходы каждого из коммутаторов 21-24 соединены с младшими адресными входами соответствующих ОЗУ 25 - 28, старшие адресные входы которых соединены между собой и с выходами старших разрядов счетчика 9, выходы каждого ОЗУ 25 28соединены с информациоными входами соответствующего одного из m регистров

29- 32, тактовые входы которых соединены с выходами соответствующих коммутаторов 14, 16, 18 и 20, выходы регистров 29 - 32 соединены с соответствующими входами ЦАП 33, выход которого соединен с входом фильтра 34, вход усилителя 36 подключен к выходу фильтра 34, а выход через аттенюатор 37 соединен с выходом устройства; управляющий вход генератора 1 соединен с выходом регистра 2, управляющий вход ключа 5 соединен с выходом регистра 6; вход установки счетчика 9 соединен с выходом регистра 10; входы установки счетчика 11 и дополнительного счетчика 13 соединены с выходами регистра 12; вход управления фильтра 34 соединен с выходом регистра 35; вход управления аттенюатора 37 соединен с выходом регистра 38.

Вычислительный блок 4 и блок 3 управления соединены между собой через ШУ 39, ША 40 и ШД 4, все информационные входы

регистров 2, 6 и 10, а также ОЗУ 25 - 28 и регистров 12, 35 и 38 обоих каналов 7 и 8 соединены через ШД 41 с вычислительным блоком 4, а их управляющие входы - с соответствующими управляющими выходами блока 3 управления. Управляющие входы коммутаторов 14, 16,18 и 20 и коммутаторов 21-24 обоих каналов 7 и 8 соединены между собой и с соответствующими выходами блока 3 управления.

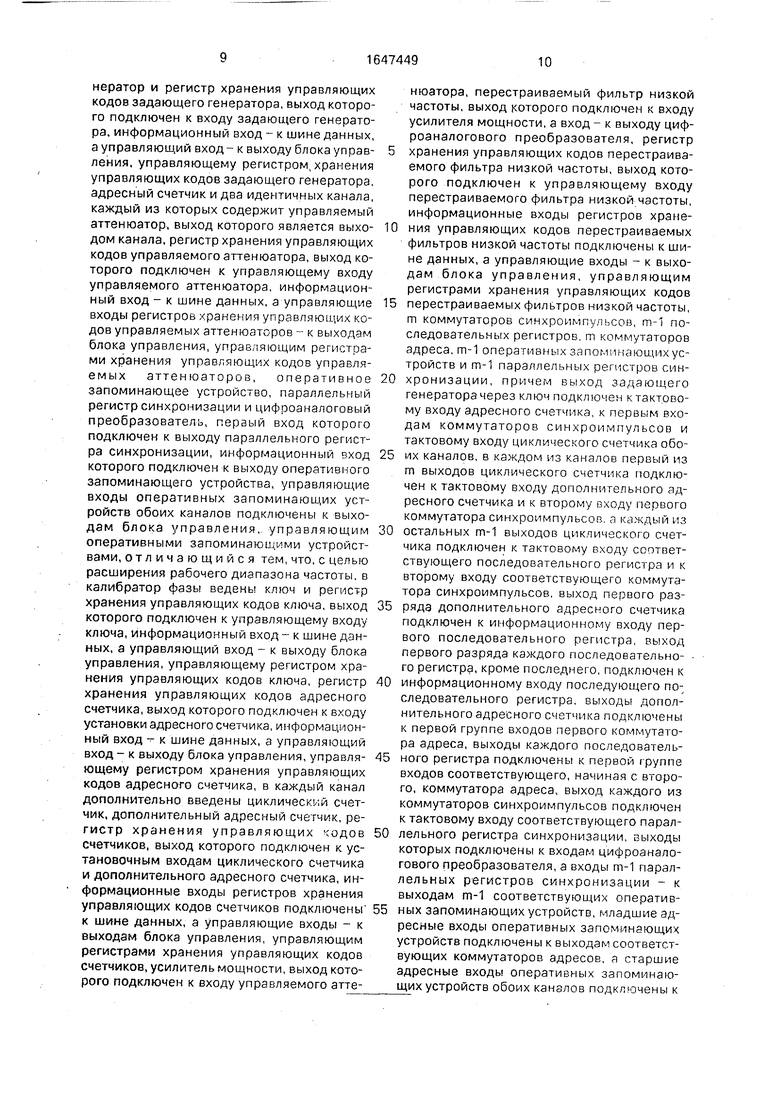

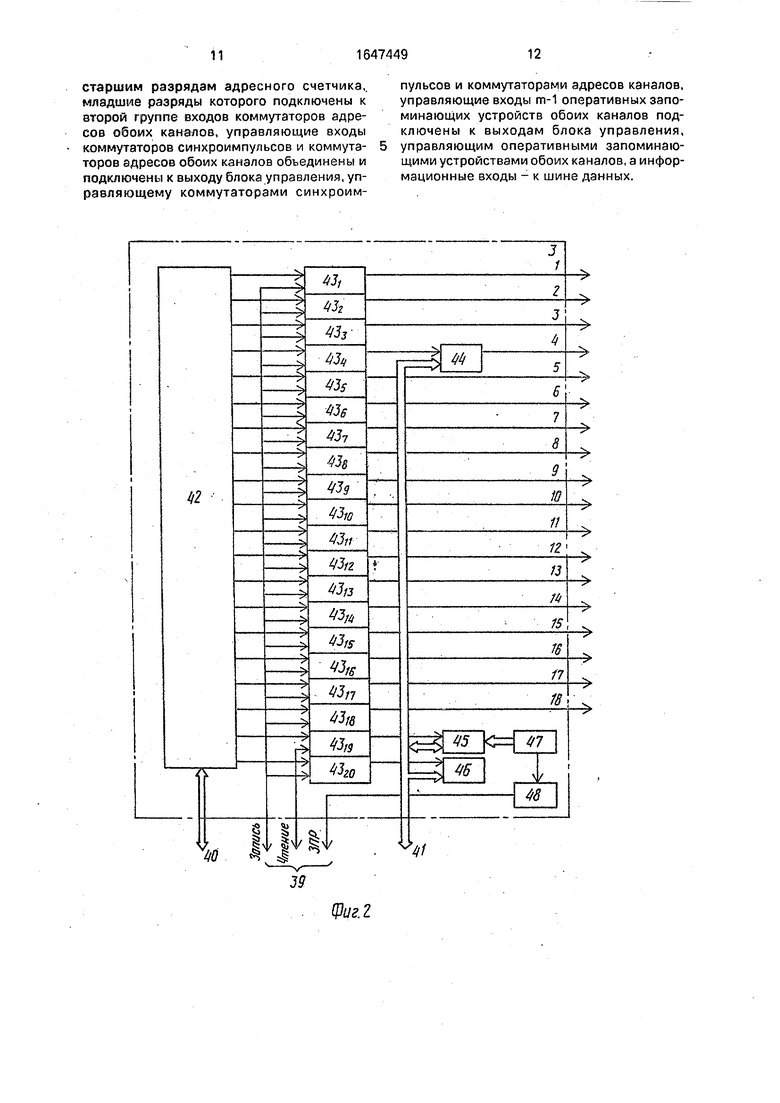

Блок 3 управления (фиг. 2) содержит дешифратор 42 адреса, логические элементы И 43.1 - 43,20, регистр 44 хранения, буферный регистр 45, блок 46 индикации, панель 47 управления, формирователь 48 сигнала Запрос прерывания. Входы дешифратора 42 подключены к ША 40, а выходы - к первым входам элементов И 43.1 - 43.20, вторые входы которых соединены с ШУ 39, выход элемента И 43.1 соединен с входом разрешения записи регистра 44, информационные входы которого соединены с ШД 41, Выходы элементов И 43.2 -43.18 и выход регистра 44 являются выходами блока 3 управления, выход элемента И 43.19 соединен с входом разрешения чтения регистра 45, выходы которого соединены с ШД 41 устройства, а информационные входы - с выходами панели 47, управляющий выход которой соединен с управляющим входом формирователя 48, выход которого соединен с ШУ 39; выход элемента И 43.20 соединен с входом разрешения записи блока 46 индикации, информационные входы которого соединены с ШД 41.

Вычислительный блок 4 (фиг. 3) содержит микропроцессорный модуль 49, постоянный запоминающий узел (ПЗУ) 50, схему 51 управления и запоминающий оперативный узел (ЗОУ) 52; адресные выходы микро- процессорного модуля 49 соединены с адресными входами ПЗУ 50, схемы 51 управления, ЗОУ 52 и ША 40 устройства, информационные входы/выходы микропроцессорного модуля 49 соединены с выходами ПЗУ 50, с входами/выходами ЗОУ 52 и с ШД 41 устройства; управляющие входы схемы 51 управления соединены с ШУ 39 устройства (с линиями Запись и Чтение), а ее управляющие выходы - с управляющими входами ПЗУ 50 и ЗОУ 52; вход Запрос прерывания микропроцессорного модуля 49 соединен с линией Запрос ШУ 39 устройства; выходы Запись и Чтение микропроцессорного модуля 49 соединены с соответствующими входами схемы 51 управления и соответствующими линиями ШУ 39 устройства.

Устройство работает следующим образом.

В блок 3 управления (с панели 47) вводят параметры, синтезирующих выходных сигналов - вид формы сигналов, значения их частоты, амплитуд первой и высших гармоник (для синусоидальной формы), значения начальных фаз всех гармоник (для синусоидальной формы.)По сигналу Запрос прерывания, формируемому в блоке 3 управления, вычислительный блок 4 считывает из регистра 45 блока 3 управления введенную информацию и анализиру ет ее. По результатам анализа определяются и формируются код выключения ключа 5 и управляющие коды установки необходимого значения частоты генератора 1, установки соответствующей полосы пропускания фильтра 34 и требуемого ослабления аттенюаторов 37. Эти коды по ШД 41 пересылаются соответственно в регистры 6, 2, 35 и 38 из вычислительного блока 4 с помощью блока 3 управления, в котором дешифрируются поступающие в него по ШД 40 коды адресов соответствующих регистров 2, 6, 10, 12, 35 и 38, формируются и подаются на их управляющие входы сигналы разрешения записи информации. При этом выключается ключ 5, устанавливаются требуемые значения частоты генератора 1, устанавливается соответствующая полоса пропускания фильтра 34 и устанавливаются необходимые значения ослабления аттенюаторов 37. Из четвертом выходе блока 3 управления устанавливается потенциал, обеспечивающий включение коммутаторов 21 -24 в режим передачи на входы ОЗУ 25 - 28 сигналов младших разрядов счетчика 9. После этого сначала на ШД 41 вычислительный блок 4 устанавливает код установки счетчика 9 в состояние, соответствующее адресу первых ячеек ОЗУ 25 - 28. затем на ША 40 устанавливается адрес регистра 10, по которому блок 3 управления формирует на одиннадцатом выходе сигнал разрешения записи, поступающий на управляющий вход регистра 10 и разрешающий запись в него информации, Далее вычислительный блок 4 устанавливает на ШД 41 информацию, которую необходимо занести в первую ячейку ОЗУ 25, а на ША 40 устанавливается адрес этого ОЗУ, по которому в блоке 3 управления формируется на соответствующем выходе сигнал разрешения записи информации в ячейку этого ОЗУ 25 - 28.

В такой последовательности записывается информация, соответствующая дискретным значениям выходного сигнала с требуемыми параметрами во все ячейки ОЗУ 25 - 28 каждого канала, количество которых соответствует числу отсчетов сигнала на его периоде.

Вследствие; ограниченности быстродействия используемых цифровых микросхем количество участков аппроксимации синтезируемого сигнала на высоких частотах обычно не превышает значения 12 - 24. В связи с этим целесообразно для упрощения устройства формировать текущий адрес используемых ячеек памяти ОЗУ 25 - 28 либо с помощью счетчика 9 (на нижних частотах, когда требуется обеспечить малый дискрет задания фазовых сдвигов и точное воспроизведение формы сигнала), либо с помощью соединенных цепочкой дополнительного счетчика 13 и регистров 15, 17 и 19 (на высоких частотах).

Поэтому, если введенное значение частоты превышает значение, соответствующее границе раздела диапазонов низких и высоких частот данного устройства, вычислительный блок 4 выключает счетчик 9 путем формирования и записи в регистр 10 кода установки младших разрядов счетчика 9 в нулевые, а старших разрядов - в нулевые или любые другие фиксированные состояния. На четвертом выходе блока 3 управления устанавливается потенциал, переключающий в обоих каналах коммутаторы 21 - 24 в режим передачи на адресные входы ОЗУ выходных сигналов дополнительного счетчика 13 и регистров 15,17 и 19. а коммутаторы 14, 16, 18 и 20 - в режим передачи выходных импульсов счетчика 11. Для уменьшения дискретности воспроизведения фазового сдвига в устройстве предусмотрена возможность дополнительно изменять фазовые сдвиги между сигналами путем управления начальными кодовыми состояниями счетчиков 11 и счетчиков 13 в обоих каналах 7 и 8. Использование регистров 15, 17 и 19 обеспечивает автоматически соответствие их начальных кодовых состояний кодовому состоянию счетчика 13 после прохождения счетных импульсов в течение первого периода синтезируемого сигнала. Управление начальными состояниями счетчиков 11 и 13 осуществляется с помощью регистра 12. После программирования ОЗУ 25 - 28 и установки начальных состояний счетчиков 11 и 13 в регистр 12 обоих каналов записываются нулевые коды (коды, не препятствующие работе счетчиков 11 и 13 обоих каналов), в регистр б записывается код, включающий ключ 5. С момента включения ключа 5 на тактовый вход счетчика 11 начинают поступать импульсы с генератора 1.

Появляющиеся поочередно на выходах счетчика 11 сигналы поступают на тактовые входы счетчика 13 и регистров 15, 17 и 19 и изменяют их кодовые состояния.

Текущие коды счетчика 13 и регистров 15,17 и 19 через коммутаторы 21-24 поступают на младшие адресные входы соответствующих ОЗУ 25 - 28, на старших входах

которых установлен неизменный код старших разрядов счетчика 9, который удерживается кодом установки счетчика в это состояние, записанным и хранящимся в регистре 10. По текущему адресу считывается

содержимое ячеек памяти ОЗУ 25 - 28 и синхронно, для устранения неизбежной асинхронности извлечения содержимого этих ячеек, переписывается в регистры 29 - 32 теми же тактовыми импульсами, которые

поступают на счетный вход счетчика 9, формирующего этот текущий адрес памяти. Цифровая информация с выходов регистров 29 - 32 поступает на входы ЦАП 33, где она преобразуется в аналоговый сигнал, который затем фильтруется фильтрами 34, усиливается усилителем 36 и поступает через аттенюатор 37 на выход устройства. Аналогично работает и второй канал устройства. При введении значения частоты выходных сигналов, соответствующего диапазону нижних частот устройства, вычислительный блок 4 после программирования ОЗУ 25 - 28 обоих каналов записывает в регистры 12 код установки нулевых начальных кодовых состояний счетчиков 11 и 13 обоих каналов. На четвертом выходе блока 3 управления сохраняется тот же потенциал, что и при программировании ОЗУ. Затем в регистр 10 записывается нулевой код, не препятствующий работе счетчика 9, а в регистр 6 заносится код включения ключа 5. В этом случае текущий адрес ячеек памяти формируется счетчиком 9, а на входы синхронизации регистров 29 - 32 поступают через коммутаторы 14, 16, 18 и 20 обоих каналов 7 и 8 тактовые импульсы с выхода ключа 5.

При любом изменении параметров выходных сигналов устройства в блоке 3 управления формируется сигнал Запрос

прерывания, по которому выполняются все описанные подготовительные операции и осуществляется перепрограммирование ОЗУ обоих каналов.

Преимуществом предлагаемого калибратора фазы является повышение рабочей частоты, уменьшение дискретности воспроизведения фазовых сдвигов на верхних частотах, уменьшение нелинейных искажений выходных сигналов.

Формула изобретения Калибратор фазы, содержащий блок управления и вычислительный блок, соединенные между собой шиной адреса, шиной данных и шиной управления, задающий reнератор и регистр хранения управляющих кодов задающего генератора, выход которого подключен к входу задающего генератора, информационный аход - к шине данных, а управляющий вход- к выходу блока управления, управляющему регистром, хранения управляющих кодов задающего генератора, адресный счетчик и два идентичных канала, каждый из которых содержит управляемый аттенюатор, выход которого является выходом канала, регистр хранения управляющих кодов управляемого аттенюатора, выход которого подключен к управляющему входу управляемого аттенюатора, информационный вход - к шине данных, а управляющие входы регистров /ранения управляющих кодов управляемых аттенюаторов - к выходам блока управления, управляющим регистоа- ми хранения управляющих кодов управляемых аттенюаторов, оперативное запоминающее устройство, параллельный регистр синхронизации и цифроаналоговый преобразователь, первый вход которого подключен к выходу параллельного регистра синхронизации, информационный вход которого подключен к выходу оперативного запоминающего устройства, управляющие входы оперативных запоминающих устройств обоих каналов подключены к выходам блока управления, управляющим оперативными запоминающими устройствами, отличающийся тем, что, с целью расширения рабочего диапазона частоты, в калибратор фазы ведены ключ и регистр хранения управляющих кодов ключа, выход которого подключен к управляющему входу ключа, информационный вход - к шине данных, а управляющий вход - к выходу блока управления, управляющему регистром хранения управляющих кодов ключа, регистр хранения управляющих кодов адресного счетчика, выход которого подключен к входу установки адресного счетчика, информационный вход - к шине данных, а управляющий вход - к выходу блока управления, управляющему регистром хранения управляющих кодов адресного счетчика, в каждый канал дополнительно введены циклический счетчик, дополнительный адресный счетчик, регистр хранения управляющих кодов счетчиков, выход которого подключен к установочным входам циклического счетчика и дополнительного адресного счетчика, информационные входы регистров хранения управляющих кодов счетчиков подключены к шине данных, а управляющие входы - к выходам блока управления, управляющим регистрами хранения управляющих кодов счетчиков, усилитель мощности, выход которого подключен к входу управляемого аттенюатора, перестраиваемый фильтр низкой частоты, выход которого подключен к входу усилителя мощности, а вход - к выходу циф- роаналогового преобразователя, регистр

хранения управляющих кодов перестраиваемого фильтра низкой частоты, выход которого подключен к управляющему входу перестраиваемого фильтра низкой частоты, информационные входы регистров хране0 ния управляющих кодов перестраиваемых фильтров низкой частоты подключены к шине данных, а управляющие входы - к выходам блока управления, управляющим регистрами хранения управляющих кодов

5 перестраиваемых фильтров низкой частоты, m коммутаторов синхроимпульсов, т-1 последовательных регистров m коммутаторов адреса, гп-1 оперативных запоминающих устройств и т-1 параллельных регистров син0 хронизации, причем выход задающего генератора через ключ подключен к тактовому входу адресного счетчика, к первым входам коммутаторов синхроимпульсов и тактовому входу циклического счетчика обо5 их каналов, в каждом из каналов первый из m выходов циклического счетчика подключен к тактовому входу дополнительного адресного счетчика и к второму входу первого коммутатора синхроимпульсов з каждый из

0 остальных т-1 выходов циклического счетчика подключен к тактовому входу соответствующего последовательного регистра и к второму входу соответствующего коммутатора синхроимпульсов, выход первого раз5 рядз дополнительного адресного счетчика подключен к информационному входу первого последовательного регистра, выход первого разряда каждого последовательного регистра, кроме последнего, подключен к

0 информационному входу последующего по; следовательного регистра, выходы дополнительного адресного счетчика подключены к первой группе входов первого коммутатора адреса, выходы каждого последователь5 ного регистра подключены к первой ipynne входов соответствующего, начиная с второго, коммутатора адреса, выход каждого из коммутаторов синхроимпульсов подключен к тактовому входу соответствующего парал0 лельного регистра синхронизации, выходы которых подключены к входам цифроанало- гового преобразователя, а входы т-1 параллельных регистров синхронизации - к выходам т-1 соответствующих оператив5 ных запоминающих устройств, младшие адресные входы оперативных запоминающих устройств подключены к выходам соответствующих коммутаторов адресов, ч старшие адресные входы оперативных запоминающих устройств обоих каналов подключены к

старшим разрядам адресного счетчика, младшие разряды которого подключены к второй группе входов коммутаторов адресов обоих каналов, управляющие входы коммутаторов синхроимпульсов и коммутаторов адресов обоих каналов объединены и подключены к выходу блока управления, управляющему коммутаторами синхроимпульсов и коммутаторами адресов каналов, управляющие входы т-1 оперативных запоминающих устройств обоих каналов подключены к выходам блока управления, управляющим оперативными запоминающими устройствами обоих каналов, а информационные входы - к шине данных.

teJ

Авторы

Даты

1991-05-07—Публикация

1988-07-01—Подача