1

Изобретение относится к области вычислительной техники и предназначено для преобразования многоразрядных чисел из одной системы счисления в другую.

Известен преобразователь двоичного кода в двоично-десятичный код градусов и минут, содержащий двоично-десятичный счетчик градусов, двоично-десятичный счетчик минут, двоичный счетчик, дешифратор, вентиль, второй дешифратор, выход которого соединен с двоичио-десятичным счетчиком градусов, а вход - со старп1ими разрядами двоичного счетчика .

Недостатками этого преобразователя являются преобразование только двоичного кода в двоично-десятичный код градусов и минут и малое быстродействие, определяемое временем .пересчета кода.

Наиболее близким техническим решением к изобретению является преобразователь кодов, содержащий входной регистр, информационные входы которого подключены к входным шинам, генератор импульсов, выходной сумматор, выходы которого соединены с выходными шинами, дешифратор, переключатель эквивалентов, первый вход которого соединен с управляющим входом выходного сумматора 2. Недостатком этого устройства является узкий класс рещаемых задач, так как устройство позволяет осуществлять преобразоватше кодов, имеющих только постоянную схему опроса разрядов входного кода.

Целью изобретения является расшнрение класса реишемых задач.

Поставленная цель достигается тем, что в предлагаемое устройство введены элемент И, дешифратор нуля, блок анализа, формирователь адреса, накопитель, причем второй, третий и четвертый выходы переключателя эквивалентов соединены соответственно с иервы.ми тремя управляюии1ми входам формирователя адреса, информанионпые входы выходного сумматора соединены с первой группой выходов накоп)1теля, входы которого

соединены с выходами формирователя адреса, а вторая группа выходов соединена с входами деншфратора, выходы которого соединены соответственно с четвертым управляющнм входом формирователя адреса, уиравляющим входом входного регистра и уиравляющими входами блока анализа, выход которого соедннен с информационным входом формирователя адреса, иятый управляющий вход которого подключен к выходу элемента

И, входы которого соединены соответственно с выходами генератора импульсов и дешифратора нуля, при этом в.чоды дешифратора нуля соединены соответственно с выходами входного регистра и информационными входами блока анализа.

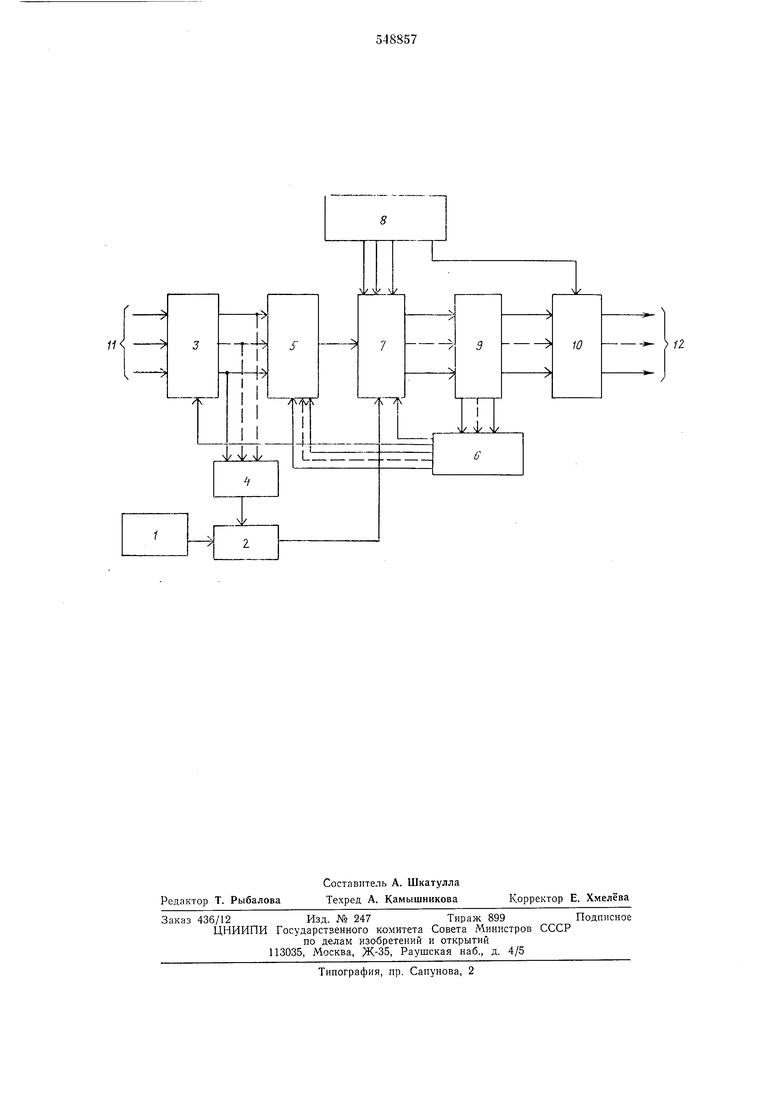

На чертеже показан предлагаемый преобразователь кодов.

Преобразователь содержит генератор 1 импульсов, элемент 2 И, входной регистр 3, дешифратор 4 нуля, блок 5 анализа, дешифратор 6, формирователь 7 адреса, переключатель 8 эквивалентов, накопитель 9, выходной сумматор 10, входные шины 11 и выходные шины 12.

Преобразователь кодов работает следующнм образом. Генератор 1 импульсов непрерывно вырабат з1вает последовательность импульсов, элемент 2 И открывается, и последовательность импульсов поступает на формирователь 7 адреса. Импульсы генератора 1 импульсов осуш,ествляют синхронизацию работы всего устройства, первоначальный адрес накопителя 9 формируется формирователе.м 7 адреса в соответствии с сигналами, пр11ходяш,ими от переключателя 8 эквивалентов.

Адрес начальной ячейки накопителя 9, установленный при помош,и переключателя 8 эквивалентов считывается первым тактирующим импульсом, поступающим от элемента 2 И л подается на накопитель 9. Считанный ио данному адресу код состоит из двух групп сигналов. Первая группа сигналов является информационной, подается на выходной сумматор 10 и для образования выходного кода, а вторая является командной, подается на дешифратор 6 и служит для управления процессом преобразования. Па выходе одной из шин дешифратора 6 в соответствии с кодом лоступившей команды появляется сигнал, который поступает на опрос одного или нескольких разрядов блока 5 анализа. Выходной сигнал блока 5 анализа в зависимости от входного кода, записанного в анализируемом разряде (или группе разрядов), устанавливает тот или другой адрес следующей ячейки в формирователе 7 адреса.

Вторым импульсом, .поступающим от генератора 1 импульсов, через элемент 2 И по очередному адресу, установленному в формирователе 7 адреса, считывается новая группа сигналов, состоящая также из информадионной части, которая подается на выходной .сумматор 10, и управляющей, постуиающей на дешифратор 6. Дальнейшее преобразование входного кода осуществляется автоматически по ирограмме, записанной в дополнительных запоминающих ячейках накопителя 9. После полного преобразования кода последней командой, поступающей из накопителя 9 на дешифратор 6, последний выдает сигнал, обнуляющий входной регистр 3 и формирователь 7 адреса. Дешифратор 4 нуля вырабатывает запрещающий сигнал на элемент 2 И. Импульсы от генератора 1 импульсов не .проходят через элемент 2 И, и схема нрекращает работу.

При преобразовании непозиционных кодов в иозицнониые и обратно последовательный опрос разрядов входного кода неприемлем. В этом случае необходимо осуществлять неоднократный опрос разрядов входного кода. С этой целью в предлагаемом преобразователе дешиф.ратор 6 соединен с выходными шинами дополнительных элементов накопителя. Это дает возможность производить поразрядный опрос преобразуемого кода в произвольном порядке в соответствии с кодом, поступающим из накопителя 9.

Использование элеменга И, дешифратора нуля, блока анализа формирователя адреса и накопителя .позволило значительно расщирить класс решаемых преобразователем задач и увеличить его универсальность.

Формула изобретения

Преобразователь кодов, содержащий входной регистр, информационные входы которого подключены к входным шинам, генератор импульсов, выходной сумматор, выходы которого соединены с выходными шинами, дешифратор, переключатель эквивалентов, первый выход которого соединен с управляющим входом выходного сумматора, отличаюЩИЙ.СЯ тем, что, с целью расширения класса решаемых задач, в него введены элемент И, дешифратор нуля, блок анализа, формирователь адреса, накопитель, причем второй, третий и четвертый выходы переключателя эквивалентов соединены соответственно с первыми тремя управляющими входами формирователя адреса, информационные входы выходного сумматора соединены с первой группой выходов накопителя, входы которого соединены с выходами формирователя адреса, а вторая группа выходов соединена с входами дешифратора, выходы которого соединены соответственно с четвертым управляющим входом формирователя адреса, управляющим входом входного регистра и управляющими входами блока анализа, выход которого соединен с информационным входом формирователя адреса, пятый управляющий вход которого подключен к выходу элемента И, входы которого соединены соответственно с выходами генератора импульсов и дешифратора нуля, при этом входы дешифратора нуля соединены соответственно с выходами входного регистра и информационными входами блока анализа.

Источники информации, принятые во внимание при эксиертизе

1.. св. № 277406, кл. G 06F 5/02, 1969,

2.Авт. св. № 331382, кл. G 06F 5/02, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для контроля параметров объекта | 1975 |

|

SU690498A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1973 |

|

SU521564A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

Авторы

Даты

1977-02-28—Публикация

1974-07-04—Подача