4

эо ел

DO

Изобретение относится к цифровой измерительной текинке и аналого-цифровой вычислительной технике и предназначено для преобразования напряжения в цифровой код.

По основному авт, св. W 863023 известен аналого-цифровой преобраэовтель, содержащий последовательно соединенные входной измерительный преобразователь, токозадакидйй резиотор, промежуточный измерительный пре образоватепь, выход которого с выходом .цифро-аналогового прв образоеателя , входом компаратора, первым выводом резистора нагрузки и входом ограничителя второй вывод резистора нагрузки и выход ограничителя подключен к общей точке аналого-цифрового преобразователя в вход входного измерительного преобразователя является входом ана/юго-цифро-j вого преобразователя 5 шина опорного напряжения подключена к входу блока коррекции погрешностей выход ко торого соединен с париям входом цифро-аналого8ого преобразователя, входные цифровые шины цифро-аналогового преобразователя, соединены с первыми выходными цифpoвы W1 шинами блока управления,первый вход которого сое динен с выходом компаратора р второй аход - сигнал Пуск, а вторые выходные цифровые шины являются выхо дом аналого-цифрового преобразователя l,

Недостатком этого преобразователя является относительно невысокое быстродействие, определяемое медленным разрядом паразитной

ч„ емкости суммирующего узла через сопротивление нагрузки«

Цель изобретения повышение быстродействия.

Цель достигается тем, что в аналого-цифровой преобразователь введены блок совпадений и коммутируемый источник тока, причем первый и второй входы блока совпадений соединены с дополнительными выходами бло,ка управления, третий вход - с выходом компаратора, а выход - с управляющим входом коммутируемого источника тока, выход которого подсоединен ко входу компаратора.

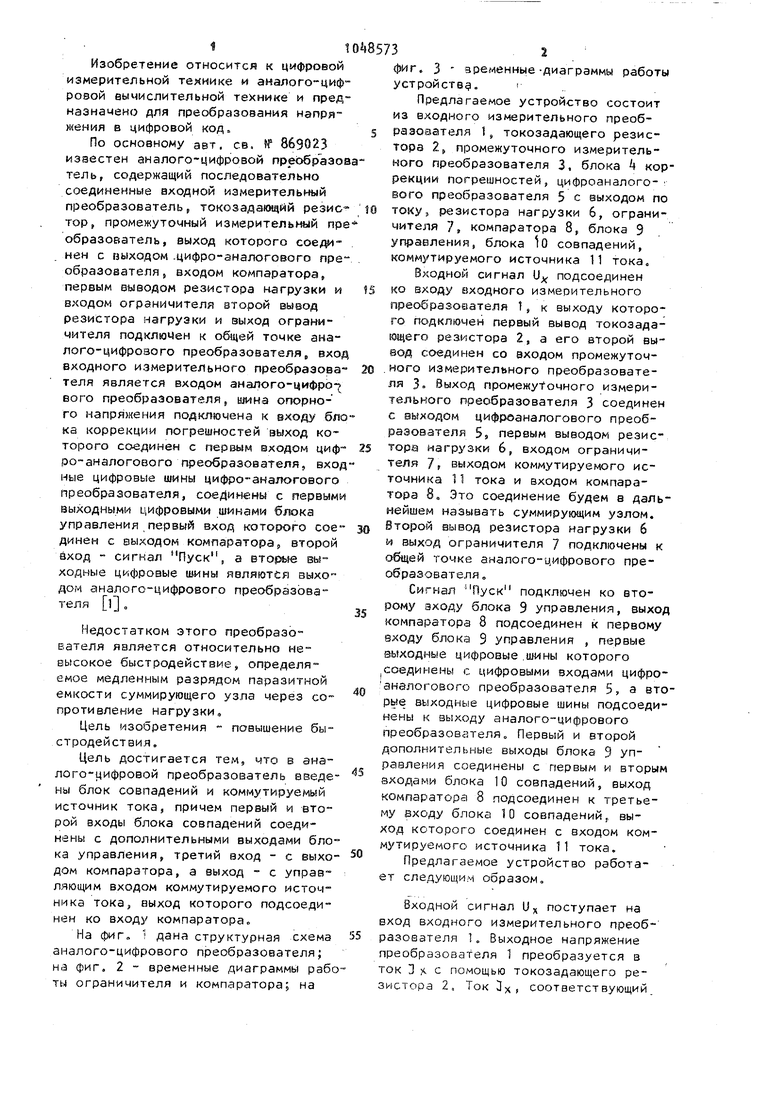

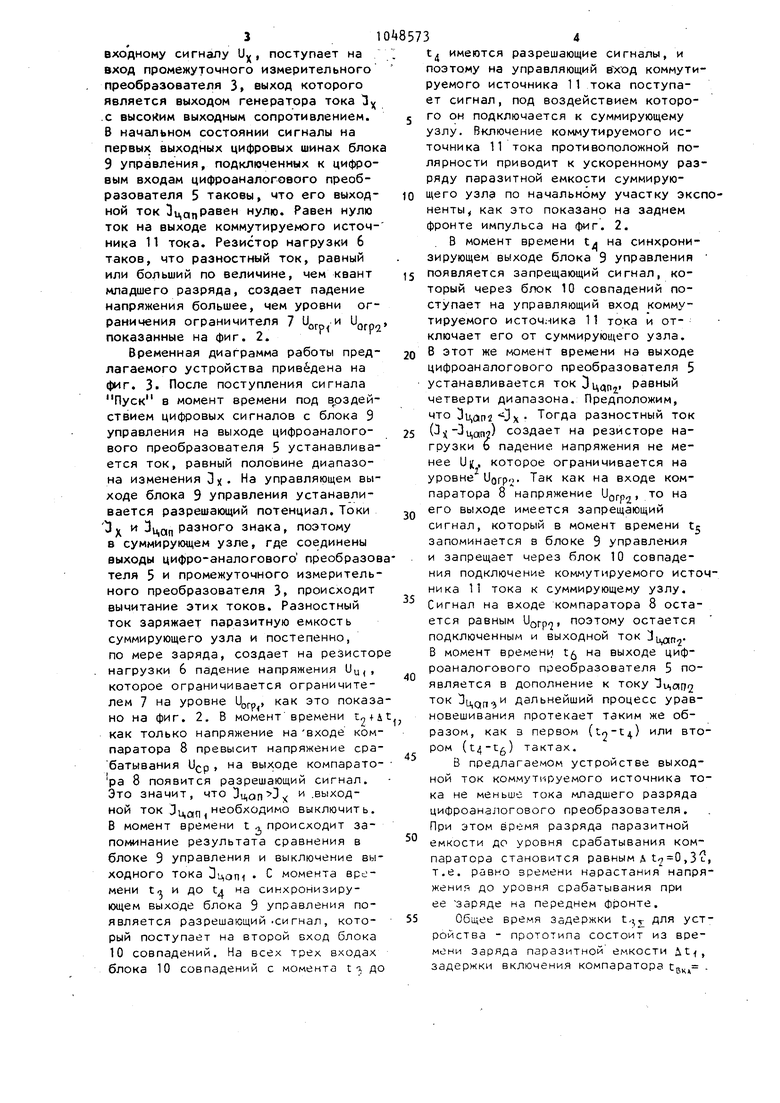

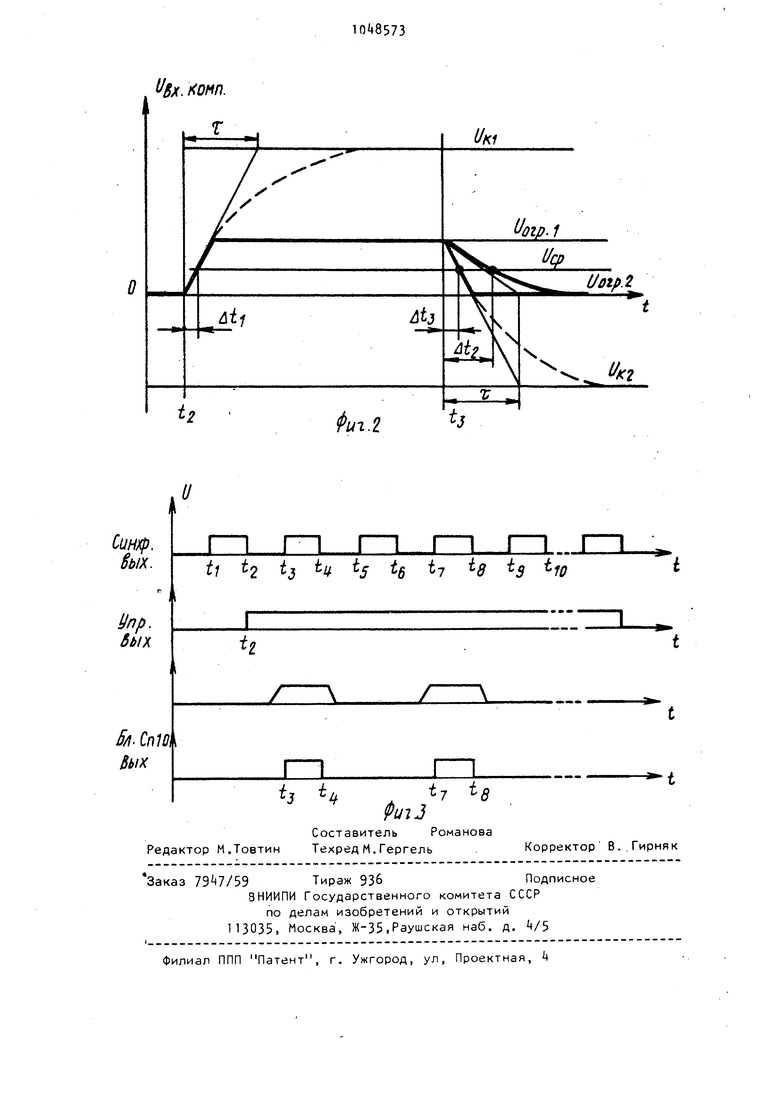

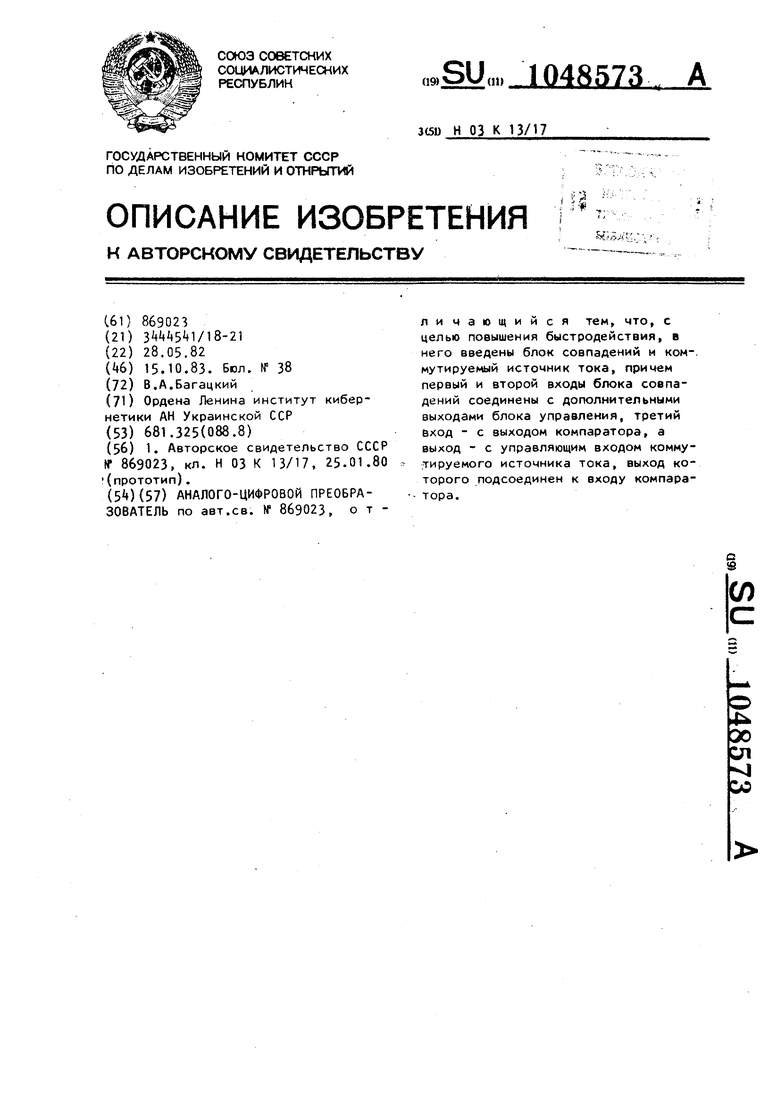

На фиг, 1 дана структурная схема аналого-цифр)ового преобразователя; на фиг, 2 - временные диаграммы работы ограничителя и компаратора; на

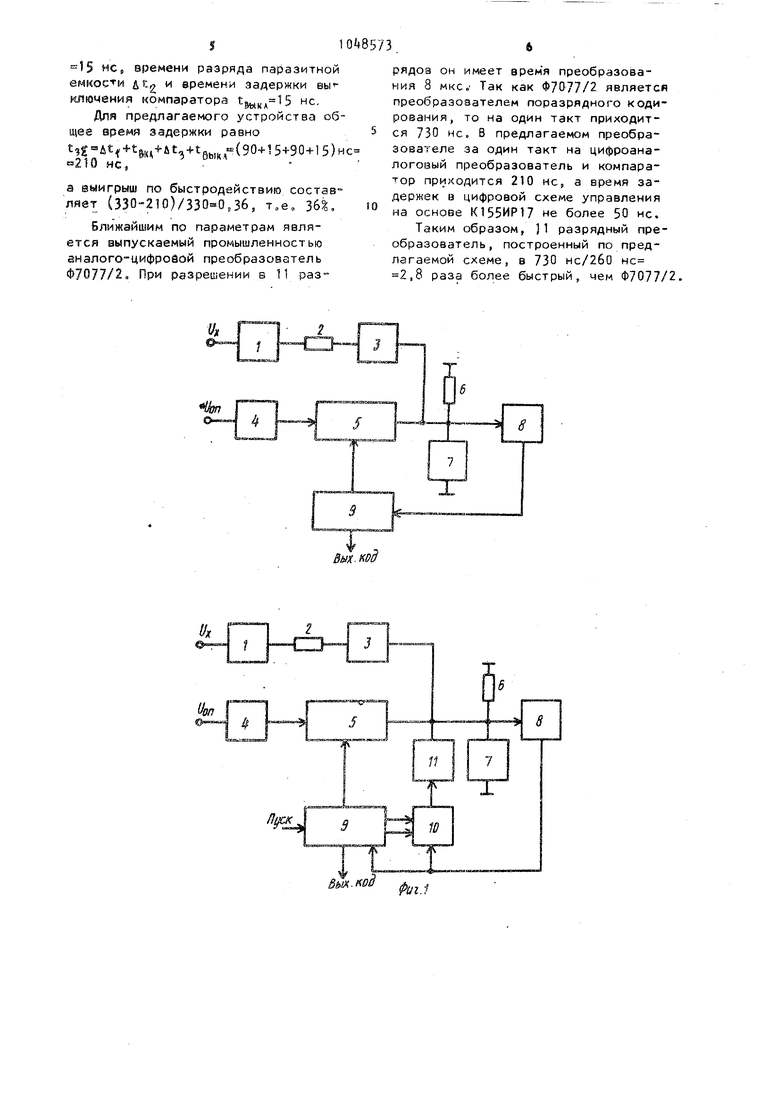

фиг. 3 временные-диаграммы работы устройству. 1

Предлагаемое устройство состоит из входного измерительного преобразователя 1, токозадающего резистора 2 промежуточного измерительного преобразователя 3, блока 4 коррекции погрешностей, цифроаналого-: вого преобразователя 5 с выходом по току, резистора нагрузки 6, ограничителя 7t компаратора 8, блока 9 управления, блока 1о совпадений, коммутируемого источника 11 тока.

Входной сигнал Uj. подсоединен ко входу входного измерительного Г1рео€ разое1ателя t, к выходу которого подклюмен первый вывод токозадающего резистора 2, а его второй вывод соединен со входом промежуточного измерительного преобразователя 3« Выход промежуточного измерительного преобразователя 3 соединен с выходом цифр&аналогового преобразователя 59 первым выводом резистора нагрузки 6, входом ограничителя 7р выходом коммутируемого источника 11 тока и входом компаратора 8, Это соединение будем в дальнейшем называть суммирующим узлом. Второй вывод резистора нагрузки б и выход ограничителя 7 подключены к общей точке аналого-цифрового преобразователя „

Сигнал Пуск подключен ко второму 1зходу блока 9 управления, выхо компаратора 8 подсоединен к первому входу блока 9 управления , первые вь ходные цифровые .шины которого Iсоединены с цифровыми входами цифроаналогового преобразователя 5, а втрые выходные цифровые шины подсоединены к выходу аналого-цифрового преобразователя Первый и второй дополнительные выходы блока Э управления соединены с первым и вторы sxoдa sи блока 10 совпадений, выход компаратора 8 подсоединен к третьему входу блока 10 совпадений, выход которого соединен с входом коммутируемого источника 11 тока.

Предлагаемое устройство работает следующим образом.

Входной сигнал U поступает на вход входного измерительного преобразователя U Выходное напряжение преобразователя 1 преобразуется в ток 1 ). с помощью токозадающего резистора 2, Ток Зх, соответствующий. входному сигналу Uj, поступает на вход промежуточного измерительного преобразователя 3, выход которого является выходом генератора тока .с высоким выходным сопротивлением. 8начальном состоянии сигналы на первых выходных цифровых шинах блок 9управления, подключенных к цифровым входам цифроаналогового преобразователя 5 таковы, что его выходной ток ЗцапР нулю. Равен нулю ток на выходе коммутируемого источника 11 тока. Резистор нагрузки 6 таков, что разностный ток, равный или больший по величине, чем квант младшего разряда, создает падение напряжения большее, чем уровни ограничения ограничителя 7 U и U , показанные на фиг. 2. Временная диаграмма работы предлагаемого устройства приведена на фиг. 3. После поступления сигнала Пуск в момент времени под воздействием цифровых сигналов с блока 9 управления на выходе цифроаналогового преобразователя 5 устанавливается ток, равный половине диапазона изменения Зх На управляющем выходе блока 9 управления устанавливается разрешающий потенциал. Токи и Зцап знака, поэтому в суммирую{цем узле, где соединены выходы цифро-аналогового преобразов теля 5 и промежуточного измерительного преобразователя 3, происходит вычитание этих токов. Разностный ток заряжает паразитную емкость суммирующего узла и постепенно, по мере заряда, создает на резистор нагрузки 6 падение напряжения U,, которое ограничивается ограничителем 7 на уровне , как это показа но на фиг. 2, В моментвремени t2tA как только напряжение на входе компаратора 8 превысит напряжение срабатывания 0 , на выходе компаратора 8 появится разрешающий сигнал. Это значит, что .выходной ток Зцдр необходимо выключить. В момент времени t 2, происходит запоминание результата сравнения в блоке 9 управления и выключение выходного тока Зцоп С момента времени ta и до t на синхронизирующем выходе блока 9 управления появляется разрешающий-сигнал, который поступает на второй вход блока 10 совпадений. На всех трех входах блока 10 совпадений с момента t-i до 1д имеются разрешающие сигналы, и поэтому на управляющий вход коммутируемого источника 11 тока поступает сигнал, под воздействием которого он подключается к суммирующему узлу. Включение коммутируемого источника 11 тока противоположной полярности приводит к ускоренному разряду паразитной емкости суммирующего узла по начальному участку экспоненты, как это показано на заднем фронте импульса на фиг. 2. В момент времени tj на синхронизирующем выходе блока 9 управления появляется запрещающий сигнал, который через блок 10 совпадений поступает на управляющий вход коммутируемого источника 11 тока и отключает его от суммирующего узла. В этот же момент времени на выходе цифроаналогозого преобразователя 5 устанавливается ток цдр,, равный четверти диапазона. Предположим, что Зцапг Тогда разностный ток р5(-3цдп2) создает на резисторе нагрузки о падение напряжения не менее UK, которое ограничивается на уровне Ugrpo, Так как на входе компаратора 8 напряжение Ugrp то на его выходе имеется запрещающий сигнал, который в момент времени tj запоминается в блоке 9 управления и запрещает через блок 10 совпадения подключение коммутируемого источника 11 тока к суммирующему узлу. Сигнал на входе компаратора 8 остается равным UQPP, поэтому остается подключенным и выходной ток i n-jВ момент времени t на выходе цифроаналогового преобразователя 5 появляется в дополнение к току Зцстг;2 ,и дальнейший процесс уравновешивания протекает таким же образом, как 3 первом () или втором (t4-tg) тактах. В предлагаемом устройстве выходной ток коммутируемого источника тока не меньше тока младшего разряда цифроаналогового преобразователя. При этом время разряда паразитной емкости до уровня срабатывания компаратора становится равным д ,3L, т.е. равно времени нарастаниянапряжения до уровня срабатывания при ее заряде на переднем фронте. Общее время задержки t.r для устройства - прототипа состоит из времени заряда паразитной емкости it, задержки включения компаратора ti;m S115 HCs времени разряда паразитной емкоси ,trt и времени задержки выкпючения компаратора t.j,15 не, Для предлагаемого устройства общее время задержки равно t f &t -4-tg +&t +tg,-(90+15+90-fl5)H 210 НС, а выигрыш по быстродействию составлйет (330-210)/330-0J6, т„е, 36%, Ближайшим по параметрам является выпускаемый промышленностью аналого-цифровой преобразователь Ф7077/2. При разрешении в 11 разрядов он имеет время преобразования 8 МКС. Так как Ф7077/2 является преобразователем поразрядного кодирования, то на один такт приходится 730 НС, В предлагаемом преобразователе за один такт на цифроаналоговый преобразователь и компаратор приходится 210 НС, а время задержек в цифровой схеме управления на основе К155ИР17 не более 50 не. Таким образом, 1 разрядный преобразователь , построенный по предлагаемой схеме, в 730 нс/2бО нс 2,8 раза более быстрый, чем Ф7077/2,

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| Фазометр | 1990 |

|

SU1797076A1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ МЕТАЛЛИЧЕСКИХ КОНСТРУКЦИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2339938C1 |

| Способ аналого-цифрового преобразования с контролем выходного кода и аналого-цифровой преобразователь с контролем выходного кода | 1985 |

|

SU1292180A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU869023A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (АЦП) | 2011 |

|

RU2477564C1 |

%

Вш. Kffff

Авторы

Даты

1983-10-15—Публикация

1982-05-28—Подача