. жит сдвигающий регистр; запоминающий регистр, элементы ИЛИ. входы которых поразрядно соединены с информационными выходами сдвигающего и запоминающего регистров соответственно, а Выходы - с входами запоминающего регистра, два выходных запоминающих регистра, информационные входы которых попарно соединены с выходами запоминающего регистра, а тактовый вход первого из них соединен с информационным входом сдвигающего регистра, три элемента совпадений , первые входы которых соединены с тaктoвы I входом сдвигающего регистра, второй вход первого элемента совпадения соединен с i (где i 0 ,1,2,. , . ,i) выходом сдвигающего регистра, вторые входы второго и третьего элементов совпадений соединены с выходом последнего разряда сдвигающего регистра, а выходы - соответственно с входом установки в нулевое состояние запоминающего регистра и тактовым входом первого выходного запоминающего регистра, и тактовым входом второго выходного запоминающего регистра, и три триггера, входы установки в единичное состояние первого и второго из которых соединены с нулевым выходом сдвигающего регистра, второй вход установки в нулевое состояние первого триггера соединен с первым информационным выходом сдвгающего регистра, счетный вход второго триггера соединен с выходом третьего элемента совпадения, а вь1ход - с входом режима работы сдвигаЮ1цего регистра, счетный вход третьего триггера соединен с выходом по.следнего разряда сдвигающего регистра, а выходы - соответственно с третьими входами второго и третьего элементов совпадений, при этом выходы элементов ИЛИ соединены с первым входом блока формирования кода, второй выход которого соединен с певыми входами триггеров, второй выход первого триггера соединен с третим выходом.блока Нормирования кода, В1ЛХОДЫ первого и второго вр 1ходных запоминающих регистров соединены с информационными выходными шинами, а первые входы установки в нулевое со стояние триггеров, тактовые входы сдвигающего и запоминающего регистров соединены соответственно с первым, вторым и третьим входами блока Нормирования кода,.

4. Преобразователь по п.1, о т личающийся тем, что в нем устройство пуска содержит формирователь импульсов, три элемента совпадений, первые входы которых соединен с выходом формирователя импульсов, а второй Вход второго элемента совпа.дения соединен с вторым входомтретьего элемента совпадения, первый триггер, счетный вход которого .соединен с выходом Формирователя импульсов, а выходы соединены с вторыми вхддами первого и второго элементов совпаде ний, и второй триггер, счетный вход которого соединен с выходом третьего элемента совпадения, а выходы соединены соответственно с управляющим входом Формирователя импульсов и входом установки нуля первого триггера, при этом вход Формирователя импульсов соединен с тактовым входом устройства пуска, третий и четветый входы второго элемента совпадения соединены соответственно с управляющим и первым входами устройства пуска, третий вход третьего элемента совпадения соединен с дополнительным управляющим входом устройства пуска, выходы первого и второго элементов совпадений соединены соответственно с первым и вторым выходами устройства пуска, выход второго триггера соединен с третьим выходом устройства пуска, а вход установки единицы второго триггера и выход третьего элегданта совпадения соединены соответственно с шинами Пуск и Конец преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ РАЗНОСТИ ФАЗ | 1973 |

|

SU370720A1 |

| Аналого-цифровой преобразователь сАВТОМАТичЕСКОй КОРРЕКциЕй Нуля | 1979 |

|

SU805490A1 |

| НОНИУСНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2128853C1 |

| Анализатор импульсных моментовлиНЕйНыХ СиСТЕМ АВТОМАТичЕСКОгОРЕгулиРОВАНия | 1979 |

|

SU847283A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ ОБЪЕКТА | 1991 |

|

RU2100775C1 |

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

1. АНАЛОГО-ЦИФРОВОЙ- ПРЕОБРАЗОВАТЕЛЬ, содержащий цифроаналоговый преобразователь. сравнивающий блок, выполненный в виде последова- .тельно соединенных суммирующего усилителя и компаратора, программирующий блок выполненный в виде последовательно соединенных устройства пуска и блока «нормирования кода, дешифратор и генератор импульсов, выход которого соединен с тактовым входом устройства пуска, управляющий вход которого соединен с выходом компаратора сравниваклцегр блока, а первый, второй и третий выходы блока формирований кода соединены соответственно с входами диЛроаналогового преобразова.теля, дешигЬратора и с первым входом устройства пуска, о тл и ча ю щи йся тем, что, с целью повышения точности, в него .введены нониусный блок, два ключа, резистор и шифратор, причем первый вход и первый выход нониусного блока соединены соответственно с выходом и неинвертирующим входом суммирующего усилителя, второй вход - с выходом цифроаналогового преобразователя -и входом первого ключа, второй выход через резистор-с инвертирукицим входом cyм 1иpyющeгo усилителя, вход шифратора соединен с выходом дешифратора, управляющий выход которого соединен с дополнительным управляющим входом устройства пуска, программирующего блока, первый, второ: и третий выходы шкЛратора соединены с первым, вторым и третьим управляющими входами нониусного блока, четвертый и пятый выходы шил ратора соединены соответственно с управляю1пими входамипервого и второго ключей, выходы которых соединены с входами cy 1миpyюneгo усилителя, а информационный .вход второго ключа соединен с входной щиной .преобразователя. - . 2. Преобразователь по п.1, о т и чающийся. тем, что в нем нониусный блок содержит операцион-ный усилитель с отрицательно.й обрат.ной связью, два весовых резистора,(соединенных первыми выводами с ин- вертируняцим .входом операционного усилителя, блок выборки и хранения, вход которого соединен с выходом операционного усилителя, и четыре ключа, причем входы первого и второго ключей, выходы которых подключены к первому и второму выходам нониусного блока,соединены соответственно с выходами блока выборки и хра нения и операционного усилителя, выходы третьего и. четвертого ключей, входы которых подключены к первому и второму входам нониусного блока, .соединены соответственно с вторыми выводами весовых резисторов, а управляю1цие входы первого и второго ключей, блока выборки и хранения и третьего ключа и управляющий вход четвертого ключа соединены соответствен.но с первым, вторым и третьим управляющими входами нониусного блока. . 3. Преобразователь по п.1, о т личаю. щийся тем, что в . нем блок формирования кода содер

1

Изобретение относится к автоматике, телемеханике и вычислительной тенике и может быть использовано в различных информационных измерительных системах с преобразованием анапоговой информации в дискретную.

Известны аналого-цифровые преобразователи поразрядного кодирования, содержащие в цепи обратной связи циФроаналоговыГ преобразователь lH.

Погрешность квантования по уровню в них определяется числом разрядов цифроаналогового преобразователя, который является сложным элек-. тронным устройством, состоящим из большого числа различных компонентов и схемных элементов, Таким образом, уменьшение погрешности квантования по уровню приводит к увеличению числа разрядов цифроаналогового поеобразователя. т.е. к его усложнению, а

следовательно, и к усложнению всего аналого-дифрового преобразователя в целом, .

Известен аналого-цифровой преобразователь, содержащий циЛроаналоговый преобразователь, сравнивающий блок, выполненный в виде последовательно соединенных су У1мирующего усилителя и компаратора, программирующий блок, выполненньай в виде последовательно соединенных устройства пуска и блока формирования кода, дешифратор и генератор импульсов, выход которого соединен с тактовым входом устройства пуска, управляющий вход которого соединен с выходом компаратора сравнивающего блока, а первый, второй и третий выходы блока Нормирования кода соединены соответственно со входами цифроаналогового преобразователя , дешифратора и с первым входом устройства пуска С2;3.

Недостатком этого преобразователя ;является то, что уменьшение погреш|ности квантования по уровню достигается путем увеличения числа разрядов цифроаналогового преобразователя, (Т.е. путем усложнения как циЛроаналогового преобразователя, так и всегд устройства в целом, а также пониженная точность преобразования за счет дрейфа нуля суммирующего усилителя .

т.ель изобретения - повышение точности.

Поставленная цель достигается тем что в аналого-цифровой преобразователь , содержащий цифроаналоговый преобразователь, сравнивающий блок, выполненныйв виде последовательно соединенных суммирующего усилителя и компаратора, программирующий блок, выполненный в виде последовательно соединенных устройства пуска и блока формирования кода, дешифратор и генератор импульсов, выход которого соединен с тактовым входом устройства пуска, управляющий вход которого соединен с выходом компаратора сравнивающего блока, а первый, второй и третий выходы блока Формирования кода соединены соответственно с входами цифроансшогового преобразователя, дешифратора и с первым входом уст-; ройства пуска, введены нокиусный блок,.два ключа, резистор и шифратор причем первый вход и первый выход нониусного блока соединены соответственно с выходом и неинвертирующим входом суммирующего усилителя, второй вход - с выходом цифроаналогового преобразователя и входом первого ключа, второй выход через резистор с инвертирующим входом суммирующего усилителя, вход шифратора соединен с выходом дешифратора, управляющий выход которого соединен с дополнительным управляющим входом устройства пуска программирующего блока, первый, второй и третий выходы шифратора соединены с первым, вторым и третьим управ шющими входами нониусного блока, четвертый и.пятый выходы шифратора соединены соответственно с управляющими входами первого и второго ключей, выходы которых соединены с входами суммирующего усилите- ля, а информационный вход второго

0 ключа сЪединен с входной шиной преобразователя .

Нониусный блок содержит операционный усилитель с отрицательной обратной связью, два весовых резистора,

5 соединенных первыми выводами с инвертирующим входом операционного усилителя, блок выборки и хранения, вход которого соединен с выходом операционного усилителя, и четыре

Q ключа, причем входы первого и второго ключей, выходы которых подключены к первому и второму выходам нониусного блока, соединены соответственно с выходами блока выборки и хране5 ния и операционного усилителя, выходы третьего и четвертого ключей, входы которых подключены к первому и второму входам нониусного блока, соединены соответственно с вторыми выводами весовых резисторов, а уп0равляющие входы первого и второго ключей, блока выборки и хранения и третьего ключа и управляющий вход четвертого ключа соединены соответственно с первым, вторым и третьим

5 управляющими входами-нониусного блока.- .

Блок Формирования кода содержит сдвигающий регистр, запоминающий регистр, элементы ИЛИ, входы которых

0 поразрядно соединены с информационными выходами сдвигающего и запоминающего регистров соответственно, а выходы - с входами запоминаю1цего регистра, два выходных запоминающих

5 регистра, информационные вхоДы которых попарно соединены с выходами запоминающего регистра, а тактовый вход первого из них соединен с ийформационным входом сдвигающего регистра, три элемента совпадений,первые

50

входы КОТОРЫХ соединены с тактовым входом сдвигающего регистра, второй вход первого элемента совпещения соединен с i (где 0,1/2,,..,i) выходом сдвигающего регистра,, вторые

55 входы вто&ого и третьего элементов совпадений соединены с выходом последнего разряда сдвигающего регистра, а выходы - соответственно.с входом установки в нулевое состоя60 ние запоминающего регистра и тактовы входом первого выходного запоминающего регистра,и тактовым входом второго выходного запоминающего регистра,и три .триггера, выходы установки в единичное

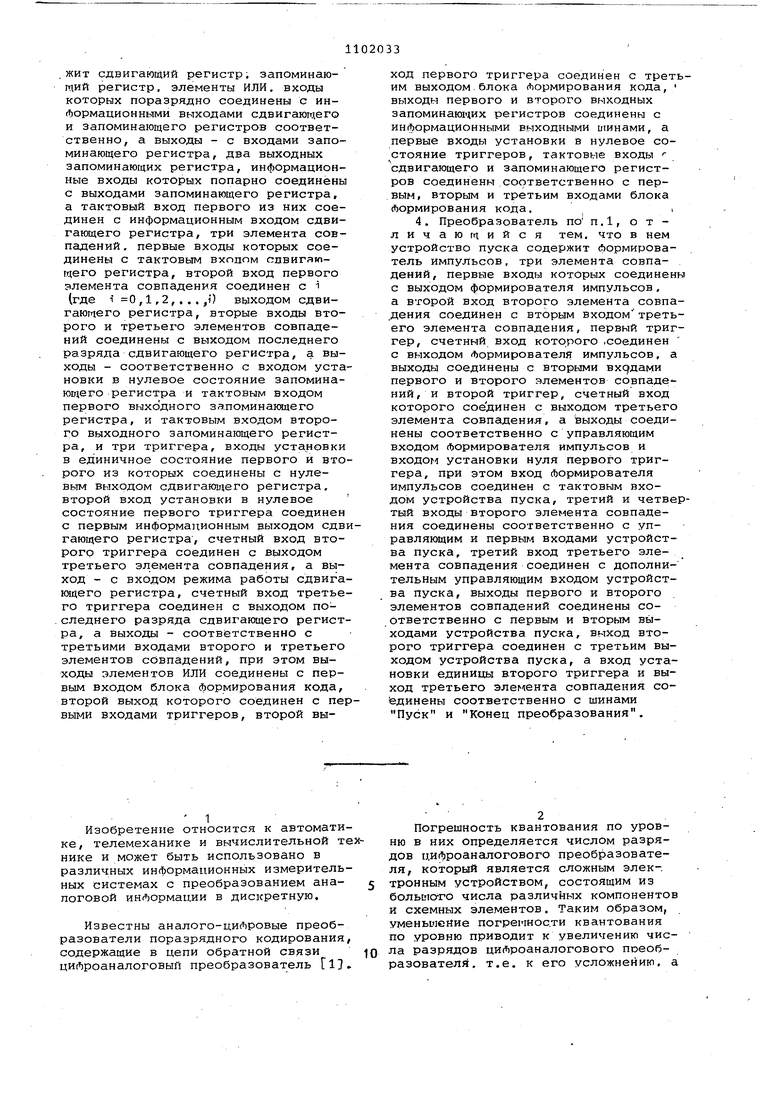

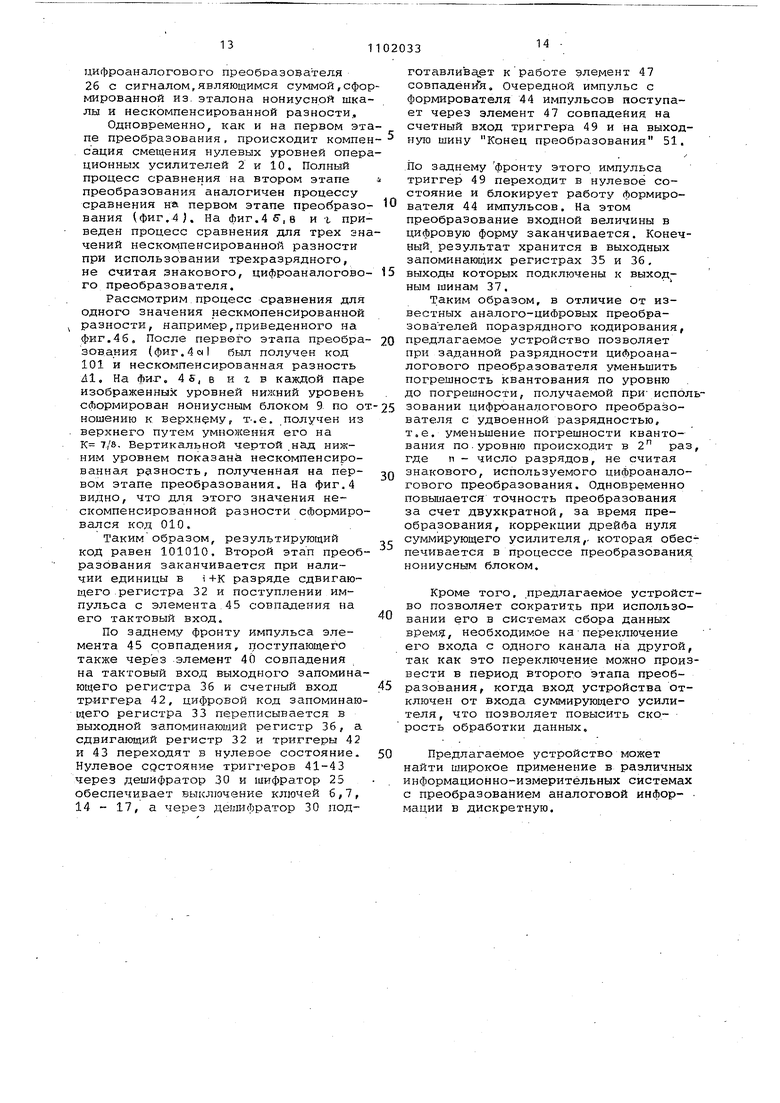

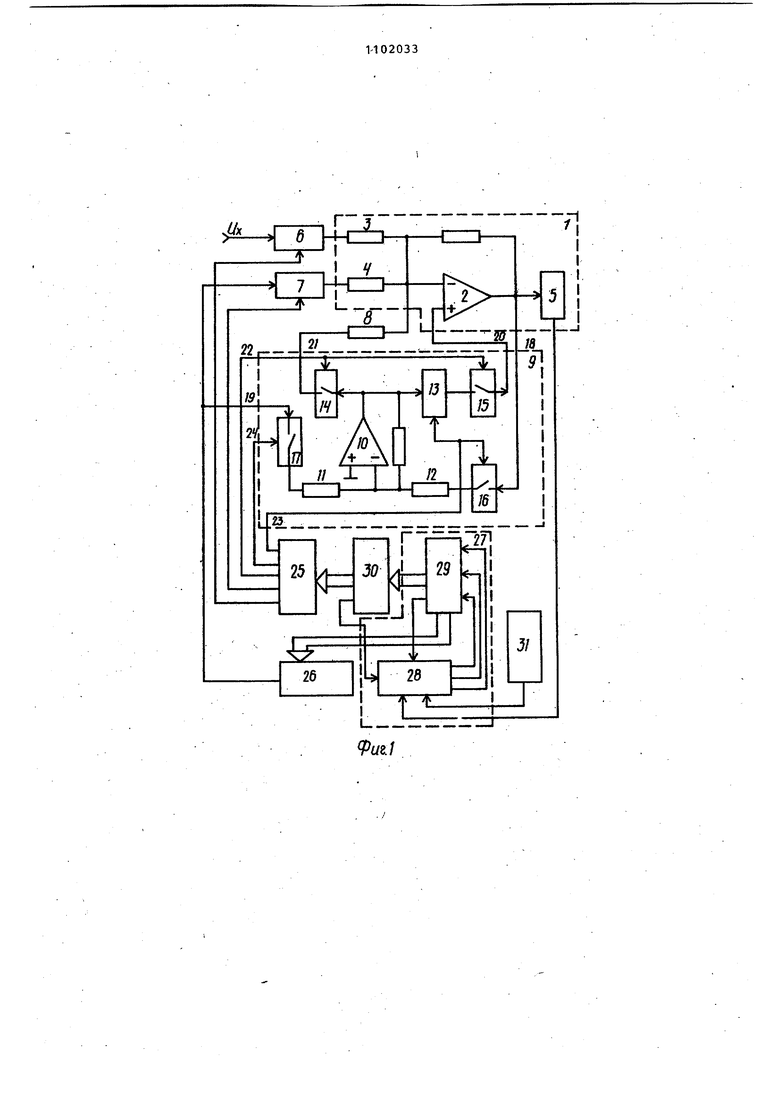

65 состояние первого и второго из которых соединены с нулевым выходом сдвигающег регистра,второй вход установки в нулевое состояние первого-триггера соединён с первым информационным выходом сдвигающего регистра, счетный вход второго триггера соединен с выходом третьего элемента совпадения, а выкод - с входом режима работы сдвигаю чего регистра, счетный вход третьего триггера соединен с выходом последнего разряда сдвигающего регистра, а выходы - соответственно с третьим входами второго и третьего элементов совпадений, при этом выходы элементов ИЛИ соединены с первым входом блока формирования кода, второй выход которого соединен с первыми выхо дами триггеров , второй выход первого триггера соединен с третьим выходом блока сЬормирования кода, выходы, первого и второго выходных запоминающих регистров соединены с ин Лормационными выходными шинами, а первые входы установки в нулевое со .стояние триггеров, тактовые входы сдвигающего и запоминающего регистров соединены соответственно с первым, вторым и третьим входами блока формирования кода. Устройство пуска содержит формиро ватель импульсов, три элемента совп дений, первые входы которых соединены с выходом )Ормирователя импульсов а второй вход второго элемента совпадения соединен с вторым входом третьего элемента совпещения, первый триггер, счетный вход которого соединен с выходом формирователя импуль сов, а выходы соединены с вторыми входами первого и второго элементов совпадений, и второй триггер, счетный вход которого соединен с выходом третьего элемента совпадения, а выходы соединены соответственно с управляющим входом формирователя импульсов и входом установки нуля первого триггера, при этом вход формиро вателя импульсов соединен с тактовым входом устройства пуска, третий и четвертый входы второго элемента совпадения соединены соответственно с управляющим и первым входами устройства пуска третий вход третьего элемента совпадения соединен с дополнительным управляющим входом устройства пуска, ,вых6дь1 первого и второго элементов совпадений соединены соответственно с первым и вторым выходами устройства пуска, выход второго триггера соединен с третьим выходом устройства пуска, а вход установки единицы второго триггера и выход третьего элемента совпадения соединены соответственно с шинами Пуск и Конец преобразования. На фиг.1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока формирования кода; на Лиг.З - схема устройства пуска; на фиг.4 - временные диаграммы. Устройство содержит сравнивающий блок 1, состоящий из суммирую1(его усилителя 2 с отрицательной обратной связью, весовых резисторов ,3 и 4 и компаратора 5, ключи 6 и 7,. выходы которых соединены с весовыми резисторами 3 и 4,резистор 8, нониусный блок 9, состоящий из операционного усилителя 10 с отрицательной обратной связью, весовых резисторов 11 и 12, соединенных с инвертирующим входом операционного усилителя 10, блока 13 выборки и хранения, четырех ключей 14 - 17, двух входных иин 18 и IS, . первая из которых соединена с выходом су1 1мирующего усилителя 2, двух выходных шин 20 и 21, первая из которых соединена с неинвертирующим входом, а вторая через резистор Я с инвертирующим входом суммирующего усилителя 2, и трех управляющих шин 22 - 24, первая из которыхсое-динена с управляющими входами ключей 14 и 15, вторая соединена с управляющими входами блока 13 выборки и xpaнeн я и ключа 16, а третья соединена с управляющим входом ключа 17, при этом выход операционного усилителя 10 соединен с входами блока 13выборки и хранения и ключа 14, выход которого соединен с выходной шиной 21, вход кетюча 15 соединен с выходом блока 13 выборки и хранения, а выход соединен с выходной шиной 20, входы ключей 16 и 17 соединены соответственно с входными шинами 18 и 19, а выходы - с весовыми резисто-г рами 11 и 12, шифратор 25, выходы которого соединены с управляющими шинами 22 - 24 нониусного блока 9 и управляющими входами ключей б и 7, циброаналогбвый преобразователь 26, выход которого соединен с входной шиной 19 нониусного блока 9 и входом ключа 7, программирукяпий блок 2 7, состоящий из устройства 28 пуска, первый управляющий вход которого соединен с выходом компаратЬра 5, и блока 29 Формирования кода, два тактовых входа и один управляющий вход которого соединены с выходами устройства 28 пуска, первый выход - с входом цифроаналогового преобразователя 26, третий выход - с вторым управляющим входом устройства 28 пуска, дешифратор 30, входы которого соединены с вторым выходом блока 29 формирования кода, а выходы соединены с входами шифратора 25 и управляющим входом устройства 28 пуска, и генератор 31 импульсов, выход которого сбединен с входом устройства 28 пуска программирующего блока 27. Блок формирования кода (фиг.2) содержит сдвигающий регистр 32, запоминающий -регистр 33, блок 34 элементов ИЛИ, входы которых поразрядно соединены с информационными выходами сдвигающего и запоминающего регистров 32 и 33, а выходы соединены с входами запоминающего регистра 33 и цифроаналогового преобразователя 26, выходные запоминающие регистр 35 и 36,-информационные входы которых попарно соединены с выходами запоминающего регистра 33, тактовый вход первого из них соединен с информационным входом сдвигающего регистра 32, а выходы соединены с ин формационными выходными шинами 37 аналого-цифрового преобразователя, три элемента совпадения 38, 39 и 40 первые входы которых соединены с так товым входом сдвигающего регистра 32, второй вход элемента совпадения 38 соединен с выходом сдвигающег регистра 32, вторые входы элементов совпадений 39 и 40 соединены с выходом последнего разряда сдвигающего регистра 32, а выходы соединены соответственно с входом установки в нулевое состояние запоминающего регистра 33, и с тактовыми входами выходных запоминающих регистров 35 и 36, и три триггера 41 - 43, входы установки в нулевое состояние которых объединены, входы установки в единичное состояние триггеров 41 и 42 объединены и соединены с нулевым выходом сдвигающего.регистра 32, второй вход установки в нулевое состояние триггера 41 соединен с первым информационным выходом сдвигающего регистра, счетный вход триггера 42 соединен с выходом элемента 40 совпадения, а выход соединен с входом режима работы сдвигающего регист ра 32, счетный вход триггера 43 соединен с выходом последнего разряда :двигающего регистра 32, а выходы оединены с третьими входами элеентов 39 и 40 совпадений, при йтом ыходы триггеров 41 - 43 соединены ; входами дешифратора 30. Устройство пуска (фиг.З} содержит Формирователь 44 импульсов, вход которого соединен с выходом генерато ра 31 импульсов, три элемента совпадения .45 - 47, первые входы которых соединены с выходом формирователя 44 импульсов, второй вход элемента 46 совпадения соединен с вторым входом элемента 47 совпадения, триггер 48, счетный вход которого соединен с выходом формирователя 44 импульсов а выходы соединены с вторыми входами элементов 45 и 46 совпадений, и триггер 49, счетный вход которого со единен с выходом элемента 47 совпаде ния, а выходы - с управляющим входом Формирователя 44 импульсов и с входами установки-нуля триггеров 41 -. 43 и 48, при этом третий и четвертый входы элемента, 46 совпадения соединены соответственно с выходом компаратора 5 и вторым йыходом триггера 41, третий вход элемента 47 совпадения соединен с отдельным выходом дешифратора 30, выходы элементов 45 и 46 совпадений соединены соответственно с тактовыми входами сдвигакяцего регистра 32 и запоминающего регистра 33, вход установки единииы триггера 49 соединен с шиной Пуск 50, а выход элемента 47 совпадения соединен с выходной шиной Конец преобразования 51. Устройство работает следующим образом, В исходном состоянии формирователь 44 импульсов закрыт, триггеры 41 - 43, 48 и 49 находятся в нулевом состоянии, ключи 6,7, 14-17 закрыты, сдвигающий регистр 32 находится в режиме Запись. Выходной аналоговый сигнал поступает на вход ключа 6. При поступлении на шину 50 сигнала Пуск триггер 49 переходит в единичное состояние, открывая тем самым формирователь 44 импульсов и разрешая работу триггеров 41 - 43 и 48. Последовательность импульсов-с . генератора 31 импульсов через формирователь 44 импульсов начинает поступать на входы элементов 45-47 совпадений и счетный вход триггера 48. Первый импульс из этой последовательности проходит через элемент 45 совПсщения и поступает на тактовьгй вход сдвигающего регистра 32. По заднему фронту импульса триггер 48 переходит в единичное состояние, подготавливая тем самым прохождение следующего импульса через элемент 46 совпадения, а в младший разряд сдвигающего регистра 32 записывается единица, в остальные жеразряды записываются нули. (Подключение информационного входа младшего разряда к шине питания, а информационных входов .остальных разрядов к нулевой шине на фиг.2 не показано |. При этом триггеры 41 и 42 переходят в единичное состояние. Триггер 42 в единичном состоянии переводит сдвигающий регистр 32 из режима Запись в оежим Сдвиг, триггер 41 блокирует работу элемента. 46 совпадения,а через дешифратор 30 и .шиЛратор 25 они открывают ключ 16 vi переводят в режим Выборка блок 13 выборки и хранения, на котором начинается процесс запоминания напряжения, обусловленного смещенияг.и нулевых уровней операционных усилителей 2 и 10. Второй импульс из последовательности импульсов с генератора 31 импульсов через элементы 45 - 47 совпадения не проходит, так как элемент 45 совпадения заблокирован триггером 48, элемент 46 совпадения - триггером 41, а элемент 47 совпадения - дешиЛрато ром 30. П.О заднему фронту второго импульса триггер 48 переходит в исходное состояние, подготавливая к работе элемент 45 совпадения. Третий импульс из последовательности импульсов снова поступает через 45 элемент на тактовый вход сдвигающег регистра 32. По заднему фронту, трет его импульса единица из младшего ра ряда сдвигающего регистра 32 передв гается в следующий разряд. Этот про цесс продолжается до тех пор. пока единица в сдвигающем регистре 32 не передвинется в i. разряд. Номер i ра ряда определяется временем, необходимым для запоминания блоком 13 выборки и хранения информации, поступающей на его вход. Очередной импул элемента 45 совпадения, при наличии единицы в i разряде сдвигающего регистра 32, через элемент 38 совпадения поступает на. вход установки в нулевое состояние запоминающего регистра 33. По заднему фронту этого импульса запоминаю1пий регистр 33 переходит в нулевое состояние, а еди ница всдвигающем-регистре 32 сдвигается в i +1 разряд. При этом единица в i+1 разряде, пocтvпaя чеоез блок 34 элементов ИЛИ на цифроаналоговый преобразователь 26, включает его старший разряд, одновременно переводит триггер 41 в исходное состояние, обеспечивая тем самым работу элемента. 46 совпадения и через дешифратор 30 и шифратор 25 осуществляет перевод блока 13 выборки и хра нения в режим Хранб;ние, а также выключение ключа 16 и включение ключей 6,7,14 и 15. : Таким образом, с появлением единицы в i+1 разряде сдвигающего регистра 32 начинается первый этап пре образования аналоговой информации, поступающей на вход ключа 6, в цифровую . Результат сравнения входной величины и эталонной, поступающей с выхода циЛроаналогового преобразователя 26 на вх-од ключа 7, сформированный сравнивающим блоком 1, в пооиессе преобразования управляет работой элемента 46 совпадения.При наличии разрешающего сигнала с сравнивающего блока 1 на входе элемента 46 совпаде ния, чет ный импульс с формирователя 44 импульсов поступает через элемент 46 совпадения на тактовый вход запоминающего регистра 33, обеспечивая запись кода с выхода блока 34 элемен-. тов ИЛИ в запоминающий регистр ЗЗ.Та как входы блока 34 элементов ИЛИ связаны с выходами сдвигающего и запоминающего регистров 32 и 33, управляющих работой пиЛроаналогового преобразователя 26, то в процессе преобразования на запоминающем регистре 33 формируется цифровой эквивалент входной величиньд. Одновременно в процессе преобразования происходит компенсация смещений нулевых уровней операционных усилителей 2 и 10, так как в блоке 13 выборки и хранения смещение нулевых уровней операционных усилителей 2 и 10 зафиксированы соответственно с обратным и прямым знаком, а выходы блока 13 выборки-и хранения и операционного усилителя 10 соединены соответственно с неинвертирующим и инвертирующим входами операционного усилителя 2 через ключ 15 и последовательно соединенные ключ 14 и резистор 8. Первый этап преобразования заканчивается при наличии единицы в i+K разряде (где К - число разрядов в цифроаналоговом преобразователе 26) сдвигающего регистра 32 и поступлении на его тактовый вход.импульса с элемента 45 совпадения, который в этом случае поступает также через элемент 39 совпадения на тактовый вход выходного запоминающего регистра 35 и информационный вход сдвигающего регистра 32. По заднему фронту импульса с элемента 45 совпадения, ; цифровой код с запоминающего регистра 33. переписывается в выходной запоминающий регистр 35, единица из 1+К разряда сдвигающего регистра 32 переписывается в нулевой разряд. При этом триггеры 41 и 43 переходят в единичное состояние, а триггер 42 остается в единичном состоянии. Состояния триггеров 41-43 через дешифратор 30 и шифратор 25 обеспечивают перевод блока 13. выборки и хранения из режима Хранение в режим Выборка, выключение ключей 14 и 15 и включение ключа 16. Это позволяет зафиксировать на блоке 13 выборки и хранения наряду со смещением нулевых уровней операционных усилителей 2 и 10 нескомпенсированную разность , напряжений между входной величиной и ее найденным цифровым эквивалентом, зафиксированным на запоминающем регистре 33 и преобразованным в аналоговую величину цифроаналрговым преобразователем 26. В состав нескомпенсированной разности .входит и величина смещения нуевого уровня суммирующего усилигеля 2, таК: как в это время выходные ши-, ны 20 и 21 отключены ключами 14 и 15 т выходов блока 13 выборки и хранеия и операционного усилителя 10 и подключенны к нулевой шине ( шины питания не показаны). Таким образом, блоком 13 выборки и хранения запоминаются как нескомпенсиро1ванная разность, так и смещение на данный момент времени нулевых уровней Операционных усилителей . й10. После окончания проце са запоминания на блоке 13 выборки и хранения, т.е. при наличии единицы в i разряде сдвиганнцего регистра 32 и поступлении импульса с элемента 45 .совпадения, запоминающий регистр 33 переходит в нулевое состояние, единица в сдвигающем регистре 32 переписывается в i+1 разряд, триггер 41 устанавливается в нулевое состоя ние, а состояние триггеров 41-43 через дешифратор 30 и шифратор 25 обеспечивает перевод блока 13 выбор ки и хранения из режима - Выборка в режим Хранение, выключение ключей 6 и 16 и включение ключей 1, 14, 15 и 17, С этого момента начина ется второй этап преобразования, за ключающийся в формировании нониусным блоком, 9 нониусной шкалы для шкалы цйЛроаналогового преобразователя 26, в сложении с эталонами, формирующими деления нониусной шкалы, нескомпенсированной разности напряжений, полученной в процессе первого этапа преобразования, ив сравнении полученной суммы с эталон ми, формирующими деления шкалы цифр аналогового преобразователя 26. Нониусная шкала формируется из шкалы цифроаналогового преобразователя 26 путем умножения значений его эталонов на коэффициент К. Умножение осу ществляется на ВТОРОМ этапе преобра зованид операционным удилителем 10, При этом эталоны, вырабатываемые цифроаналоговымпреобразователем 26, поступают на его вход через клю 17 и резистор 11. Величина резистор 11 выбирается из условия обеспечения умножения операционным усилителем 10 эталонов, поступающих на его вход, на коэффициент К. ТСоэффициёнт К можно выразить через число разрялов используемого цифроаналогового преобразователя. Если через п обозначить число разрядов, не учитывая знакового, ци роаналогового преобразователя, то в личину кванта используемого преобра зователя можно определить как и/2, гд и - максимальное значение преобра зуемого входного напряжения,, а преобразователя с удвоенной разрядност как . Квант нониусной шкапы равен кванту используемого преобразователя, уменьшенному на величину кванта преобразователя с удвоенной 2 разрядностью, т.е. С другой стороны t HTir -Следователь °;К всегда меньше единицы. Например, при использовании трехразрядного цифроаналогового преобразователя К равен 7/в. Сложение эталонов нониусной шкалы с некомпенсированной раз- костью происходит на суммирующем усилителе 2, на котррый они поступают соответственно с выхода операционно-,. го усилителя 10 через ключ 14 и с выхода блока 13 выборки и хранения через ключ 15. При этом полярности нониусной шкалы и нескомпенсированной разности на выходе блока 13 выборки и хранения должны быть противоположны, так как они поступают на различные входы операционного усилителя 2. Это обеспечивается работой знакового разряда цифроаналогового преобразователя. Например, при входном сигнале положительной полярности и нулевом уровне, поступающем с цифроаналогового преобразователя 26, на выходе операционного усилителя 2 получается отрицательный уровень сигнгша, который через компаратор 5, устройства 28 пуска и блок 29 Нормирования кода обеспечивает формирование отрицательных эталонов с выхода цифроаналогового преобразователя 26. Нескомпенсированная разность в конце первого этапа преобразования окажется при этрм отрицательной полярности на выходе операционного усилителя 2 и положительной полярности на выходе 13 блока выборки и хранения. На втором этапе преобразования при нулевом уровне с цифроаналогового преобразователя 26 на выходе операционного усилителя 2 формируется положительный уровень сигнала, так как нескомпёнсированная разность положительной полярности с блока 13 выборки и хранения поступает на неинвертирующий вход операционного усилителя 2. (Следовательно, цифроаналоговый преобразователь. 26 начинает формировать эталоны положительной полярности, которые поступают на инвертирующий вход операционного усилителя 10 и на выходе его получаем нониусную шкалу отрицательной полярности. . Таким образом, в рассмотренном случае на втором этапе преобразования на инвертирующий вход операционного усилителя 2 поступают эталоны положительной полярности -е цифроаналогового преобразователя 26 и эталоны отрицательной полярности с .нониусного блока 9, а на неинвертирующий вход нескомпенсированная разность положительной полярности, т.е. происходит сравнение эталона

цифроаналогового преобразователя 26 с сигналом,являющимся суммой,сфомированной из эталона нониуснрй шкалы и нескомпенсированной разности.

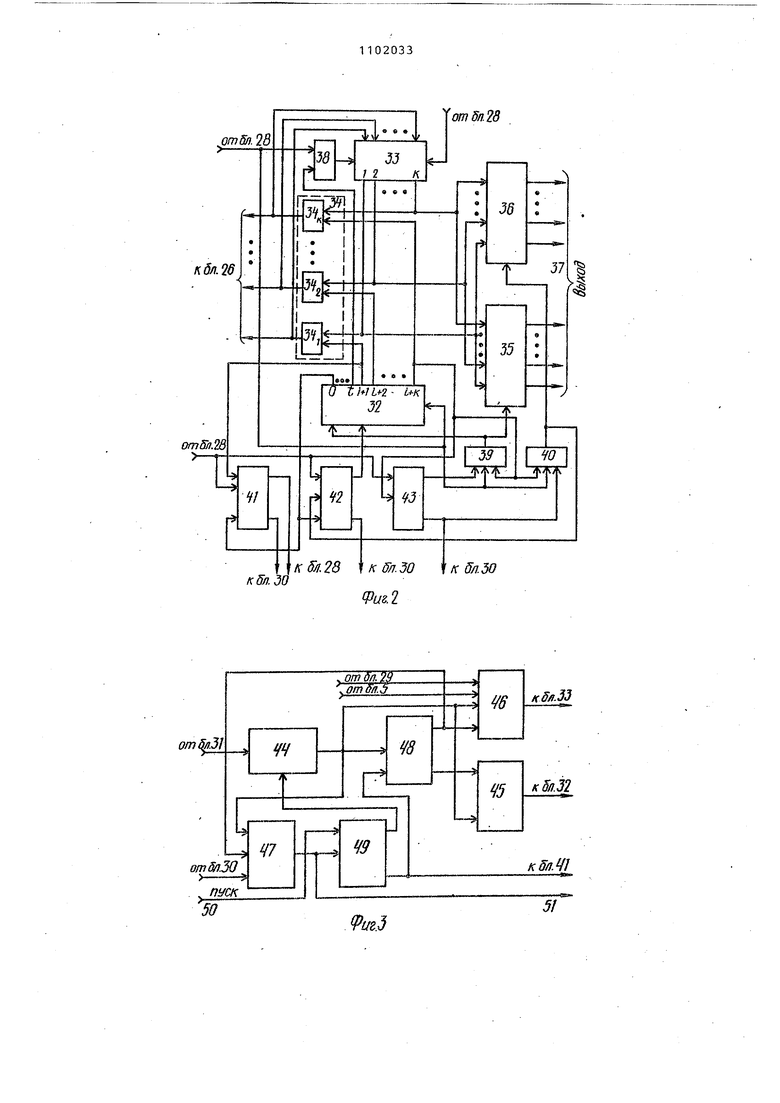

Одновременно, как и на первом этпе преобразования, происходит компе. сация смещения нулевых уровней оперционных усилителей 2 и 10. Полный процесс сравнения на втором этапе преобразования аналогичен процессу сравнения на первом этапе преобразо вания (фиг,4). На фиг.4 б, в и г приведен процесс сравнения для трех знчений нескомпенсированной разности при использовании трехразрядного, не Считая знакового, цифроаналогово го преобразователя.

Рассмотрим процесс сравнения для одного значения нескмопенсированной разности, например,приведенного на фиг.46. После перввго этапа преобра зов.ания (фиг. 4 oil был получен код 101 и нескомпенсированная разность 41, На фи.г. 4 5, в и г в каждой паре изображенных уровней нижний уровень сформирован нониусным блоком 9 по от ношению к верхнему, т-.е, получен из верхнего путем умнолсения его на К T/S, Вертикальной чертой .над нижним уровнем показана нескомпенсированная разность, полученная на перBOM этапе преобразования. На фиг,4 видно, что для этого значения нескомпенсированной разности сформироВсшся код 010.

Таким образом, результирующий код равен 101010. Второй этап преобразования заканчивается при наличии единицы в i +К разряде сдвигающего .регистра 32 и поступлении импульса с элемента,45 совпадения на его тактовый вход.

По заднему фронту импульса элемента 45 совпадения, поступающего также через элемент 4б совпадения на тактовый вход выходного запоминающего регистра 36 и счетный вход тр.иггера 42, цифровой код запоминающего регистра 33 переписывается в выходной запоминающий регистр 36, а сдвигающий регистр 32 и триггеры 42 и 43 переходят в нулевое состояние. Нулевое состояние трип-еров 41-43 через дешифратор 30 и шифратор 25 обеспечивает выключение ключей 6,7, 14 - 17, а через дешифратор 30 подготавлив ет к работе элемент 47 совпадення. Очередной импульс с формирователя 44 импульсов поступает через элемент 47 совпадения на счетный вход триггера 49 и на выходную шину Конец преобразования 51.

/

,По заднему фронту этого импульса триггер 49 переходит в нулевое состояние и блокирует работу формирователя 44 импульсов. На этом преобразование входной величины в цифровую форму заканчивается. Конечный, результат хранится в выходных запоминающих регистрах 35 и 36. выходы которых подключены к выходным шинам 37.

Таким образом, в отличие от известных аналого-цифровых преобразователей поразрядного кодирования, предлагаемое устройство позволяет при заданной разрядности цифроаналогового преобразователя уменьшить погрешность квантования по уровню до погрешностей, получаемой при- исползовании цифроаналогового преобразователя с удвоенной разрядностью, т.е. уменьшение погрешности квантования по.уровню происходит в 2 раз где п - число разрядов, не считая знакового, используемого цифроаналогового преобразования. Одновременно повыи1ается точность преобразования за счет двухкратной, за время преобразования, коррекции дрейфа нуля суммирующего усилителя,, которая обеспечивается в процессе преобразования нониусным блоком.

Кроме того, .предлагаемое устройство позволяет сократить при использовании его в системах сбора данных врем5, необходимое на переключение его входа с одного канала на другой, так как это переключение можно произвести в период второго этапа преобразования, когда вход устройства Отключен от входа суммирующего усилителя, что позволяет повысить скорость обработки данных.

Предлагаемое устройство может найти широкое применение в различных информационно-измерительных системах с преобразованием аналоговой информадии в дискретную.

«JU

.х

к5п.ЭО

omSn.28

К бл.50

Vus.2

5/

teJ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Зарубежная электроника, 1975, № 1, с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шляндин В.М | |||

| Цифровые измерительные преобразователи и приборы. | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Станок для изготовления из дерева круглых палочек | 1915 |

|

SU207A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-07-07—Публикация

1982-01-27—Подача