4

о сх со

О1

2. Адаптер noii. Х.отпичаюга 0 и с я тем, что уэеп управпения блока связи с каналом содержит входной мупьтиппексх)р, постоянную память и выходной регистр, причем группа ннфор. мационных входов входного мупьтшшексора соединена с первым - восьмым вхо дами уз па, группа адресных входов - с первой группой выходов выходного р© гистра, а выход - с управгшювдим вхо дом постоянной памяти, грута выходов i которой подкшочена к группе входов

ходного регистра, а группа адресных вхЫ . дов -к второй группе выходов выходного ре: гистра,третья группа выходов которого соед нена с первымняевятым выходами узла,

3, Адаптер по п. 1, о т п и ч а к i щ н и с я тем, что уаеп буферно памя™

ти бпока связи с канале содержит память, счетчик адреса, регистр копичества байтов и схему сравнения, причем информационные вход и выход памяти соедине..ны соответственно с информационными ; входом и выходом уэпа, адресный вход с выходом счетчика адреса и первыми входами схемы сравнения и регистра ко-, тачества байт, второй вход которого подключен к первсялу входу счетчика -адреса, первсыу утфавпяняцему входу шмяти и входу управпения записью уэпа, а выход к второму входу схемы сравнения, выход которой является выходом синхронивзаиии уэпа, второй вход счетчика адреса соединен с вторым управляющим входом памяти и выходом управления чтени-j ем узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1985 |

|

SU1305697A2 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Имитатор канала | 1984 |

|

SU1239719A2 |

| Адаптер канал-канал | 1981 |

|

SU1037235A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Имитатор канала | 1985 |

|

SU1377857A2 |

| Имитатор канала | 1985 |

|

SU1280633A2 |

| Имитатор канала | 1985 |

|

SU1287160A1 |

1. АДАПТЕР КАНАЛ АНАИ по ввт.св. № 734661, отличающ в и с а тбм, что, с цепью повыш&вия провэводкгепьноств адаптера, в каж«дый его блок связв с каналом введен узел буферной памятв, првяем в каждом блоке связи с каналом восьмой выход узла управления соединен с входом управления записью узпа буферной памятв, информационный вход которого подключав к выходу узла входных сигналов, внфо мационные выходы узлов буферной первого и второго блоков связи с каналом соединены соответственно с пяплми входами узлов выходных сигналов второго и первого блоков связв с кавалом, а входы управления чтеввем в выходы синхроншацнв - соответственно с девятыми выходами в седьмыми вхоцамв узлов управления второго в первого блоков связв с каналом.

Изобретение относится к вычислитеге яной технике и может быть испопьзовано в многомашинных вычислительных ксмплексах для связи цифровых вычислительных машин (ЦВМ).

По основному авт.св. № 734661 известен адаптер канал-канал, содержа ший буферный регистр, блок сравнения . команд, блок задании режима и два бпсжа связи с каналом, каждый из которых содержит узел входных сищалов, регистр адреса, регистр команд, узел сравнения адресов, дешифратор ксаданд, узел управления, регистр байта состояния, уэеп выходных сигнаш в, выход которого являегся первым выходам адаптера, вход узла выходных сигналов каждого блока связи с каналом объединен соотве стввнно с первыми входами буферного регистра выход котррого подключен к второму входу узла выходных сишалов в каждом из блоков связи с каналом,в ход узла входных сигналов является первым входом адаптера, а выход подключен к первым входам узла сравнения адресов, узла выходных сигналов и регистра команд, выход которого соединен через дешифратор команд с первым входом уз па управления, шрвый выход которого подкшочен к третвему входу узла выходных сигшлов, четвертым входом соединенного с выходом регистра байта состояния, вход которого подключен к второму выходу узла управления, второй вход и третий которого подключены соответственно к выходу и второму вюду узла сравнения адресов, четвертые выходы узла

управпения в каждсы иг- блоков связи с канале соеди ны между собой, пятые выходы - с вторыми входами буферного регистра, шестой выход узла управления является вторым выходом адаптера, седьмой &ь1ход соеаинен с вторым вхоаом регистра команд, третий вход - с вторалм входом ада11тера, вход узла сравнения адресов подключен к выходу регистра адреса, выходы блсяса задания режима

подключены соответственно к пятым входам узлов управления блоков связи с канаткял, шестые входы которых соединены с выходом б лежа сравнения ксаланд, входы которого соединены соответственно с

выходами регистров команд блоков связи с каналом Cl J

Недостатком известного адаптера канап-канал является низкая скорость межмашинного , обусловпенная

там, что общая скорость обмена определяется быстродействием менее быстродействующего каёсагаа ЦВМ, подключенного к адаптеру, а также невоэможвост к организации обмена в авух направлениях

одновременно.

Целью изобретения является повыш ние производительности.

Поставпенная цепь достигается тем, что в адаптер канап-канап в каждый бпок связи с каналом введен уэеп буферной памяти, причем в каждом бпоке связи с канагк%1 восьмой выход узпа управления соединен с входом управления записью узпа буферной памяти, информационный вход которого подключен к выходу узла входнь1х с{1гнапов, информационные выхо ды узпов буферной памяти первого и. второго бпоков.связи с каналом соедини вы соответственно с пятыми входами уэпов выходных сигналов BTopotx) и перво1ч блоков связи с каналом, а входы управления чтением и выходы синхронизации - соответственно с девятыми выходами и седьмыми входами узлов управпения второтх} и первого блоков связи с каналом.

При этом узеп управления блока связи с каналом содержит входной мультиплексор, постоянную память и выходной регистр, причем группа информационшых входов входного мультиплексора соединена с первым - восьмым входами узпа, группа адресных входов - с первой груп пой выходов выходного регистра а выход с управляющим входом постоянной памяти, группа выходов которой подключена к группе входов выходного регистра, а группа адресных входов - к второй группе выходов выходного регистра, третья группа выходов которого соединена с первым - девятым выходами узла.

Кроме того, узел буферной памяти блока связи с каналом содержит память, счегчвк адреса, регистр количества байтов в схему сравнения, причём информашюншле вход и выход памяти соединеои соответственно с информационными входом и выход я 1 узла, адресный вход с выходом счетчика адреса и первыми входами схемы сравнения и регистра количества байт, второй вход которого подключен к первсв у входу счетчика адреса, первсыу управляющему вход5М1а мяти в входу управления записью узла, а выход - к второму входу схемы сравнения, выход которой является выходом стшхроиизации узла, второй вход счетч ка адреса соединен с вторым управпякь щйм входом памяти и выходом управгаэния чтением узпа.

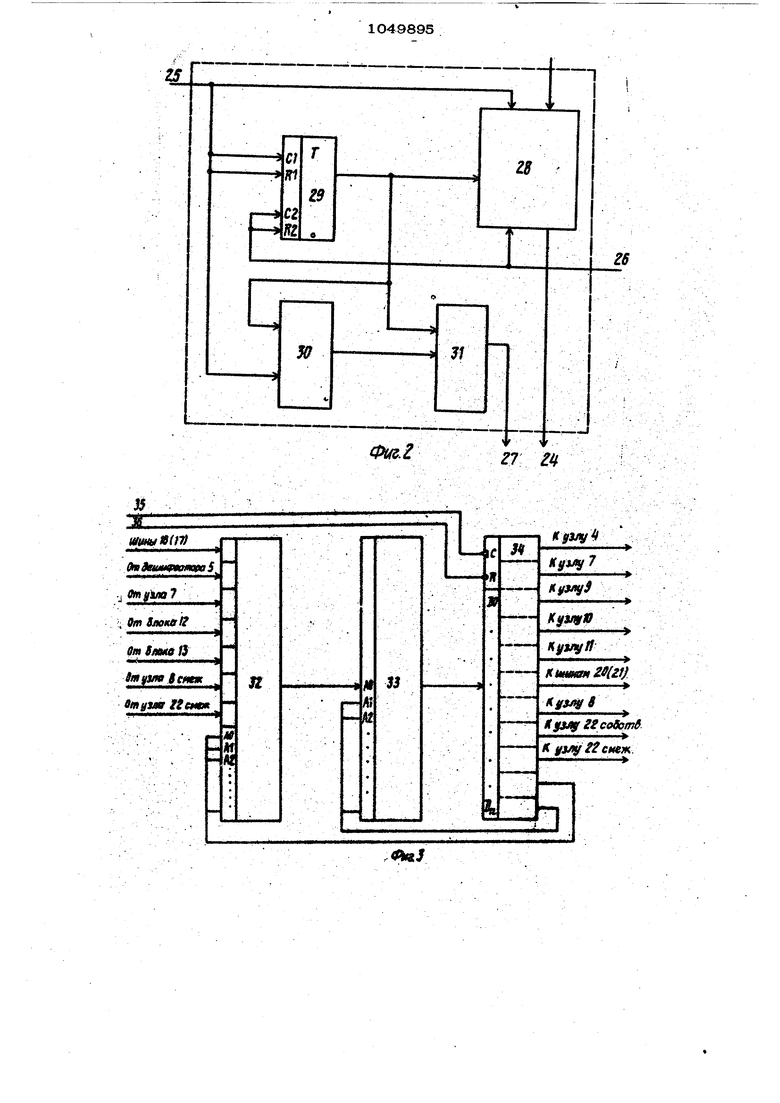

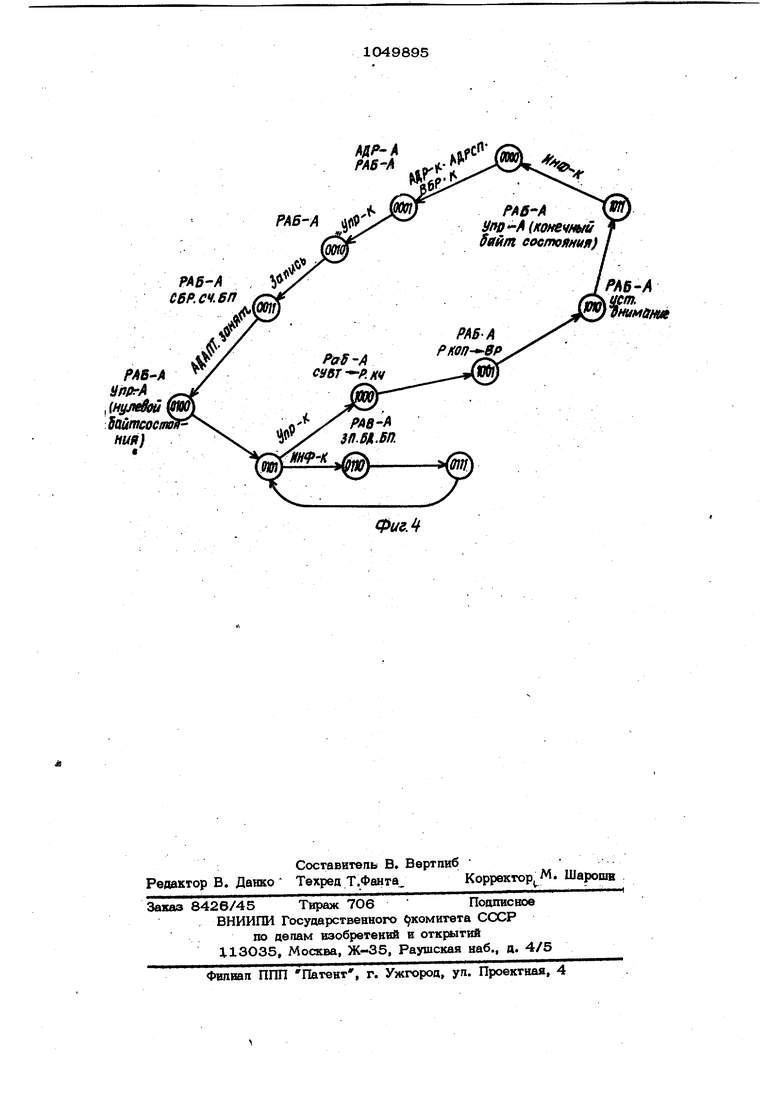

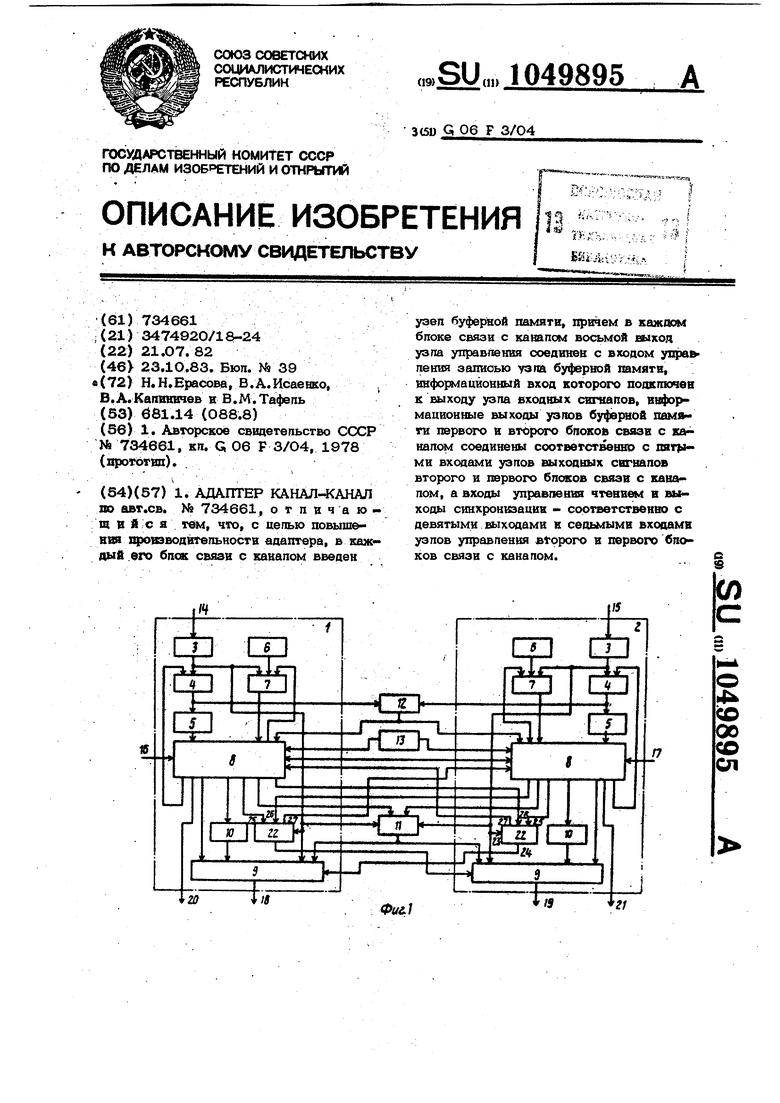

На фиг. 1 представлена блок-схема адаптера; на фиг. 2 - функшюнальшя I схема узла буферной памяти; на фиг. 3 фуюшиональная схема узла управления; на фиг. 4 - граф состояний и переходов узлов управления.

Адаптер содержит (фиг. 1) первый и второй блоки 1 и 2 связи с каналом, каждый из которых включает узел 3 выходных сигналов, регистр 4 команд,

дешифратор 5 команд, регистр 6 адреса, узел 7 сравнения адресов, узеп 8 угарен пения, узел 9 выходных сигналов, регистр Ю байта состояния. Блоки 1 и 2 связи с каналом соединены между собой

несколькими управляющими линиями и через общие буфер олй регистр 11, бпок 12 сравнения команд и бпсж 13 задания режима. Адаптер связав с сопрягаемыми каналами с помощью шин 14 и 15 ш формационных пиний кенапов, шин 16 и 17 управляющих пиний каналов, шин 18 и 19 информационных пиний абонентов, шин 2О и 21 управпяюших -линий абовев тов. Каждый КЗ блоков связи с к&яапом

содержит узел 22 буферной памяти с информационными входами 23 и выходами 24, -первыли 25 и вторыми 26 у равляющимн входами, управляющими вы- ходами 27.

Узлы 22 буферной памяти содержат (фиг. 2) память 28, счетчик .29 адреса, регистр ЗО количества байтов и схеьау 31 сравнеш1я.

Узел 8 управления включает в себя

входной мультиплексор 32, постоянную память 33, выходной регистр 34. На фиг. 3 показаны также шина 35 сигнапов синхронизации и швиа 36 начальной установки. Мупьтиплексор 32 предназначен для реааиэации условных переходов. Постоянная памятв 33 служит для хранения набора микрокоманд. Выходной регистр 34 предназначен дпя устравевия разброса времени выборки различных адресных разрядов постоянной памятв.

Информационные входы мультиплексора соединены с входными шинами узла, по которым поступают сигналы перехода из одного состояния узла 8 в другое. Выход мультиплексора подключен к мпадшему адресному входу постоянной памяти 33, на группу адресных входов которой подаются сигнапы с выходного регистра. ,. Узел 8 управления реализован в виде

микропрограммного автомата, граф-апгоритм ксторого представлен на фиг. 4 (для упрощения приведена часть алгоритма описывающая выполнение.операции Запись в режиме Одна память; Остальные чао; ти алгоритма выполняются аналогшивлм образом. Каждая часть алгоритма может быть выполнена как отдельная микропрограмма). В этом графе в кружках изображен адрес ячейки постоянной памяти, в которой хранится микрокоманда; дугами изображены переходы из одного состояния в другое; названия сигналов над кружками означают, что сигналы формируются в этих состояниях; названия сигналов над дугами означают, что переход из одного состояния (начапо дуги) в другое (стрв ка дуги) происходит при наличии этого сигнапа.

Узпы 3 входных сигналов представпнют собой группу усилителей - приемни™ ков сигналов интерфейса и осуществляют прием информационных сигналов интерфейса от канала по шинам 14(15).

Регистр 4 и дешифратор 5 команд осуществляют прием, хранение и дешифрацию кода, поступающего из канала.

Регистры 6 и узлы 7 сравнения адре са осуществляют сравнение адреса с за данным адресом, поступившим в канал, и выдачу в канал заданного адреса.

Узлы 8 управления вьрабатывают внутренние сигналы упр авпения и сигналы управления на шинах 20(21) пиний уп равления абонента в соответствии с кодом команды, сигналами, поступающими из канала по шинам 16(17), и сигналами блока 13 задания режимов.

Узлы 9 выходных сигналов предстаапяют собой усилители - передатчики ин-г терфейса и осуществляют передачу в канал инфо1 4ац1юнных сигналов по шинам 18(19).

Регистры 10 байтов состояния осуществляют хранение и передачу в кавал байтов состоянт.Формирование разрядов в регистрах 1О осуществляется по сигналам узлов 8.

Буферный регистр 11 осуществляет прием, .хранение и передачу в канал тов команд и данных. Передача данных через регистр 4 осуществляется только в режимах, при которых не используют ся узлы 22 буферной памяти. Блок 12 осуществляет сравнение кодов команд, поступивших вз первого и второго каналов. Блок 13 представляет собой , лерный регистр, задающий четыре режима работы: Монопольный, Мультиплексный, Одна память и Две памяти. Узпы 22 буферной памяти служат для приема, хранения и выдачи в канал байто .

Адаптер канагь-канал работает в четырех режимах, задаваемых блоком 13. В режимах Монопольный и Мульти-. плексный адаптер работает так же, как и известный адаптер.

В режиме Одна память адаптер работает следующим образом.

Канал (например, первый) выбирает адаптер в соответствии с принципами организации ввода-вывода. При этом адрес от канала по шинам 14 канала через узел 3 поступает в узел 7 для сравнения с адресом адаптера, хранимым в регистре 6 адреса. Результат сравнения адресов выдается в узеп 8. Если адреса совпадают, из узла 7 сравнения адресов выдается ответный адрес адаптера на шины 18 абонента и далее в канал

Дешифратор 5 декодирует команду, полученную из канала и хранимую в регистре 4.

После расшифровки команды первого канала адаптер осуществляет прием по шинам 14 и запись через узел 3 в узец, 22 блока 1 информации. При этом узел 8 блока 1 формирует сигнал обнуления, а затем сигналы модификации счетчика 29 и сигналы обращения в память 28, которые поступают на входы 23 узла 22 блока 1.

После окончания приема от первого канала данных (окончание определяется каналом) узел 8 блока 1 формирует сигнал записи в регистр ЗО, который поступает на входы 25 узла 22 блока 1 заносит в регистр 11 команду первого канала, а узел 8 блока 2 формирует и передает во второй канал байт состояния с указателем Внимание. В ответ второй канал вводит команду уточнения ;остояния, по которой ему передается содержимое регистра 11, т.е команда первого канала. По содержимсн у регистра 11 программа второй ЦВМ определяет, какую команду необходимо ввести в адаптер, и через второй канал вводит ее в адаптер. При сравнении команд блоком 12 (сравнению подвергаются поля модификаторов) адаптер начинает гюре давать во второй канал данные из узла 22 блока 1 через узел 9 блока 2. При узел 8 блока 2 формирует сипнап обнуления, а затем сигналы модифвкаанн счетчика 29 и сигналы обращения в память 28, которые поступают на , 26 узла 22 бпсжа 1. При сравнение значения счетчика 29 в регистра 30, что свидетельствует о завершении передачи во второй кааап данных, принятых от первого канала, на выхоае схемы 31 сравнения формируется сигнал, поступающий с выхода 27 узла 22 блока 1 в узел 8 блока 2, по которо My оканчивается выпопнение команоы во втором канапе, При передаче данных из второго канапа в первый адаптер работает также за искшочением того, что данные записываются в уэеп 22 бгюка 2, записью в узел 22 управляет узеп 8 блока 2, а считыванием - узел 8 блока 1. В режиме Две памяти адаптер обеспечивает одновременный прием данных из первого и второго каналов в узлы 22 соответственно блоков 1 и 2 к (или пе редачу в первый и второй канал данных из узлов 22 соответственно блоков 2 Н 1). В этом режиме, если оба канала одновременно передают данные в-адаптер,, данные первого канала записываются в узел 22 блока 1, а данные второго канала - в узел 22 блока 2. Затем во второй канал через регистр 11 и узел блока 2 передается байт состояния с указателем Внимание, после этого в первый канал через регистр 11 и узел блока 1 передается такой же байт. Программы первой и второй ЦВМ вводят в адаптер команды уточнения состояния, определяют необходимые ответные команды и вводят их через первый и второй канал в адаптер. По этим командам данные из узла 22 блока 1 передаются во второй канал, а данные вз узла 22 блока 2 - в первый канал. В этом режиме блок 12 не работает, и сравнение команд не производится. Узлами 8 по сигналам дет1Вфратора 5 производится только авалю направлени передачи данных (команда записи или чтения). Собственно процедуры записи и считывания в узлы 22 осуществляются так же, как и в режиме Одна память. Узел управления работает следующим образом. В исходном состоянии регистры 34 обнупевая, и на адресных входах постояи ной памяти 33 присутствует нулевой ьдрее. После сброса сигнала начальной установки по кахсдому сигналу синхронизации-щюизводится анапиз сигналов усло вий, поступающих на входы мультиплексора 32 и переход в очередное состояни -В каждом состояний узла 8 на адресный вход постоянной памяти 33 подклк чается одна из входных шин узла. Выбор одключаемой шины производится в поле ормата микрокоманды. Возможный фо1жгат микрокоманды име т ввд где АМК - поле адреса следующей мвкрокоманды;АМХ - поле кода адреса подключаемого входа мультиплексора; УПР - поле выходных сигналов уст ройства уп; 1вления; Если на входной шине присутствует входной сигнал (т.е. логическая 1), то узел 8 переходит в состояние, в младшем (юзряде которого присутствует единшт. Если на выбранной шине отсутствует входной сигнал (т.е. щ)нсутствует логический О), то автомат переходит в в состояние, в младшем разряде которого присутствует ноль. Например, пусть поле адресов постоянной памяти 33 представляет комбинацию ООН, попе адреса входного мультиплексора 32 . Если на пятом входе мультиплексора 32 присутствует входной сигнал (т.е. логи ческая ), то переход осуществляется по адресу ОО111, если входкюй сигнал отсутствует (т.е. осуществляется по адресу 0011О). Аналогичио реализуются все остальные условные переходы. Для формирования выхоа 1х сигналов устройства управпвияя используется эонтальное микропрограммирование, т.. каждому разряду поля выходных сигналов микрокоманды ставится в соответствие определенный выходной сигнал уст ройства управления. Таким образом, предложенный адаптер канагь-канал. обеспечивает более высокую производительность межмашинного по сравнению с известным, так как позволяет выполнять обмен между ада1 тером и каналом со скоростью, определя емой стродействием данного канала, а не скоростью меиее &1стродействукяцего канала, подключенвого к адаптеру; выполнять между адаптером и ggg ожидания подключения (т.е. приема байта состояния с указателем Внимание) второго канала. /Me-, ИпргА .{HyjieSmi Saumcoci ния) М ФигЛД

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Адаптер канал-канал | 1978 |

|

SU734661A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-10-23—Публикация

1982-07-21—Подача