и два элемента задержки, причем первый и второй входы первого элемента И соединены соответственно с выходами первых элементов НЕ и триггера, выход - с первым входом второго триггера, выходом соединенного с первыми входами первого триггера и второго и третьего элементов И, выход которо го подключен к первому входу третьего триггера, второй вход и выход второго элемента И соединены соответственно с выходом второго элементе НЕ и первым входом четвертого триггера, выход которого соединен с входом первого элемента-задержки и с первым входом четвертого Элемента И, а вход с вторым выходом имитатора и выходом пятого триггера,, первым входом подключенного к выходу четвертого элемента И, выход пятого элемента И соединен с первым входом шестого триггера, второй вход которого подключен . к выходу первого элемента задержки, а выход - к вторым входам третьего и пятого триггеров и через второй элемент задержки - к первым входам шестого и седьмого элементов И, выход шестого элемента И соединен с вторым входом второго триггера, третьим ;;;ходом подключенного к выходу четвертого триггера, а четвертым входом - к выходу третьего триггера и первому входу пятого элемента И, второй вход которого соединен с выходом третьего элемента НЕ, третий и чет- вертый входы шестого триггера соеди нены соответственно с выходами второго триггера и седьмого элемента И, входы первого, второго и третьего элементов НЕ соединены соответственно с вторыми входами первого триггера, четвертого и третьего элементов И и соответствующими шинами входа имитатора, третьи входы второго и .третьего элементов И и вторые входы шестого и седьмого элементов И подключены к соответствующим шинам входа имитатора, выходы первого, третьего и четвертого триггеров соединены с соответствующими шинами первого выхода имитатора.

3. Устройство по п, 1, о т л и чающееся тем, что узел управления содержит входной дешифратор, выходной дешифратор, генератор синхросигналов, дешифратор состояний и группу триггеров, причем первый - четвертый входы входного дешифратора соединены соответственно с первым четвертым входами узла, а пятый входс выходом дешифратора состояний и первым входом выходного дешифратора, группа выходов которого соединена с первым-шестым выходами узла, а второй, третий, четвертый и пятый входысоответственно с первым, третьим и четвертым входами узла, первые и вторые входы триггеров группы подключены соответственно к первой и второй группам выходом входного дешифратора, третьи входы - к выходу генератора синхросигналов, а выходы - к группе входов дешифратора состояний.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1982 |

|

SU1067492A1 |

| Адаптер канал-канал | 1983 |

|

SU1112361A2 |

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Адаптер канал-канал | 1983 |

|

SU1144114A1 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

| Адаптер канал-канал | 1985 |

|

SU1259276A1 |

| Адаптер канал-канал | 1987 |

|

SU1425694A1 |

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах для сопряжения ЦВМ.

Известны адаптеры канал-канал, содержащие буферный регистр, два полуадаптера, блок сравнения команд.и блок задания режима L1 .

Недостаток известных адаптеров состоит в низкой надежности и ограниченных функциональных возможностях, что приводит к низкой производительности вычислительных комплексов, где они используются.

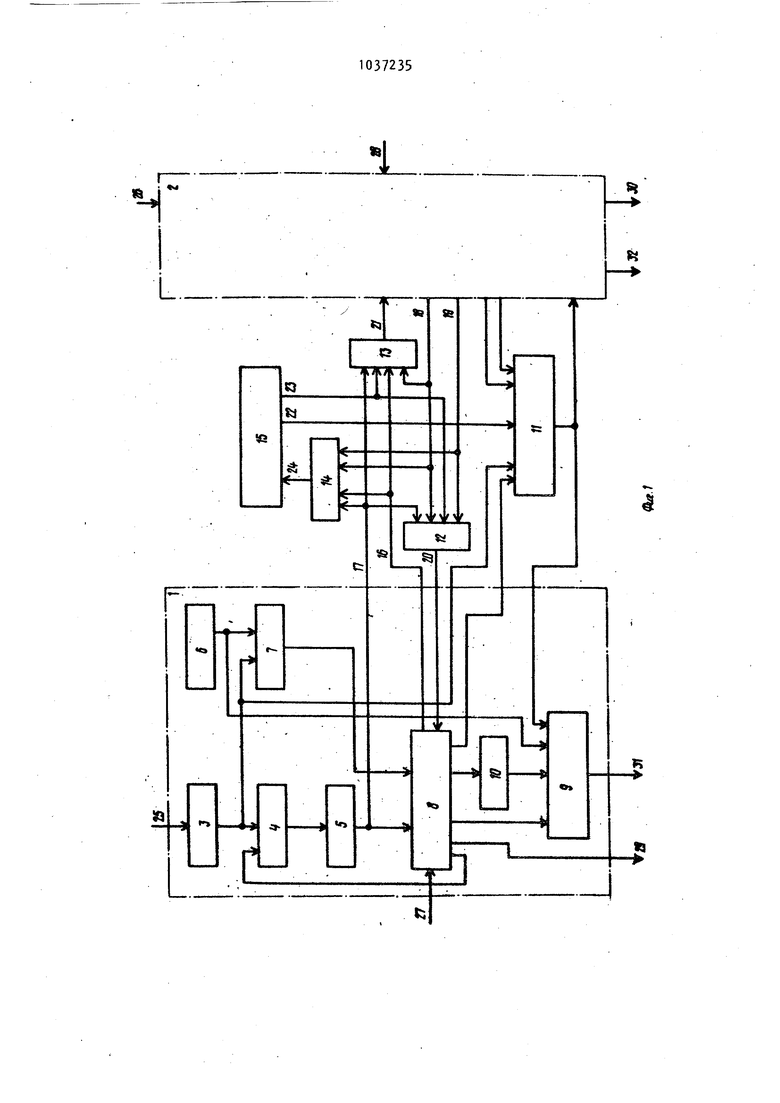

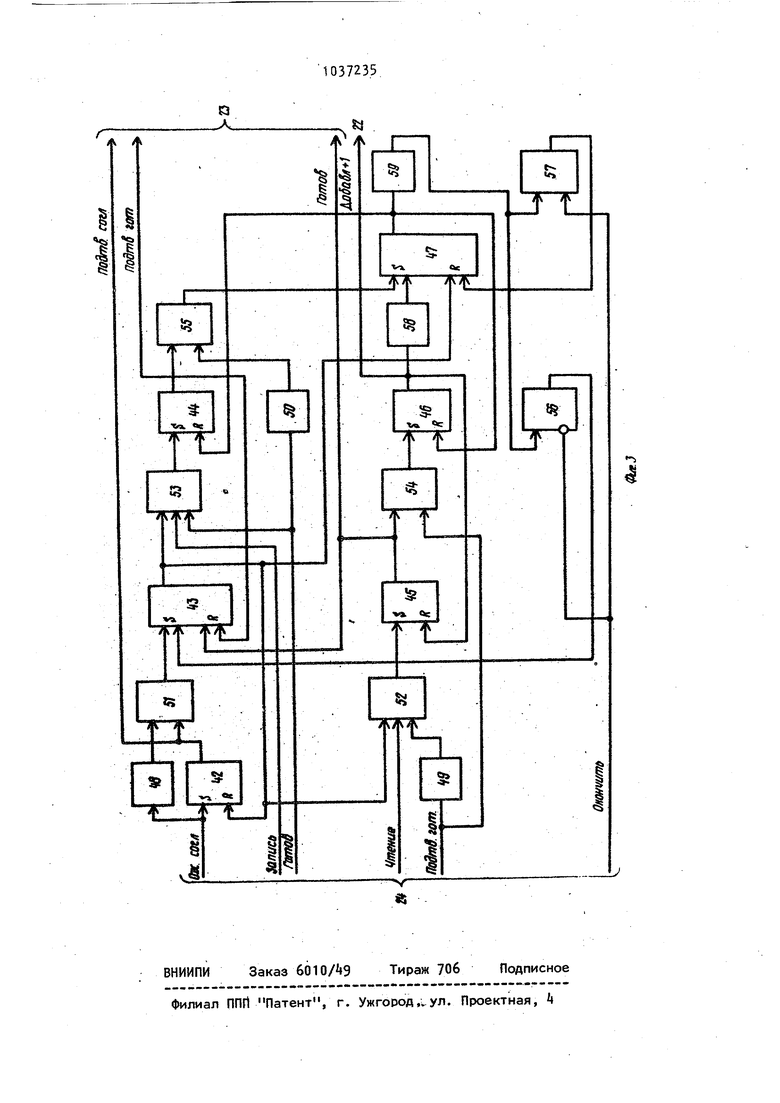

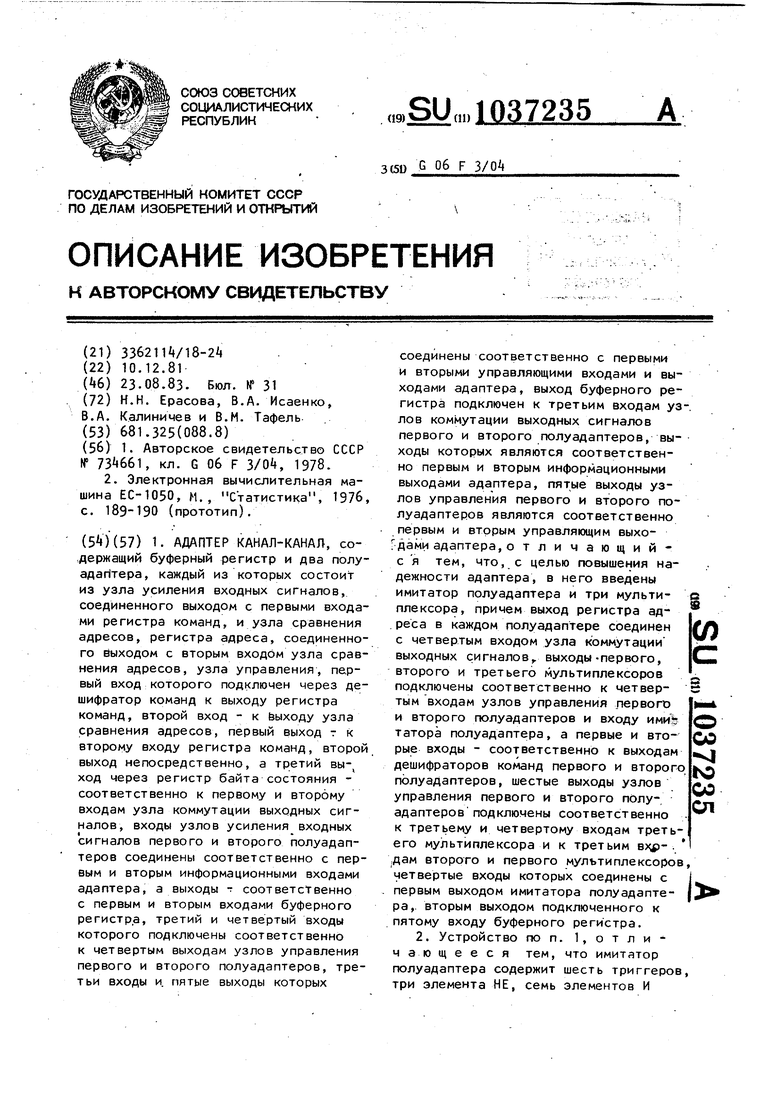

Наиболее близким по технической сущности к предлагаемому является адаптер канал-канал, содержащий буферный регистр и два полуадаптера, каждый из которых состоит из узлов входных и выходных сигналов, регистра команд, соединенного выходом через Дешифратор команд с первым входом узла управления, а входом - через узел входных сигналов с соответствукщим информационным входом адаптера, регистр адреса, выходом соединенного через узел сравнения адресов со вторым входом узла управления, третий вход и первый выход которого являются соответствующими управляющими входом и выходом адаптера, а второй и третий выходы - соединены соответственно с первым и вторым входами узла выходных сигналов, третий вход которого подключен ко второму входу узла сравнения адресов и выходу узла входных сигналов, выход - с соответствующим информационным выходом адаптера, а четвертый вход - через регистр состояния с четвертым выходо узла управления, пятым выходом соеди ненного со вторым входом регистра команд, а шестые - с третьим входом узла .сравнения адресов, причем выход буферного регистра подключен к пятым входам узлов выходных сигналов полуадаптеров, первый и второй входы соответственно к выходам узлов входных сигналов полуадаптеров, третий и 1етвертый входы - к седььв 1м выхода узлое управления полуадаптеров, третий вход и восьмой выход узла управления первого полуадаптера соединены соответственно с восьмым выходом и третьим входом узла управления второ го полу адаптера 2 J. Недостаток известного адаптера со стоит в низкой надежности, определяемой большим временем восстановления адаптера. Это обусловлено тем, чт« тестовые и диагностические программэ проверки известного адаптера приходится размещать в двух. ЦВМ, которые он сопрягает. Эти программы сложны и сильно связаны. Существует возможность при тестировании подключать адаптер к двум каналам одной ЦВМ и (ПРОИЗВОДИТЬ диагностику с помощью пр граммы этой ЦВМ. В этом случае, од-, нако, проверка адаптера связана с ме ханической перекоммутацией разъемов и, как следствие, увеличением времен ремонта. Кроме того, при тестировани известного устройства невозможно точ . но определить место неисправности, так как команду обмена тестовой программы совместно выполняют не только два полуадаптера, но и два канала ввода-вывода, В результате необходимость длительных переключений при по иске неисправностей и низкая разрешающая способность диагностических I программ приводят к существенному снижению коэффициента готовности основного надежностного параметра многомашинных комплексов. 1 5. Целью изобретения является повышение надежности адаптера. Поставленная цель достигается тем, что в адаптер, содержащий буферный , регистр и два полуадаптера, каждый из которых состоит .из узла усиления входных сигналов, соединенного выходом с первыми входами -регистра команд и узла сравнения адресов, регистра адреса, соединенного выходом с вторым . входом узла сравнения адресов, узла управления , первый вход которого подключен через дешифратор команд к выходу регистра команд, второй вход к выходу узла сравнения адресов, первый выход - к второму входу регистра команд, второй выход непосредственно, а третий выход через регистр байта состояния - соответственно к первому и второму входам узла коммутации выходных сигналов, входы узлов усиления входных сигналов первого и второго полуадаптеров соединены соответственно с первым и вторым информационными ёходами адаптера, а выходы соответственно с первым и вторым входами буферного регистра, третий и четвертый входы которого подключены соответственно к четвертым выходам узлов управления первого и второго полуадаптеров, третьи входы и пятые выходы которых соединены соответственно с первы и вторыми управляющими входами и выходами.адаптера, выход буферного регистра подключен к третьим входам узлов кo lмyтaции выходных сигналов первого и второго полуадаптеров, выходы которых являются соответственно первым и вторым информационными выходами адаптера, пятые вь1ходы узлов управления первого и второго полуадаптеров являются соответственно первым и вторым управлякщими выходами адаптера, введены i имитатор полуадаптера и три мультиплексора, причем выход регистра адреса в каждом полуадаптере соединен с четвертым входом узла коммутации выходных сигналов, выходы первого, второго и третьего мультиплексоров подключены соответственно к четвертым входам узлов управления -первого и второго полуадаптеров и входу имитатора полуадаптера, а первые и вторые входы - соответственно к выходам дешифраторов команд первого и второго подуадаптеров, шестые выходы узлов управления первого и второго полуадаптеров подключены соответственно к третьему и четвертому входам треть его мультиплексора и к третьим входам второго и первого мультиплексоров, четвертые входы которых соедине ны с первым выходом имитатора полуадаптера, вторым выходом подключенного к пятому входу буферного регистра, а также тем, что имитатор полуадаптера содержит шесть триггеров. Три элемента НЕ, семь элементов -И и два элемента задержки, причем первый и второй входы первого элемента И соединены соответственно с выходами первых элементов НЕ и триггера, выход - с первым входом второго триггера, выходом соединенного с первыми входами первого триггера ,и второго и третьего элементов И, выход которого подключен к первому входу третiiero триггере, второй вход и выход второго элемента И соединены соответственно с выходом второго эле мента НЕ и первым входом четвертого триггера, выход которого соединен со входом первого элемента задержки и с первым входом четвертого элемента И, а вход - с вторым выходом имитатора и выходом пятого триггера, первым входом подключенного к выходу е вертого элемента И, выход пятого эле мента И соединен с первым входом шестого триггера, второй вход которо го подключен к выходу первого элемента задержки , а выход - к вторым входам третьего и пятого триггеров и через второй элемент задержки к первым входам шестого и седьмого элементов И, выход шестого элемента соединен с вторым входом второго триггера, третьим входом подключенного к выходу четвертого триггера, а четвертым входом - к выходу третьего триггера и первому входу пятого элемента И, второй вход которого сое динен с выходом третьего элемента Н третий и четвертый входы шестого триггера соединены соответственно с выходами второго триггера и седь го элемента И, входы первого, второ го и третьего элементов НЕ соединены соответственно .с вторыми входами первого триггера, четвертого и трет его элементов И и соответствующими шинами входа имитатора, третьи входы второго и третьего элементов И и вторые входы шестого и седьмого эл ментов И подключены к соответствуюа шинам входа имитатора, выходы перво ГО, третьего и четвертого триггеров соединены с соответствующими шинами первого выхода имитатора, и тем, -что узел управления содержит входной дешифратор, выходной дешифратор, генератор синхросигналов, дешифратор состояний и группу триггеров, причем первый - четвертый входы входного дешифратора соединены соответственно с первым-четвертым входами узла, а пятый вход - с выходом дешифратора состояний и первым входом выходного дешифратора, группа выходов которого соединена с первым-шестым выходами узла, а второй, третий, четвертый и пятый входы - соответственно с первым, третьим и четвертым входами узла, первые и вторые входы триггеров группы подключены соответственно к первой и второй группам выходов входного дешифратора, третьи входы - к выходу генератора синхросигналов, а выходы к группе входов дешифратора состояний. На фиг. 1 представлена блок-схема адаптера; на фиг. 2 и 3 примеры функциональных схем узла управления и имитатора полуадаптера. Адаптер содержит (фиг. 1) полуадаптера 1 и 2, каждый из которых состоит из узла 3 усиления входных сигналов, регистра 4 команд, дешифратора 5 команд,регистра 6 адреса, узла 7 сравнения адресов, узла-8 управления , узла 9 коммутации выходных сигналов и регистра 10 байта состояния, буферный регистра 11, мультиплексоры 12-й и имитатор 15 полуадаптера. На фиг. 1 показаны шины 16-21 связи полуадаптеров 1 и 2 с мультиплексорами 12-И, шины выходов и входа имитатора 15 полуадаптера, а также шины 25 и 2б информационных входов адаптера, шины 27 и 28 управляющих входов адаптера, шины 29 и 30 управляющих выходов адаптера и шины 31 и 32 информационных выходов адаптера. Узел 8 управления содержит (фиг.2) входной дешифратор 33, генератор 3 синхросигналов, триггеров группы, дешифратора 0 состояний и выходного дешифратора k. Имитатор 15 полуадаптера содержит (фиг. З) триггеры 42-27, элементы НЕ 48-50, элементы И и элементы 5В и 59 задержки. Адаптер канал-канал работает следующим образом. Канал (например, первый канал, подключенный к полуадаптеру1) производит начальную выборку адаптера/ При этом адрес от первого канала по шине 25 через узел 3 поступает в узел 7, где сравнивается с адресом полуадаптера присвоенным ему в системе и хранящемся в регистре 6 адреса. Регистр 6 может быть выполнен в виде тумблерного регистра. Результат сравнения адресов (сигнал Адрес совпадения) выдается в узел 8, Который в зависимости от сигналов управления первого канала на шине 27 и сигналов, поступающих с выходов дешифратора 5i узла 7 и мультиплексора 12 вырабатывает сигналы, обеспечивающие работу адаптера в соответствии с.ОСТ k ГО 30i.000 Интерфейс ввода-вывода ЕС ЭВМ . Если адреса совпадают, то из регистра 6 выдается ответный адрес адаптера через узел 9 на информационные шины 31 и далее в первый канал, который срав нивает адрес, полученный от адаптера с адресом, ранее выданным на шины 25 и при их совпадении выдает на шины 25 код команды обмены, который запоминается в регистре k и декодируется дешифратором 5. В коде команды указы„- -..х. гч.|.., «: . ,.,i вается режим работы адаптера (Работа или Контроль). Сигналы с выхода деи|ифратора 5 поступают на входы узла 8 и мультиплексоров 12-14 и определяют режим работы адаптера. В режиме Работа производится передача информации между каналами с участием двух полуада 1теров 1 и 2. При этом связь .между полуадаптерами 1 и 2 осуществляется через мультиплексоры 12 и 13 прохождение сигналов через мультиплексор 14 запрещено и имитатор 15 не работает. В режиме Контроль производится полная автономия (без участия смежного полуадаптера и сопряженного с ним канала) проверка полуада 1тера. Во время проверки полуадаптера 1 с помощью мультиплексоров 12 И 14 устанавливается связь между полуадаптером 1 и имитатором 15. Во время проверки полуадаптера 2 подключение имитатора осуществляется с помощью мультиплексоров 13 и 14. В режиме Работа после расшифрювки команды первого канала, требующей соответствующей команды второго канала, полуадаптер 1 помещает команду . в буферный регистр 11 и выдает сигнал 1 5,8 ожидания согласования (Ожидание, согласования) , который уерез мультиплексор 13 поступает в полуадаптер 2. (Согласования требуют команды, связанные с передачей данных из одного канала в другой. Команде записи от одного канала соответствует команда считывания из другого канала и наобо рот). Полуадаптер 2 выдает во второй канал байт состояния с указателем Внимание, в ответ на который второй канал посылает в адаптер команду уточнения состояния. По этой команде полуадаптер 2 передает второму каналу содержимое буферного регистра 11, т.е. команду, присланную первым каналом. ПрограммаЦВМ, к которой подключен второй канал, определяет,- какая согласованная команда должна быть послана в адаптер и затем посылает эту команду. Если команды согласованы, полуадаптер 2 посылает в узел 8 полуадэптера 1 сигнал подтверждения согласования (Подтверждение согласования), после чего оба полуадаптера совместно выполняют команды обмена до их завершения. При этом байт информации, полученный, например, из первого канала, производящего запись, помещается в буферный регистр 11, после чего в полуадаптер 2 посылается сигнал готовности (Готов), по которому этот полуадаптер передает во второй канал этот байт информации и посылает в полуадаптер 1 сигнал подтверждения передачи информации (Подтверждение готрвности). В процессе обмену в регистре 10 формируется байт состояния, который передается в канал при выполнении начальной выборки и после завершения обмена. Узел 8 может быть реализован в виде синхронного «|и(йэового автомата. Состояние узла 8 определяется состояниями триггеров 35-39, которые изменяют свои состояния по фронту синхроимпульсов, вырабатываемых генератором 34. РХОДМОЙ дешифратор 33 в зависимости от входных сигналов узла 8 и предыдущего состояния узла 8 формирует управляющие сигналы на входах триггеров 35-39, которые определяют следующие состояния узлаd. На выходе дешифратора 40 вырабатываются сигна/м 1, соответствующие состоянию триггеров 35-39. Выходной дешифратор 41 в зависимости от состояния узла 8 и входных сигналов вырабатывает внешние управляющие си налы узла 8. По управляющим шинам канала 27 (28) на вход дешифратора 33 поступают сигналы управления канала - АДР-К, УПР-К, ВБР-К, ИНФ-К, БЛК-К, РВБ-К, РАБ-К согласно интерфейсу ввода-вывода. От дешифратора поступают сигналы Запись, Чтение Уточнить состояние, Немедленно выполняемая операция (например, Проверить ввод-вывод или Холостой ход), Работа, сформированные в результате декодирования команды обмена. По шинам 20 (21) вфежиме Работа поступают сигналы с выхода смежного полуадаптера, а в режиме Контроль - сигналы имитатора 15 полуадаптера. Сигнал Ожидание согласования вырабатывается смежным Нолуадаптером при получении им команды, требующей согласования. По этому сигналу узел 8 вырабатывает сигналы, обеспечивающие передачу в канал байта состояния с указателем Внимание. Сигнал Готов вырабаты вается смежным полуадаптером и имитйторЬм 15 после того, как в буферный регистр 11 записан байт данных для передачи. Сигналы Запись и Чтение формируются смежным полуадаптером, определяют тип выполняемой команды и используются для уста новления соответствия полученных команд. Сигнал Подтверждение согла сования вырабатывается смежным полуадаптером и имитатором 15 в ответ на сигнал Ожидание согласования после получения согласованной команды - Сигнал Окончить вырабатывается смежным полуадаптером после того, как канал, сопряженный с ним, выдал последовательность окончания. Сигнал Подтверждение готовности вырабатывается в ответ на сигнал Готовновть после того, как в кана передан байт из буферного регистра 11, Сигналы со второго выхода узла поступают на вход узла 9 и управляю коммутацией или информации из буфер ного регистра 11, или байта состоян из регистра 10, или адреса из регис ра 6 - на шины 31 -(32). На шинах 29 (30) вырабатываются сигналы управле ния абонентов ТРБ-А, АДР-А, ВБВ-А, УПР-А, ИНФ-А, РАБ-А. Сигналы с трет его выхода узла управления поступаю на вход регистра 10, где по ним про : ИЗВОДИТСЯ установка соответствукмцих разрядов байта состояния. По сигнал 35 на первом и четвертом выходах узла. 8 производится запись информации соответственно в регистры и 11. Сигналы с шестого выхода узла 8 поступают на входы мультиплексоров 13 и k, а затем в рабочем режиме - на вход смежного полуадаптера, а в режиме .Контроль - на вход имитатора 15. В режиме Контроль команда, полученная из канала, в буферный регистр не помещается. В этом режиме сигналы внутреннего сопряжения полуадаптера, смежного с проверяемым (Подтверждение согласования, Подтверждение готовности, Готов) вырабатывает имитатор 15. Для проверки полуадаптера канал (например, первый канал при проверке полуадаптера 1) посылает команду записи, в коде которой установлен признак выполнения команды в режиме Контроль. Сигнал с выхода дешифратора 5 подключает имитатор 15 через мультиплексоры 12 и 1 к первому полуадаптеру. Каждый байт информации, поступивший из канала, в ходе выполнения операции записи заносится в буферный регистр 11. После выполнения операции записи канал посылает в проверяемый полуадаптер команду считывания, при выполнении которой в канал передается информация из буферного регистра 11. Первый байт содержит информацию, переданную в последнем байте при выполнении операции записи. Значение информации в каждом последующем байте увеличивается на +V по сравнению с предыдущим. Добавление +1 к содержимому регистра 11 производится по сигналу на втором выходе имитатора 15, поступающему на счетный вход буферного регистра 11. Окончание обмена производится в режиме Контроль по инициативе канала. Имитатор полуадаптера 15 представляет собой цифровой автомат, состояния которого определяются состояниям триггеров . В режиме Контроль на вход имитатора 15 поступают сигналы проверяемого полуадаптера: Ожидание согласования, Готов, Подтверждение готовности. Чтение, Запись, Окончить, на выходе имитатора 15 формируются сигналы Подтверждение готовности, Подтверждение согласования, Готов, икмтирующие работу полуадаптера смежного с проверяемым. После получения команды, требующей согласования, проверяемый полуадаптер выдает сигнал Ожидание согласованости, по которому триггер 42 устанавливается в состояние 1, что соответствует второму состоянию узла 8. Сигнал Подтверждение согласованости с выхода триггера Ц2 поступает в проверяемый полуадаптер, кото рый сбрасывает сигнал Ожидание согласованости и переходит к циклу передачи данных. По сбросу сигнала Ожидание согласованости устанавливается триггер ijS, а затем сбрасывается триггер t2. Узел 8 переходит в третье состояние. Далее, в зависимости от команды, выполняемой пройяпяймым полуадаптером (Запись или Чтение) производятся следующие .действия. При выполнении команды за писи проверяемый полуадаптер принимает бейт данных из канала, записывает его в буферный регистр 11 и выдает сигнал Готов, свидетельствующий о готовности информации в бу ферном регистре. По сигналам Запис и Готов устанавливается триггер а затем сбрасывается триггерЧЗ :(узел 8 переходит в четвертое состоя ние). Сигнал Подтверждение готовности с выхода триггера t поступает в проверяемый полуадаптер, извещая последний, что информация из регистра 11 считана и в него можно записывать.новую информацию. По сигналу Подтверждение готовности проверяемый полуадаптер обращается в канал, за следующим байтом данных. Канал либо передает байт данных (в этом случае сигнал Окончить 0), либо отвечает последовательностью окончания операции обмена (в случае завершения передачи массива данных, указанного в команде обмена). В последнем случае проверяемый полу. адаптер выдает сигнал Окончить. После перехода из седьмого состояния в первое или третье, проверяемый полуадаптер сбрасывает сигнал Го3512тов. При этом устанавливается триггер 7 и сбрасывается триггер k. Узел 8 переходит в седьмое состояние, длительность которого определяется временем задержки элемента 59. Далее узел В переходит в третье состояние или в исходное состояние. Если проверяемый полуадаптер выполняет команду Чтение, то из третьего состояния автомат переходит в пятое состояние (по сигналам Чтение и Подтверждение готовности устанавливается триггер 5, после чего сбрасывается триггер ). Сигнал Готов с выхода триггера 45 .посту.пает в проверяемый полуадаптер, сигнализируя о готовности информации в буферном регистре. По этому сигналу проверяемый полуадаптер передает информацию из буферного регистра 11 в канал. Канал или принимает байт данных, или отвечает последовательностью окончания операции обмена (полуадап Р Формирует сигнал Окончить), после чего полуадаптер выдает сигнал Подтверждение готовности, по которому устанавливается триггер 46 и сбрасывается триггер 45. Сигнал Добавление -fl с выхода триггера 46 поступает ho шине 22 на счетный вход буферного регистра 11, где по нему к содержимому буферного регистра добавляется единица. Длительность сигнала Добавление ч-1 определяется временем задержки элемента 58. По истечении этого .времени узел 8 переходит в седьмое состояние. Переход из седьмого состояния в третье или в первое состояние описан выше. Таким образом, в предлагаемом адаптере обеспечена возможность автономной проверки каждого полуадаптера, что позволяет повысить разрешающую способность при диагностике неисправностей и сократить время поиска неисправностей.

1

m 1й

«е

fr

.

I

Ьф

&

j

h

J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР ff , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| РЕЛЕ | 1924 |

|

SU1050A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Питательный кран для вагонных резервуаров воздушных тормозов | 1921 |

|

SU189A1 |

Авторы

Даты

1983-08-23—Публикация

1981-12-10—Подача