Изобретение относится к вычисли- 1ОЙ технике, может быть использо- в многомашинных вычислительных для связи ЦВМ и является гршенствованием адаптера канал - по авт.св. № 1049895.

изобретения - повьшение про- изво41ительности адаптера.

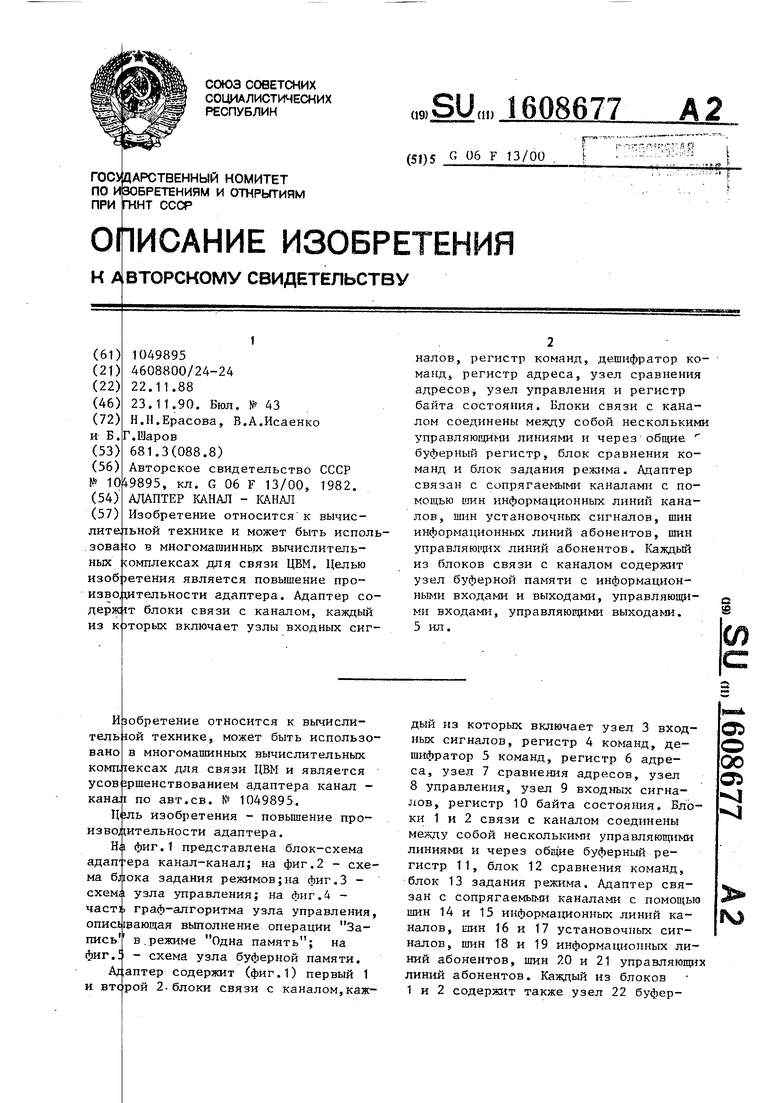

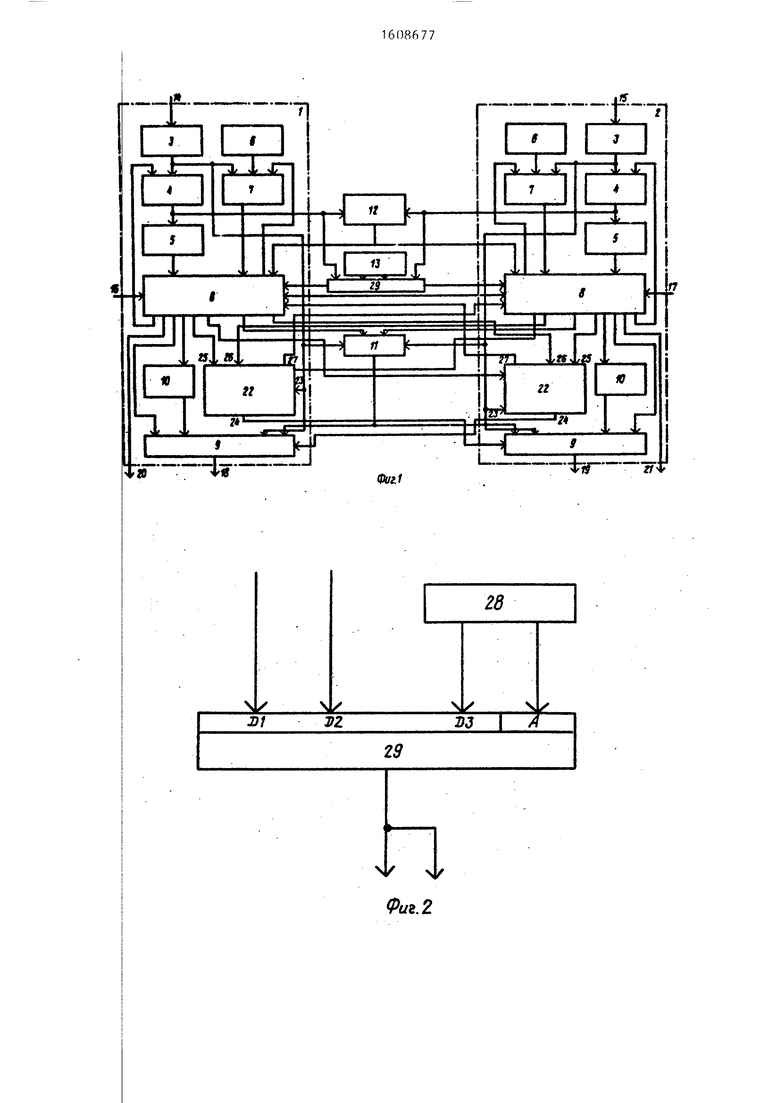

фиг.1 представлена блок-схема ера канал-канал; на фиг.2 - схе- 6jtioKa задания режимов;на фиг.З - узла управления; на фиг.4 - граф-алгоритма узла управления, опис1 1вающая вьтолнение операции За- в.режиме Одна память ; на - схема узла буферной памяти. ;аптер содержит (фиг.1) первый 1 2. блоки связи с каналом, кажтельвано

комп гексах усов канал Ц| шь

На

адап ма схема част1

пись

фиг. А; и

дый из которых включает узел 3 входных сигналов, регистр 4 команд, дешифратор 5 команд, регистр 6 адреса, узел 7 сравнения адресов, узел 8 управления, узел 9 входньгх сигналов, регистр 10 байта состояния. Блоки 1 и 2 связи с каналом соединены мехчду собой несколькими управляющими линиями и через общие буферный регистр 11, блок 12 сравнения команд, блок 13 задания режима. Адаптер связан с сопрягаемы ш каналами с помощью шин 14 и 15 информагрюнных линий каналов, шин 16 и 17 установочных сигналов, шин 18 и 19 информационных линий абонентов, шин 20 и 21 управляющих линий абонентов. Каждый из блоков 1 и 2 содержит также узел 22 буферО5

О 00

а:

гч

ной памяти с информационными входами 23 и выходами 24, управляюищми входами 25 и 26, управляющими выходами 27.

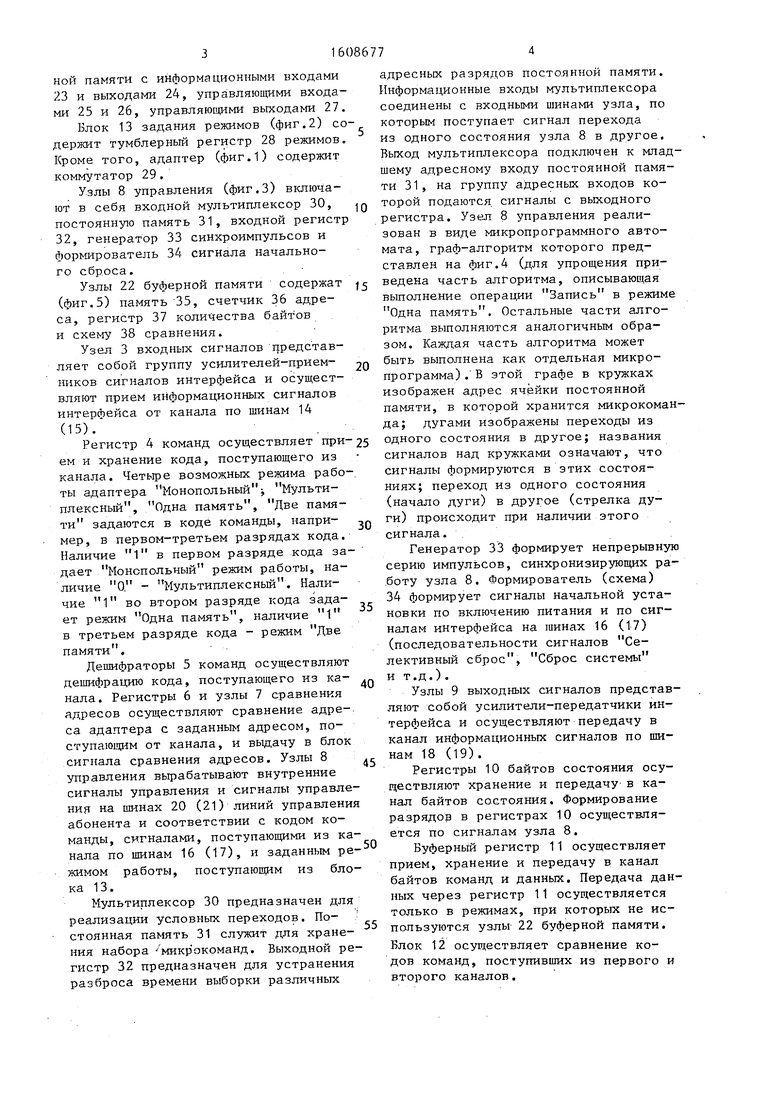

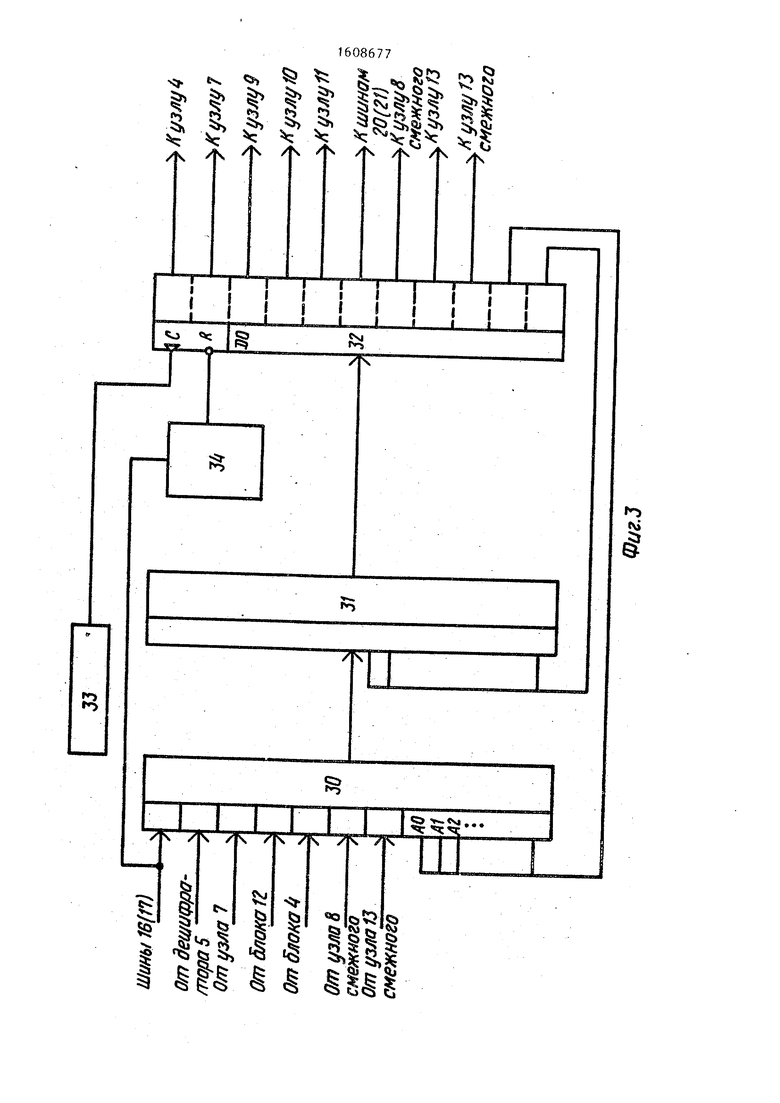

Блок 13 задания режимов (фиг.2) содерлсит тумблерный регистр 28 режимов. Кроме того, адаптер (фиг.1) содержит коммутатор 29.

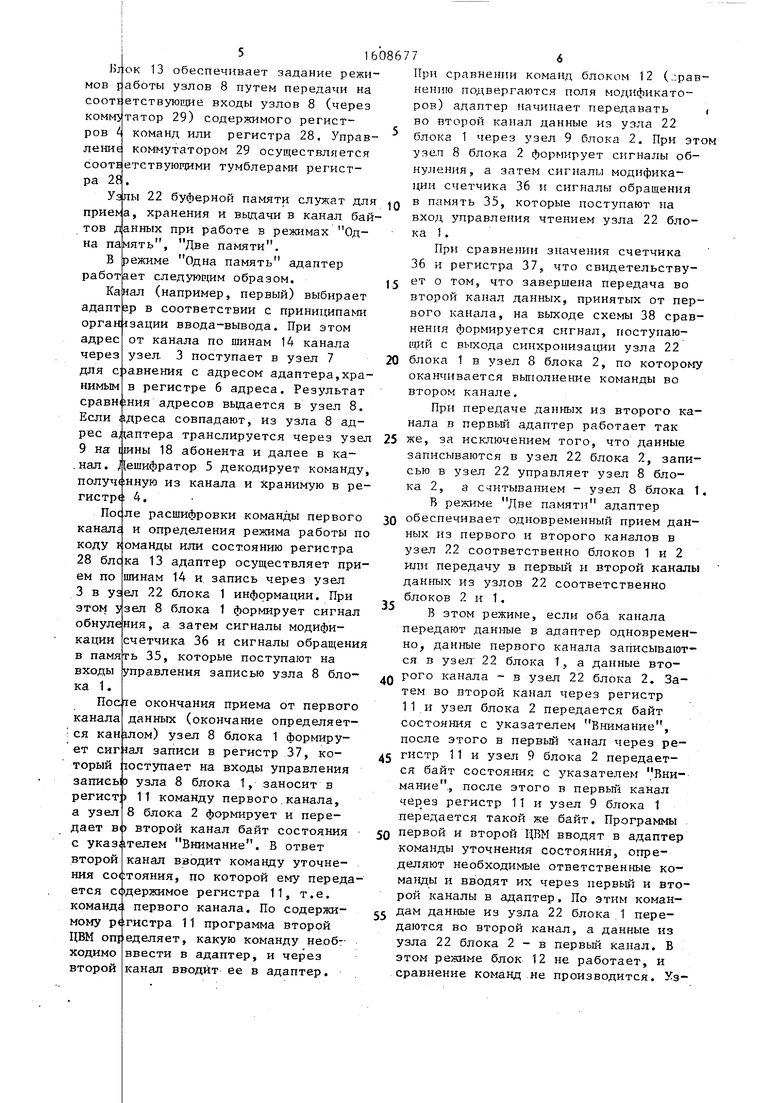

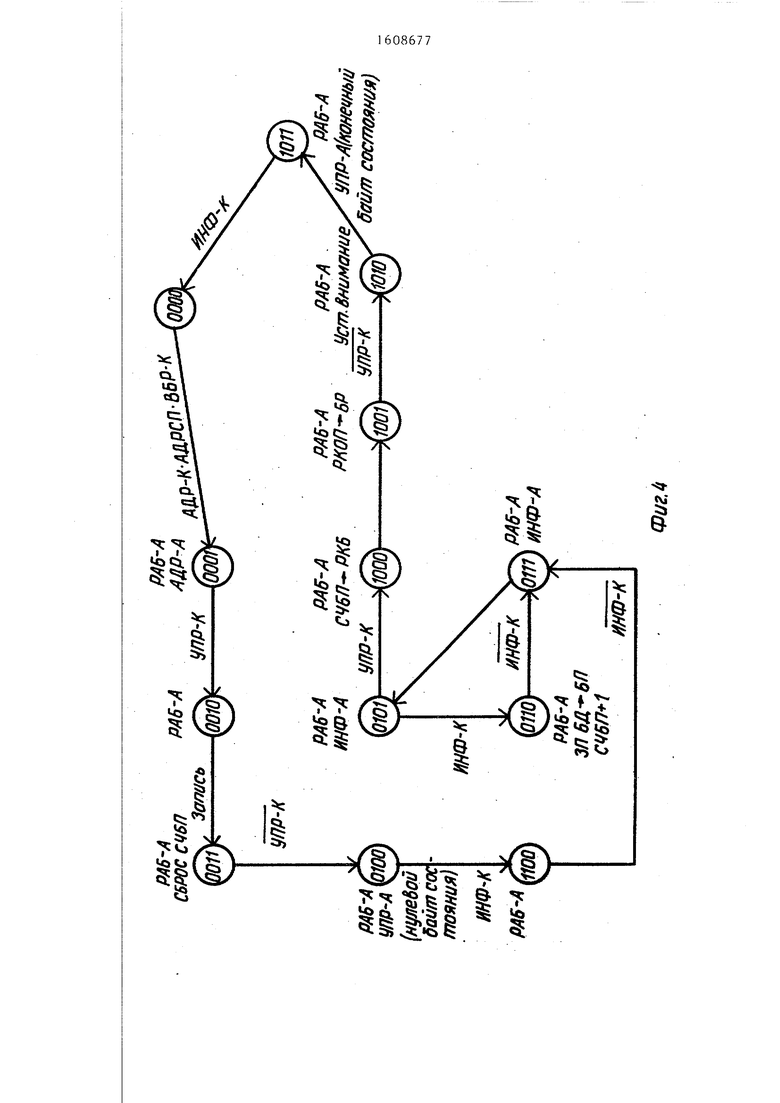

Узлы 8 управления (фиг.З) включают в себя входной мультиплексор 30, постоянную память 31, входной регистр 32, генератор 33 синхроимпульсов и формирователь 34 сигнала начального сброса.

Узлы 22 буферной памяти содержат (фиг.З) память 35, счетчик 36 адреса, регистр 37 количества байт ов и схему 38 сравнения.

Узел 3 входных сигналов представляет собой группу уснлителей-прием- НИКОВ сигналов интерфейса и осуществляют прием информационных сигналов интерфейса от канала по шинам 14

(15). .

Регистр 4 команд осуществляет при- ем и хранение кода, поступающего из канала. Четыре возможных режима работы адаптера Монопольный -, Мульти- плексньш, Одна память, Две памяти задаются в коде команды, напри- мер, в первом-третьем разрядах кода. Наличие 1 в первом разряде кода за- дает Монопольный режим работы, наличие О - Мультиплексный. Наличие 1 во втором разряде кода зада- ет режим Одна память, наличие 1 в третьем разряде кода - режим Две памяти.

Дешифраторы 5 команд осуществляют дешифрацию кода, поступающего из ка- нала. Регистры 6 и узлы 7 сравнения адресов осуществляют сравнение адреса адаптера с заданным адресом, поступающим от канала, и вьщачу в блок сигнала сравнения адресов. Узлы 8 управления вьфабатывают внутренние сигналы управления и сигналы управления на шинах 20 (21) линий управлени абонента и соответствии с кодом команды, сигналами, поступающими из нала по шинам 16 (17), и заданным ре жимом работы, поступающим из блока 13.

Мультиплексор 30 предназначен для реализации условных переходов. По- стоянная память 31 слуткит для хранения набора микр окоманд. Выходной регистр 32 предназначен для устранения разброса времени выборки различных

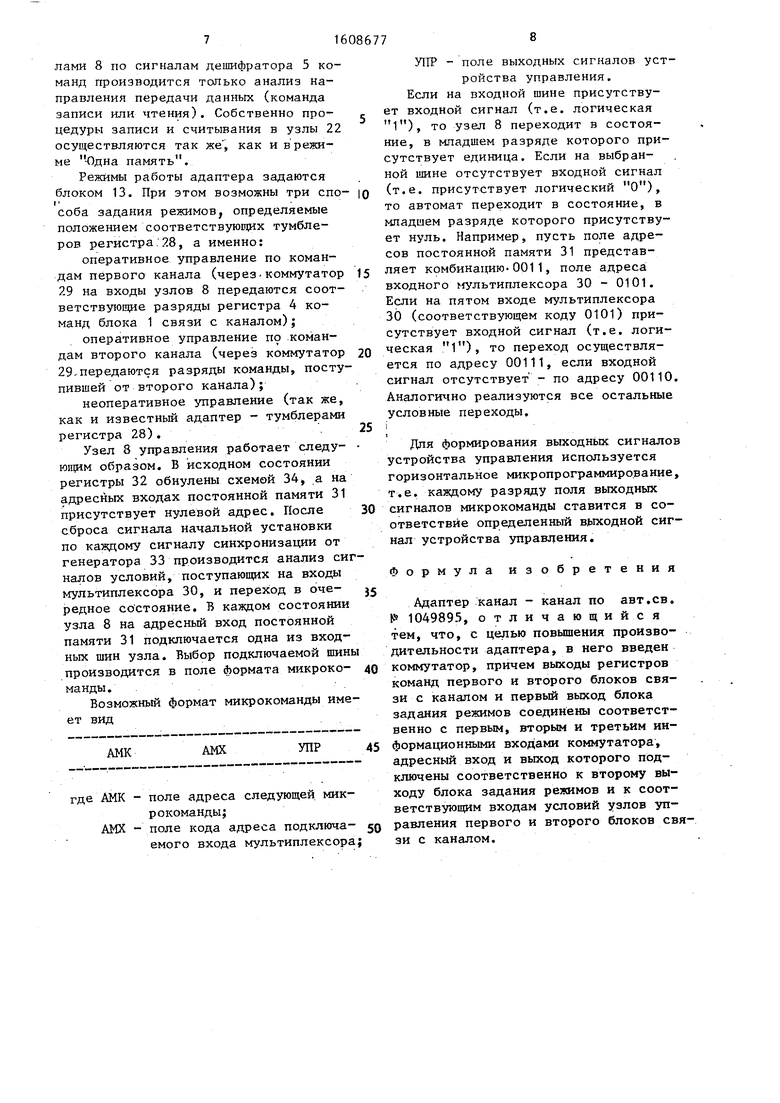

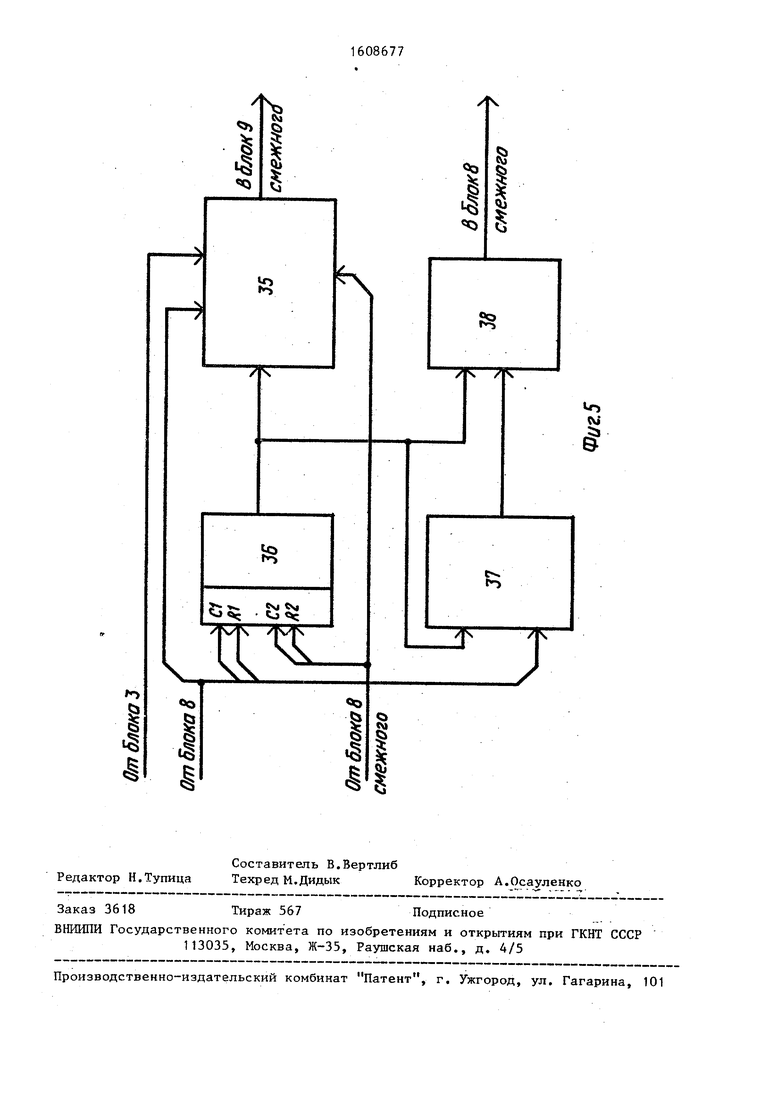

адресных разрядов постоянной памяти. Информационные входы мультиплексора соединены с входными шинами узла, по которым поступает сигнал перехода из одного состояния узла 8 в другое. Выход мультиплексора подключен к младшему адресному входу постоянной памяти 31, на группу адресных входов которой подаются, сигналы с выходного регистра. Узел 8 управления реализован в виде микропрограммного автомата, граф-алгоритм которого представлен на фиг.4 (для упрощения приведена часть алгоритма, описывающая выполнение операции Запись в режим Одна память. Остальные части алгоритма выполняются аналогичным образом. Каждая часть алгоритма может быть выполнена как отдельная микропрограмма) . В этой графе в кружках изображен адрес ячейки постоянной памяти, в которой хранится микрокомада; дугами изображены переходы из одного состояния в другое; названия сигналов над кружками означают, что сигналы формируются в этих состояниях; переход из одного состояния (начало дуги) в другое (стрелка дуги) происходит при наличии этого сигнала.

Генератор 33 формирует непрерывну серию импульсов, синхронизирующих ра .боту узла 8. Формирователь (схема) 34 формирует сигналы начальной установки по включению питания и по сигналам интерфейса на шинах 16 (17) (последовательности сигналов Селективный сброс, Сброс системы и т.д.).

Узлы 9 выходных сигналов представляют собой усилители-передатчики интерфейса и осуществляют передачу в канал информационных сигналов по шинам 18 (19).

Регистры 10 байтов состояния осуществляют хранение и передачу- в канал байтов состояния. Формирование разрядов в регистрах 10 осув1ествля- ется по сигналам узла 8.

Буферньш регистр 11 осуществляет прием, хранение и передачу в канал байтов команд и данных. Передача данных через регистр 11 осуществляется только в режимах, при которых не используются узлы 22 буферной памяти.

Блок 12 осуществляет сравнение кодов команд, поступивших из первого и второго каналов.

BJ

MOB I COOTI

:сж 13 обеспечивает задание режи- аботы узлов 8 путем передачи на етствуюЕще входы узлов 8 (через комм5(татор 29) содержимого регисткоманд или регистра 28. Управ- коммутатором 29 осуществляется соотйетствуюрщми тумблерами регистра 28

ров i ленке

Уз(лы 22 буферной памяти служат дл , хранения и выдачи в канал баданных при работе в режимах Одприе1 а

тов

на па|мять

В работает

Канал

блска

кации в памя|ть входы ка 1.

Две памяти.

режиме Одна память адаптер следуюп им образом, (например, первый) выбирает ар в соответствии с приниципами

ввода-вывода. При этом от канала по шинам 14 канала узел. 3 поступает в узел 7 с авнения с адресом адаптера,хра в регистре 6 адреса. Результат адресов вьщается в узел 8. адреса совпадают, из узла 8 ад- адаптера транслируется через узел 1ИНЫ 18 абонента и далее в ка- Дешифратор 5 декодирует команду ч(нную из канала и хранимую в ре- 4.

расшифровки команды первого и определения режима работы по команды или состоянию регистра

13 адаптер осуществляет при- шинам 14 и запись через узел ел 22 блока 1 информации. При 8 блока 1 формирует сигнал , а затем сигналы модифи- счетчика 36 и сигналы обращения

35, которые поступают на управления записью узла 8 блоадапт

организации адрес через для нимым сравнения Если рее 9 на . нал. полу:

ГИСТр{;

Пос ле каналс коду 28

ем по 3 в уз этом узел обнуления

Посте

канала ся кан ет сиг торый запиеь о регисг) а узел дает BI с

второй кия ется команда мому ЦВМ ощ ходимо второй

окончания приема от перво данных (окончание определяе шом) узел 8 блока 1 формиру- ian записи в регистр 37, ко- юступает на входы управления узла 8 блока 1, заносит в 11 команду первого.канала, 8 блока 2 формирует и пере- ) второй канал байт состояния указателем Внимание. В ответ

канал вводит команду уточне- соЛтояния, по которой ему перед содержимое регистра 11, т.е.

первого канала. По содержи- р гистра 11 программа второй еделяет, какую команду необввести в адаптер, и через канал вводит ее в адаптер.

10

При сравнении команд блоком 12 (-равнению подвергаются поля модификаторов) адаптер начинает передавать , во второй капал данные из узла 22 блока 1 через узел 9 блока 2. При этом узел 8 блока 2 формирует сигналы обнуления, а затем сигналы модификации счетчика 36 и сигналы обращения в память 35, которые поступают па вход управления чтением узла 22 блока 1 .

При сравнении значения счетчика 36 и регистра 37, что свидетельствует о том, что завершена передача во второй канал данных, принятых от первого канала, на выходе схемы 38 сравнения формируется сигнал, поступающий с выхода синхронизации узла 22 блока 1 в узел 8 блока 2, по которому оканчивается выполнение команды во втором канале.

При передаче данных из второго канала в nepobrii адаптер работает так же, за исключением того, что данные записываются в узел 22 блока 2, записью в узел 22 управляет узел 8 блока 2, а считыванием - узел 8 блока 1.

В режиме Две памяти адаптер 30 обеспечивает одновременный прием данных из первого и второго каналов в узел 22 соответственно блоков 1 и 2 или передачу в первый и второй каналы данных из узлов 22 соответственно блоков 2 и 1.

В этом режиме, если оба канала передают данные в адаптер одновремен15

20

25

35

но, данные первого канала записываются в узел 22 блока 1, а данные вто- Q рого канала - в узел 22 блока 2. Затем во второй канал через регистр 11 и узел блока 2 передается байт состояния с указателем Внимание, после этого в первый через ре- 45 гистр 11 и узел 9 блока 2 передается байт состояния с указателем Внимание., после этого в первьй канал регистр 11 и узел 9 блока 1 передается такой же байт. Программы 0 первой и второй ЦВМ вводят в адаптер команды уточнения состояния, определяют необходимые ответственные команды и вводят их через первый и второй каналы в адаптер. По этим коман- 5 дам данные из узла 22 блока 1 передаются во второй канал, а данные из узла 22 блока 2 - в первьш канал. В этом режиме блок 12 не работает, и сравнение команд не производится. У-злами 8 по сигналам дешифратора 5 команд производится только анализ направления передачи данных (команда записи или чтения). Собственно про- цедуры записи и считывания в узлы 22 осуществляются так же, как и в режиме Одна память.

Режимы работы адаптера задаются блоком 13. При этом возможны три спо- соба задания режимов, определяемые положением соответствующих тумблеров регистра.28, а именно:

оперативное управление по командам первого канала (через.коммутатор 29 на входы узлов 8 передаются соответствующие разряды регистра 4 команд блока 1 связи с каналом);

оперативное управление по .командам второго канала (через коммутатор 29.-передаются разряды команды, поступившей от второго канала);

неоперативное управление (так же, как и известный адаптер - тумблерами регистра 28),

Узел 8 управления работает следу- ющим образом. В исходном состоянии регистры 32 обнулены схемой 34, .а на адресных входах постоянной памяти 31 присутствует нулевой адрес. После сброса сигнала начальной установки по каждому сигналу синхронизации от генератора 33 производится анализ синалов условий, поступающих на входы мультиплексора 30, и переход в оче- редное состояние. В каждом состоянии узла 8 на адресный вход постоянной памяти 31 подключается одна из входных щин узла. Выбор подключаемой шин производится в поле формата микроко-

манды. .

Возможный формат микрокоманды имеет вид

АМК

АМХ

УПР

где АМК - поле адреса следующей микрокоманды;

АМХ - поле кода адреса подключа- 50 емого входа мультиплексора;

0 5 0

5

0

УГ1Р - поле выходных сигналов устройства управления. Если на входной шине присутствует входной сигнал (т.е. логическая 1), то узел 8 переходит в состояние, в мпадшем разряде которого присутствует единица. Если на выбранной шине отсутствует входной сигнал (т.е. присутствует логический О), то автомат переходит в состояние, в младшем разряде которого присутствует нуль. Например, пусть поле адресов постоянной памяти 31 представляет комбинацию.0011, поле адреса входного iyльтиплeкcopa 30 - 0101. Если на пятом входе мультиплексора 30 (соответствующем коду 0101) присутствует входной сигнал (т.е. логическая 1), то переход осуществляется по адресу 00111, если входной сигнал отсутствует - по адресу 00110. Аналогично реализуются все остальные условные переходы. i

Для формирования выходньк сигналов устройства управления используется горизонтальное микропрограммирование, т.е. каждому разряду поля выходных сигналов микрокоманды ставится в соответствие определенный вьпсодной сигнал устройства управления.

Формула изобретения

Адаптер канал - канал по авт.св. JS 1049895, отличающийся тем, что, с целью повышения производительности адаптера, в него введен коммутатор, причем выходы регистров команд первого и второго блоков связи с каналом и первый вьжод блока задания режимов соединены соответственно с первым, вторым и третьим информационными входами коммутатора, адресный вход и выход которого подключены соответственно к второму выходу блока задания режимов и к соот- ветствуюпщм входам условий узлов управления первого и второго блоков связи с каналом.

ra «M ts S

I ill

чг

ill

I

ч

r j

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1985 |

|

SU1305697A2 |

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Имитатор канала | 1984 |

|

SU1239719A2 |

| Адаптер канал-канал | 1981 |

|

SU1037235A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Имитатор канала | 1985 |

|

SU1377857A2 |

| Имитатор канала | 1985 |

|

SU1429115A2 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах для связи ЦВМ. Целью изобретения является повышение производительности адаптера. Адаптер содержит блоки связи с каналом, каждый из которых включает узлы входных сигналов, регистр команд, дешифратор команд, регистр адреса, узел сравнения адресов, узел управления и регистр байта состояния. Блоки связи с каналом соединены между собой несколькими управляющими линиями и через общие буферный регистр, блок сравнения команд и блок задания режима. Адаптер связан с сопрягаемыми каналами с помощью шин информационных линий каналов, шин установочных сигналов, шин информационных линий абонентов, шин управляющих линий абонентов. Каждый из блоков связи с каналом содержит узел буферной памяти с информационными входами и выходами, управляющими входами, управляющими выходами. 5 ил.

| № |

Авторы

Даты

1990-11-23—Публикация

1988-11-22—Подача