1

(61) 1112361

(21)4388873/24-24

(22)03.03.88

(46) 23.09.89. Бюл. № 35 (72) В.А.Исаенко, Е.А.Николаева, А.А.Самчинский, Б.Г.Шаров и Н.Н.Ерасова .(53) 1.81 325 (088.8)

(56)Авторское свидетельство СССР № 1112361, кл. G 06 F 3/04, 1984.

(54) АДАПТЕР КАНАЛ - КАНАЛ

(57)Изобретение относится к вычислительной технике и может быть использовано для сопряжения ЭВМ в многомашинных вычислительных комплексах. Целью изобретения является повышение пропускной способности адаптера при выполнении канальных программ, содержащих несколько команд, за счет сокращения времени на передачу и анализ байтов состояния.Сокращение времени достигается путем запрета передачи байтов состояния ло второй и последующим командам канальной программы, для чего в адаптере выходы регистров команд первого и второго полуадаптеров подключены соответственно к входам узлов управления первого и второго полуадаптеров. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1981 |

|

SU1037235A1 |

| Адаптер канал-канал | 1983 |

|

SU1112361A2 |

| Адаптер канал-канал | 1982 |

|

SU1067492A1 |

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Адаптер канал-канал | 1983 |

|

SU1144114A1 |

| Адаптер канал-канал | 1985 |

|

SU1259276A1 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Имитатор канала | 1985 |

|

SU1429115A2 |

| Адаптер канал-канал | 1985 |

|

SU1305697A2 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения ЭВМ в многомашинных вычислительных комплексах. Целью изобретения является повышение пропускной способности адаптера при выполнении канальных программ, содержащих несколько команд, за счет сокращения времени на передачу и анализ байтов состояния. Сокращение времени достигается путем запрета передачи байтов состояния по второй и последующим командам канальной программы, для чего в адаптере выходы регистров команд первого и второго полуадаптеров подключены соответственно к выходам узлов управления первого и второго полуадаптеров.

Изобретение относится к вычислительной технике, может использоваться для сопряжения ЭВМ в многомашинных вычислительных комплексах и является усовершенствованием устройства по авт.св. № 1112361.

Целью изобретения является повышение пропускной способности адаптера при выполнении канальных программ, содержащих несколько команд, за счет сокращения времени на передачу и анализ байтов состояния.

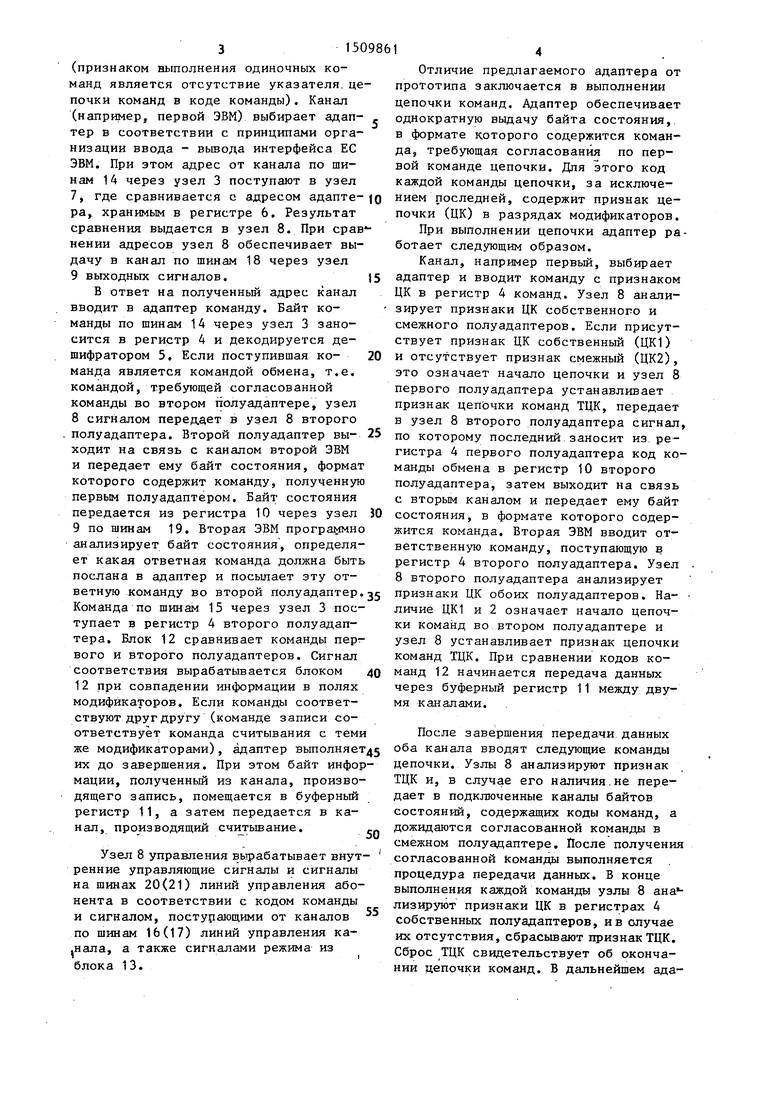

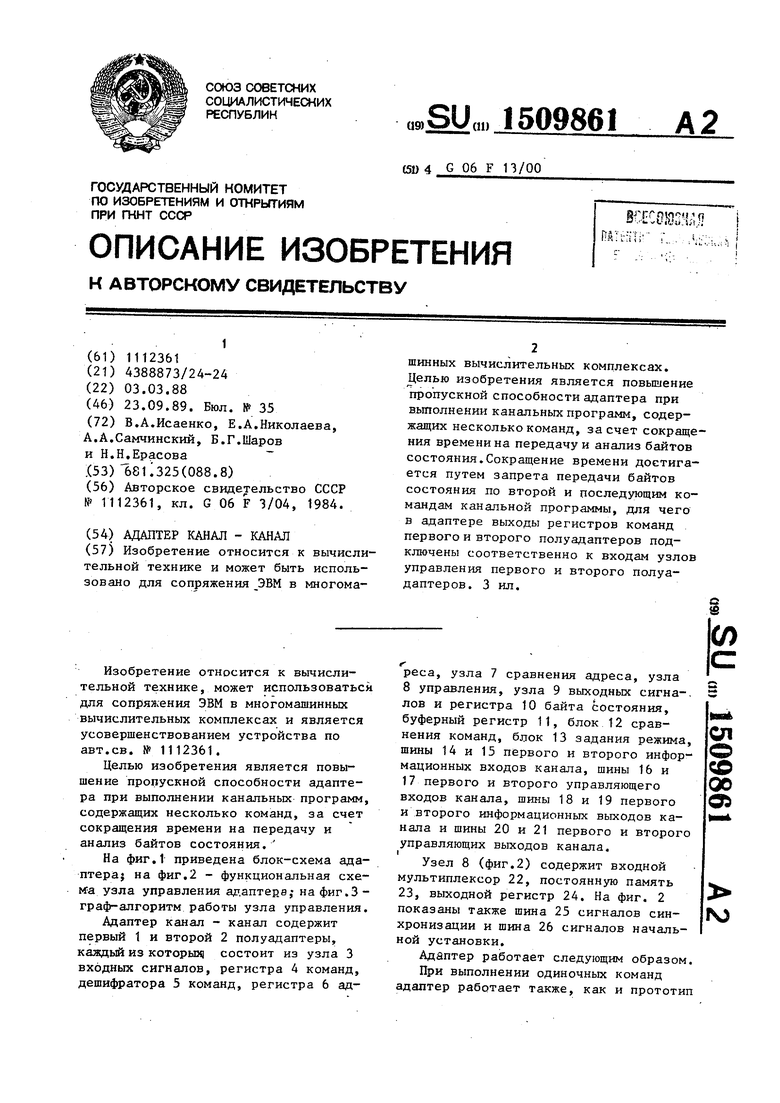

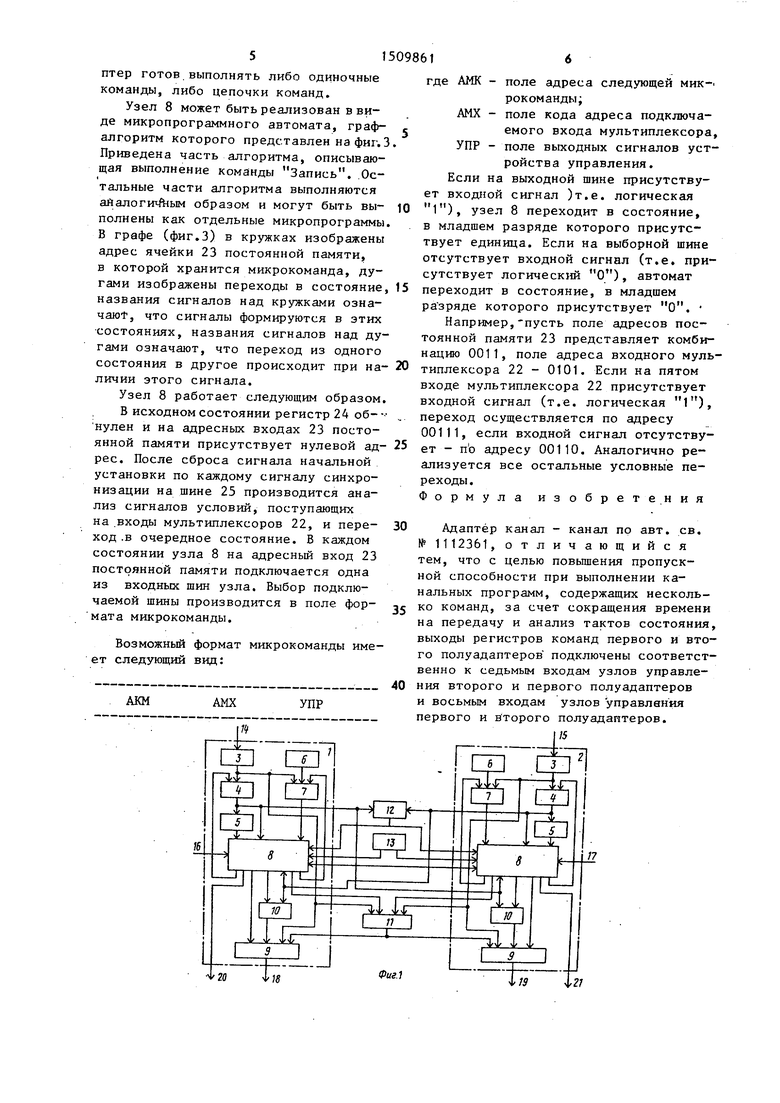

На фиг.1 приведена блок-схема адаптера} на фиг.2 - функциональная схе- узла управления а. на фиг.З - граф-алгоритм работы узла управления.

Адаптер канал - канал содержит первый 1 и второй 2 полуадаптеры, калздый из которых состоит из узла 3 входных сигналов, регистра 4 команд, дешифратора 5 команд, регистра 6 адреса, узла 7 сравнения адреса, узла 8 управления, узла 9 выходных сигна-. лов и регистра 10 байта состояния, буферный регистр 11, блок 12 сравнения команд, блок 13 задания режима, шины 14 и 15 первого и второго информационных входов канала, шины 16 и 17 первого и второго управляющего входов канала, шины 18 и 19 первого и второго информационных выходов канала и шины 20 и 21 первого и второго управляющих выходов канала.

Узел 8 (фиг.2) содержит входной мультиплексор 22, постоянную память 23, выходной регистр 24. На фиг. 2 показаны также шина 25 сигналов синхронизации и шина 26 сигналов начальной установки.

Адаптер работает следующим образом.

При выполнении одиночных команд адаптер работает также, как и прототип

ел

;о

00

Од

hj

31509861

(признаком выполнения одиночных коанд является отсутствие указателя, цеочки команд в коде команды). Канал (например, первой ЭВМ) выбирает адап- . ер в соответствии с принципами оргаизации ввода - вьшода интерфейса ЕС ВМ. При этом адрес от канала по шиам 14 через узел 3 поступают в узел 7, где сравнивается с адресом адапте- ю а, хранимым в регистре 6, Результат сравнения выдается в узел 8. При сравении адресов узел 8 обеспечивает выачу в канал по шинам 18 через узел 9 выходных сигналов.15

В ответ на полученный адрес канал вводит в адаптер команду. Байт команды по шинам 14 через узел 3 заносится в регистр 4 и декодируется дешифратором 5. Если поступившая ко- 20 манда является командой обмена, т.е. командой, требующей согласованной команды во втором полуадаптере, узел

8сигналом передает в узел 8 второго

полуадаптера. Второй полуадаптер вы- 25 ходит на связь с каналом второй ЭВМ и передает ему байт состояния, формат которого содержит команду, полученную первым полуадаптером. Байт состояния передается из регистра 10 через узел Ю

9по шинам 19. Вторая ЭВМ программно анализирует байт состояния, определяет какая ответная команда должна быть послана в адаптер и посылает эту ответную команду во второй полуадаптер.35 Команда по шинам 15 через узел 3 поступает в регистр 4 второго полуадаптера. Блок 12 сравнивает команды пер вого и второго полуадаптеров. Сигнал соответствия вырабатывается блоком 40 12 при совпадении информации в полях модификаторов. Если команды соответствуют друг другу (команде записи соответствует команда считывания с теми же модификаторами), адаптер вьшолняетдз их до завершения. При этом байт информации, полученный из канала, производящего запись, помещается в буферный регистр 11, а затем передается в канал, производящий считьшание. „

Узел 8 управления вьфабатывает внут- ренние управляющие сигналы и сигналы на шинах 20(21) линий управления абонента в соответствии с кодом команды и сигналом, поступающими от каналов по шинам 16(17) линий управления ка- .нала, а также сигналами режима из блока 13.

Отличие предлагаемого адаптера от прототипа заключается в выполнении цепочки команд. Адаптер обеспечивает однократную выдачу байта состояния,, в формате которого содержится команда, требующая согласования по первой команде цепочки. Для этого код каждой команды цепочки, за исключением последней, содержит признак цепочки (ЦК) в разрядах модификаторов.

При выполнении цепочки адаптер работает следующим образом.

Канал, например первый, выбирает адаптер и вводит команду с признаком ЦК в регистр 4 команд. Узел 8 анализирует признаки ЦК собственного и смежного полуадаптеров. Если присутствует признак ЦК собственный (ЦК1) и отсутствует признак смежный (ЦК2), это означает начало цепочки и узел 8 первого полуадаптера устанавливает признак цепочки команд ТЦК, передает в узел 8 второго полуадаптера сигнал по которому последний заносит из регистра 4 первого полуадаптера код команды обмена в регистр 10 второго полуадаптера, затем выходит на связь с вторым каналом и передает ему байт состояния, в формате которого содержится команда. Вторая ЭВМ вводит ответственную команду, поступающую в регистр 4 второго полуадаптера. Узел 8 второго полуадаптера анализирует признаки ЦК обоих полуадаптеров. На- личие ЦК1 и 2 означает начало цепочки команд во втором полуадаптере и узел 8 устанавливает признак цепочки команд ТЦК. При сравнении кодов команд 12 начинается передача данных через буферный регистр 11 между двумя каналами.

После завершения передачи данных оба канала вводят следующие команды цепочки. Узлы 8 анализируют признак ТЦК и, в случае его наличия.не передает в подключенные каналы байтов состояний, содержащих коды команд, а дожидаются согласованной команды в смежном полуадаптере. После получения согласованной Команды выполняется процедура передачи данных. В конце выполнения каждой команды узлы 8 ана лизируют признаки ЦК в регистрах 4 собственных полуадаптеров, ив случае их отсутствия, сбрасьшают признак ТЦК. Сброс ТЦК свидетельствует об окончании цепочки команд. В дгшьнейшем адагами изображены переходы в состояние, 15 переходит в состояние, в младшем названия сигналов над кружками ознара зряде которого присутствует О

чают, что сигналы формируются в этих состояниях, названия сигналов над дугами означают, что переход из одного

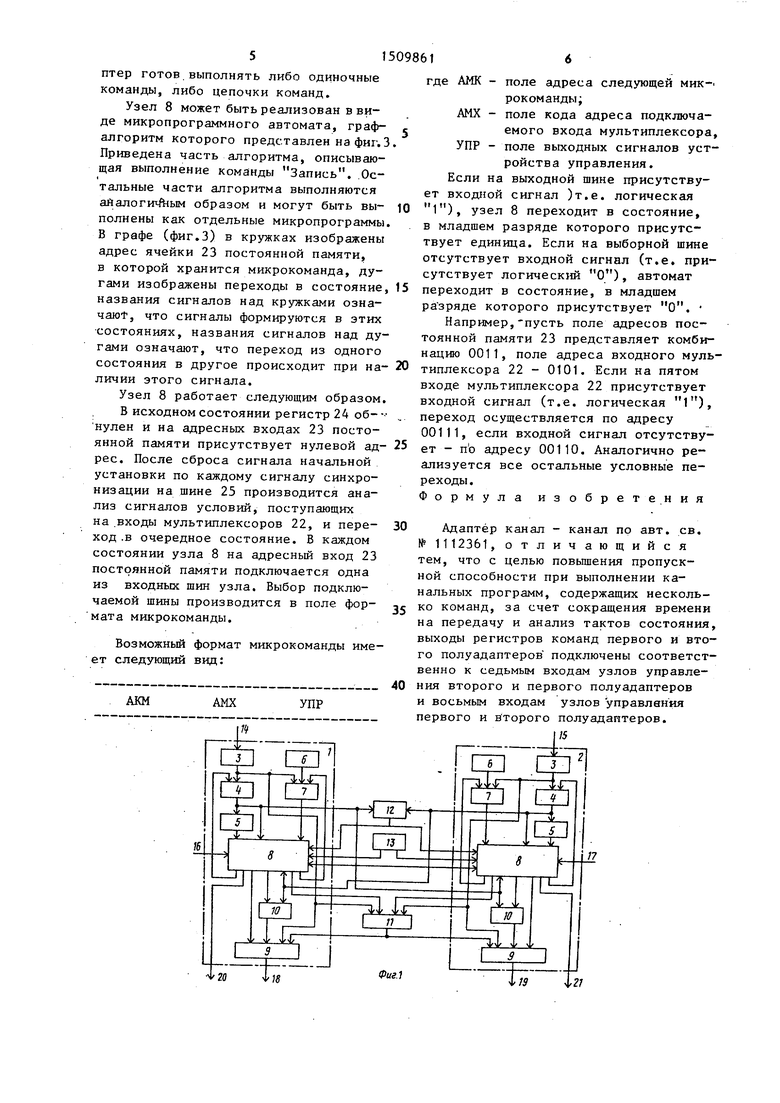

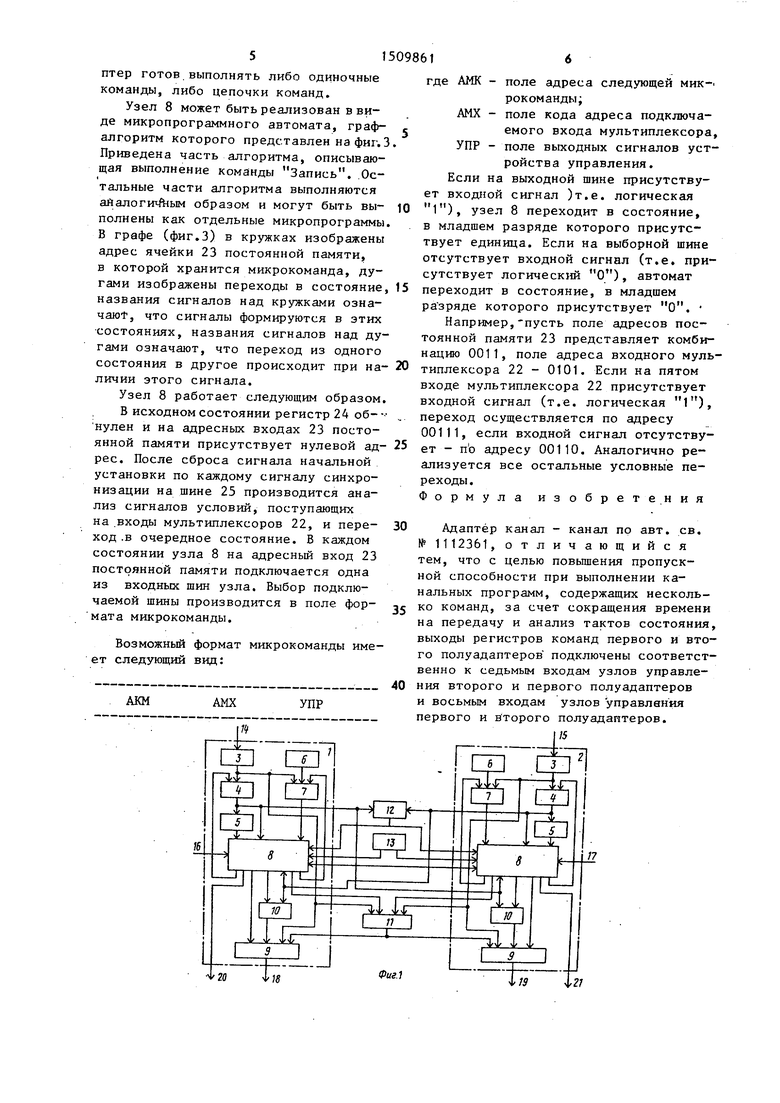

Например, пусть поле адресов постоянной памяти 23 представляет комбинацию 0011, поле адреса входного мульсостояния в другое происходит при на- 20 типлексора 22 - 0101. Если на пятом личии этого сигнала.входе мультиплексора 22 присутствует

Узел 8 работает следующим образом. входной сигнал (т.е. логическая 1), В исходном состоянии регистр 24 об-- переход осуществляется по адресу нулен и на адресных входах 23 посто- 00111, если входной сигнал отсутству- янной памяти присутствует нулевой ад- 25 ет - п о адресу 00110. Аналогично ре- рес. После сброса сигнала начальной установки по каждому сигналу синхронизации на шине 25 производится анализ сигналов условий, поступающих на .входы мультиплексоров 22, и переход .в очередное состояние. В каждом состоянии узла 8 на адресный вход 23 постоянной памяти подключается одна из входных шин узла. Выбор подключаемой шины производится в поле формата микрокоманды.

ализуется все остальные условные переходы . Формула изобретения

30

Адаптер канал - канал по авт. св. № 1112361, отличающийся тем, что с целью повышения пропускной способности при выполнении канальных программ, содержащих несколь35 ко команд, за счет сокращения времени на передачу и анализ тактов состояния выходы регистров команд первого и вто- го полуадаптеров подключены соответственно к седьмым входам узлов управлеВозможный формат микрокоманды имеет следующий вид:

АКМ

АМХ

УПР

переходит в состояние, в младшем

ра зряде которого присутствует О

Например, пусть поле адресов постоянной памяти 23 представляет комбинацию 0011, поле адреса входного мульвходной сигнал (т.е. логическая 1), переход осуществляется по адресу 00111, если входной сигнал отсутству- ет - п о адресу 00110. Аналогично ре-

ализуется все остальные условные переходы . Формула изобретения

входной сигнал (т.е. логическая 1), переход осуществляется по адресу 00111, если входной сигнал отсутству- ет - п о адресу 00110. Аналогично ре-

Адаптер канал - канал по авт. св. № 1112361, отличающийся тем, что с целью повышения пропускной способности при выполнении канальных программ, содержащих несколько команд, за счет сокращения времени на передачу и анализ тактов состояния, выходы регистров команд первого и вто- го полуадаптеров подключены соответственно к седьмым входам узлов управления второго и первого полуадаптеров и восьмым входам узлов управления первого и второго полуадаптеров.

Tflft-Л

АЯР-К-ААРСП-ВВР-К .двр-к

mp f

(ВС 0}

ТРб-А Осоеда- Т9Ж2 PAS-А « Осост

АМР-А

Wftr

гат2

фиг.

Авторы

Даты

1989-09-23—Публикация

1988-03-03—Подача