через общие буферный регистр 11, блок 12 сравнения команд и блок 13 задания режима. Адаптер связан с сопрягаемыми каналами с помощью ишн 14 и

15информационных линий каналов, шин

16и 17 управляющих линий каналов, шин 18 и 19 информационных ЛИНИРГ абонентов, шин 20 и 21 управляющих линий абонентов. Каждый из блоков 1, 2 связи с каналом содержит узел 22 буферной памяти, включающий коммутаторы управляющих сигналов записи и чтения, входной информации, счетчик

1

Изобретение относится к вычислительной технике, может быть использовано в многомашинных вычислительных комплексах для связи цифровых вычислительных машин (ЦВМ) и явля- ется усовершенствованием устройства по авт.св. № 1049895.

{елью изобретения является повышение производительности адаптера.

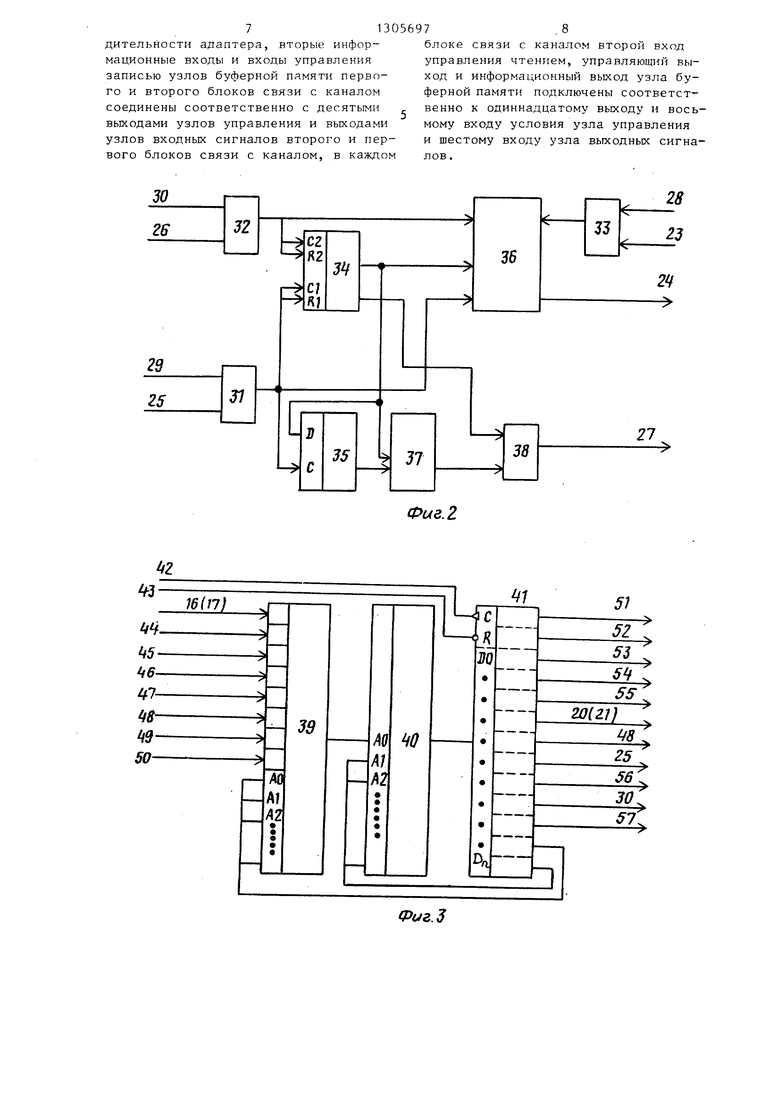

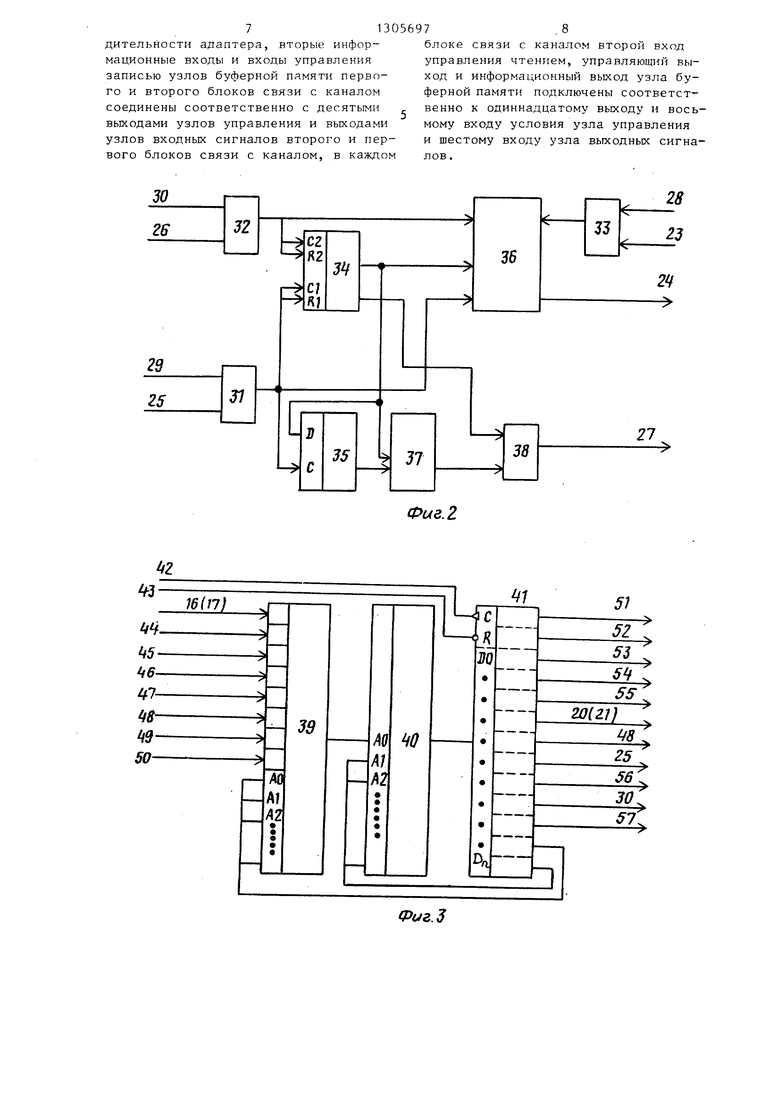

На фиг.1 представлена блок-схема адаптера, на фиг.2 - функциональная узла буферной памяти; на фиг.3- функциональная схема узла управления на фиг.4 - граф состояний и переходов узла управления.

даптер содержит (фиг.1) первый и второй блоки t и 2 связи с каналом каждый из которых включает узел 3 выходных сигналов, регистр 4 команд, дешифратор 5 команд, регистр 6 адре- са, узел 7 сравнения адресов, узел 8 упрс1вления, узел 9 выходных сигналов регистр 10 байта состояния.

Блоки 1 и 2 связи с каналом сое- дине:ны между собой управляющими линиями и через общие буферный регистр 11, блок 12 сравнения команд и блок 13 задания режима. Адаптер связан с сопр Ягаемыми каналами с помощью шин 4 к 15 информационных линий каналов шин 16 и 17 управляющих линий каналов, шин 18 и 19 информационных линий абонентов, шин 20 и 21 управляю- 1Г(шс линий абонентов.

Каждый из блоков1 и 2 содержит узел 22 буферной памяти с первым информационным входом 23 и выходом

адреса, регистр количества байтов, память, схему сравнения, элемент ИЛИ. Узел 8 управления имеет входной мультиплексор, постоянную память, выходной регистр. Сущность изобретения в обеспечении возможности использования общего объема памяти, узлов буферной памяти для передачи больших массивов информации по одной команде, что позволяет сократить затраты времени на установление связи с каналами и повысить производительность адаптера и вычислительного комплекса в целом. 4 ил.

5

5

5

0

24, первыми управляющими входами записи 25 и чтения 26, управляющим входом 27, вторым информационным входом 28, вторыми управляющими входами записи 29 и чтения 30.

Узел 22 буферной памяти содержит (фиг.2) коммутаторы управляющих сигналов записи 31 и чтения 32, коммутатор 33 входной информации, счетчик 34 адреса, регистр 35 количества байтов, память 36, схему 37 сравнения, элемент ИЛИ 38.

Узел 8 управления содержит входной мультиплексор 39, постоянную память 40, выходной регистр 41. На фиг.З показаны также шина 42 сигналов синхронизации, шина 43 начальной установки и шины 44-57 входов и выходов узла 8.

Мультиплексор 39 предназначен для реализации условных переходов. Постоянная память 40 служит для хранения набора микрокоманд Выходной регистр 41 предназначен для устранения разбора времени выборки различных адресных разрядов постоянной памяти.

Информационные входы мультиплексора 39 соединены с входными шинами узла, по которым поступают сигналы перехода из одного состояния узла 8 в другое. Выход мультиплексора 39 подключен к младшему адресному входу постоянной памяти 40, на группу адресных входов, которой подаются сигналы с выходного регистра.

Узел 8 реализован в виде микропрограммного автомата, граф-алгоритм которого представлен на фиг.4. Приведена часть алгоритма, описывающая выполнение операвди Запись в ре- жиме Расширенная память. Остальные части алгоритма вьтолняются аналогичным образом. Каждая часть алгоритма может быть выполнена как отдельная микропрограмма. В графе фиг.А вкруж- ках изображен адрес ячейки постоянной памяти 40, в которой хранится микрокоманда, дугами изображены переходы из одного состояния в другое, названия сигналов над, кружками оз- начают, что сигналы формируются в этих состояниях, название сигналов над дугами означают, что переход из одного состояния (начало дуги) в другое (стрелка дуги) происходит при наличии этого сигнала.

Узлы 3 выходных сигналов представляют собой группу усилителей-приемников сигналов интерфейса и осуществляют прием информационных сигналов интерфейса от канала по шинам 14(15)

Регистр 4 и дешифратор 5 команд осуществляют прием, хранение и дешифрацию кода, поступающего из канала.

Регистры 6 и узлы 7 сравнения адреса осуществляют сравнение адреса с заданным адресом, поступившим в канал, и вьщачу в канал заданного адреса.

Узлы 8 управления вьфабатывают внутренние сигналы управления и сигналы управления на шинах 20(21) линий управления абонента в соответствии с кодом команды, сигналами, по- ступающими из канала по шинам 16(17) и сигналами блока 13 задания режимов

Узлы 9 выходных сигналов представляют собой усилители-передатчики интерфейса и осуществляют передачу в канал информационных сигналов по шинам 18(19).

Регистр 10 байтов состояния осуществляют хранение и передачу в канал байтов состояния. Формирование разрядов в регистрах 10 осуществляется по сигналам узлов 8.

Буферный регистр 11 осуществляет прием, хранение и передачу в канал байтов команд и данных. Передача

данных через регистр 4 осуществляется только в режимах, при которых не используются узлы 22 буферной памяти.

Клок 12 осуществляет сравнение кодов команд, поступивших из пер пего и второго каналов. Блок 13 представляет собой тумблерный регистр, задающий пять режимов работы: Монопольный, Мультиплексный, Одна память, Две памяти, Расширень ая память. Узлы 22 буферной памяти служат для приема, хранения и вьщачи в канал байтов данных.

Адаптер канал - канал работает в пяти режимах, задаваемых блоком 13. В режимах Ь онопольный, Мультиплексный, Одна память и Две памяти адаптер работает так же, как и известный адаптер.

В режиме Расширенная память предлагаемый адаптер работает следующим образом.

Канал (например, первый) выбирает адаптер в соответствии с принципами организации ввода-вывода. При этом адрес от канала по шинам 14 канала через узел 3 поступает в узел

7для сравнения с адресом адаптера, хранимым в регистре 6 адреса. Результат сравнения адресов выдается в узел 8. Если адреса совпадают, то из узла 7 вьщается ответный адрес адаптера на шины 18 и далее в канал.

Дешифратор 5 декодирует команду, полученную из канала и хранимую в регистре 4.

После расшифровки команды первого канала адаптер осуществляет прием по шинам 14 и запись через узел 3 в узел 22 блока 1 информации. При этом узел 8 блока 1 формирует сигнал обнуления, а затем сигналы модификации счетчика 34 и сигналы обращения в память 36, которые поступают на входы 25 узла 22 блока 1.

После заполнения всего- объема памяти 36 счетчик 34 формирует сигнал переполнения, который через элемент ИЛИ 38 по шине 27 поступает в узел

8блока 1. По этому сигналу узел 8 блока 1 продолжает запись информации в узел 22 блока 2. При этом информация по шинам 28, сигналы управления записью по шинам 29 поступают в узел 22 блока 2 из узла 8 блока 1.

После окончания приема от первого канала данных (окончание определяется каналом) узел 8 блока 1 формирует сигнал записи в регистр 35, который поступает на входы 29 узла 22 блока 2, заносит в регистр 11 команду пер}.iorc канала, a узел 8 блока 2 формирует и передает во второй канал байт состояния с указателем Внимание. В ответ второй канал вводит команду уточнения состояния, по которой ему передается содержимое регистра 11, т.е. команда первого канала. По содержимому регистра 11 программа второй ЦВМ определяет, какую команду необходимо ввести в адаптер, и через второй канал вводит ее в адаптер. При сравнении команд блоком 12 (сравнению подвергаются поля модификаторов) адаптер начинает передавать во второй канал данные из узла 22 блока 1 через узел 9 блока 2. При этом

узел 8 блока 2 формирует сигнал об-

нуления, а затем сигналы модификации счетчика 34 и сигналы обращения в память 36, которые поступают на вхо- ды 25 узла 22 блока 1.

После считывания всего объема памяти 36 счетчик 34 формирует сигнал переполнения, который через элемент ИЛИ 38 по шине 27 поступает в узел 8 блока 2. По этому сигналу узел 8 блока 2 продолжает считывание информации из узла 22 блока 2 и передачу ее во второй канал через узел 9 блока 2 При этом сигналы управления чтением в узел 22 блока 2 поступают по шинам 30 из узла 8 блока 2.

При сравнении значения счетчика 34 и регистра 35, что свидетельству- ет о завершении передачи во второй канал данных, принятых от первого канала, на выходе схемы 37 сравнения формируется сигнал, поступающий через элемент ИЛИ 38 с вькода 27 узла 22 блока 2 в узел 8 блока 2, по ко- торому оканчивается выполнение команды во втором канале.

Коммутаторы 31,32 и 34 обеспечивают коммутацию сигналов управления записью и чтением информации, посту- пающих на входы узла 22 либо из блока 1, либо из блока 2 (с выходов узла 8 и узла 3).

При передаче данных из второго канала в первый адаптер работает так же, за исключением того, что запись информации осуществляется сначала в узел 22 блока 2, а затем в узел 22 блока 1 под управлением узла 8 блока 2, а чтение - сначала из узла 22 бло КЗ 2, а затем из узла 22 блока 1 под управлением узла 8 блока 1.

Узел 8 управления работает следующим образом.

В исходном состоянии рег истр 4 обнулен и на адресных входах постоянной памяти 40 присутствует нулевой адрес. После сброса сигнала начальной установки по каждому сигналу синхронизации на шине 42 гфоизводится анализ сигналов условий, поступающих на входы мультиплексора 39, и переход в очередное состояние.

В каждом состоянии узел 8 на адресный вход постоянной памяти 40 подключается одна из входных шин узла.

Выбор подключаемой шины производится в поле формата микрокоманды.

Возможньй формат микрокоманды имеет следуюпшй вид:

АКХ

УПР

где АМК - поле адреса следующей микрокоманды;

АМХ - поле кода адреса подключаемого входа мультиплексора ,

УПР - поле выходных сигналов устройства управления. Если на выходной шине присутствует входной сигнал (т.е. логическая 1), то узел 8 переходит в состояние, в мпадшем разряде которого присутствует единица. Если на выборной отсутствует входной сигнал (т.е. присутствует логический О), то автомат переходит в состояние, в младшем разряде которого присутствует ноль.

Например, пусть поле адресов постоянной памяти 40 представляет комбинацию 0011, поле адреса входного мультиплексора 39 - 0101. Если на пятом входе мультиплексора 39 присутствует входной сигнал (т.е. логическая 1) , то переход осуществляется по адресу 00111, если входной сигнал отсутствует осуществляется по адресу 00110. Аналогично реализуются все остальные условные переходы.

Для формирования выходных сигналов устройства управления используется горизонтальное микропрограммирование, т.е. каждому разряду поля выходных сигналов микрокоманды ставится в соответствие определенный выходной сигнал устройства управления.

Формула изобр. етени

Адаптер канал - канал по авт.св. № 1049895, отличающийся тем, что, с целью повышения производительностн адаптера, вторые информационные входы и входы управления записью узлов буферной памяти первого и второго блоков связи с каналом соединены соответственно с десятыми выходами узлов управления и выходами узлов входных сигналов второго и первого блоков связи с каналом, в каждом

блоке связи с каналом второй вход управления чтением, управляющий выход и информационный выход узла буферной памяти подключены соответственно к одиннадцатому выходу и восьмому входу условия узла управления и шестому входу узла выходньк сигналов.

Фиг.2

Фиг.З

«Slili

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

| Имитатор канала | 1984 |

|

SU1239719A2 |

| Адаптер канал-канал | 1981 |

|

SU1037235A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

| Имитатор канала | 1985 |

|

SU1377857A2 |

Изобретение относится к вычислительной технике и может быть ис- лользовано в многомашинных вычисли16 тельных комплексах для связи цифровых вычислительных машин (ЦВМ). Цель изобретения - повышение производительности адаптера. Адаптер канал- канал содержит первый и второй блоки 1 и 2 связи с каналом, каждый из которых имеет узел 3 выходных сигналов, регистр 4 команд, дешифртор 5 команд, регистр 6 адреса, узел 7 сравнения, адресов, узел 8 управления, узел 9 выходных сигналов, регистр 10 байта состояния. Блоки 1 и 2 связи с каналом соединены между собой несколькими управляюшкми линиями и 00 о 01 Oi со N)

Р(2дактс р С.Пекарь

Составитель В.Вертлиб

Техред Л.КравчукКорректор Л.Патай

Заказ 1 53/47Тираж 673Подписное

БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-30—Подача