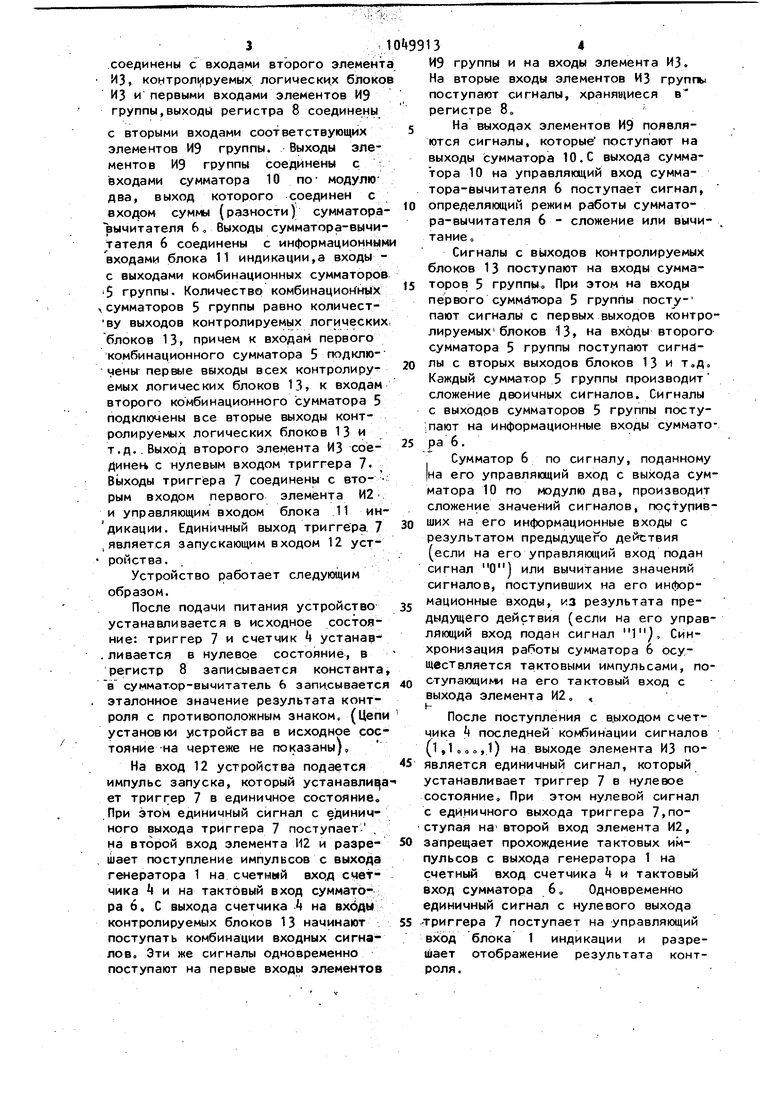

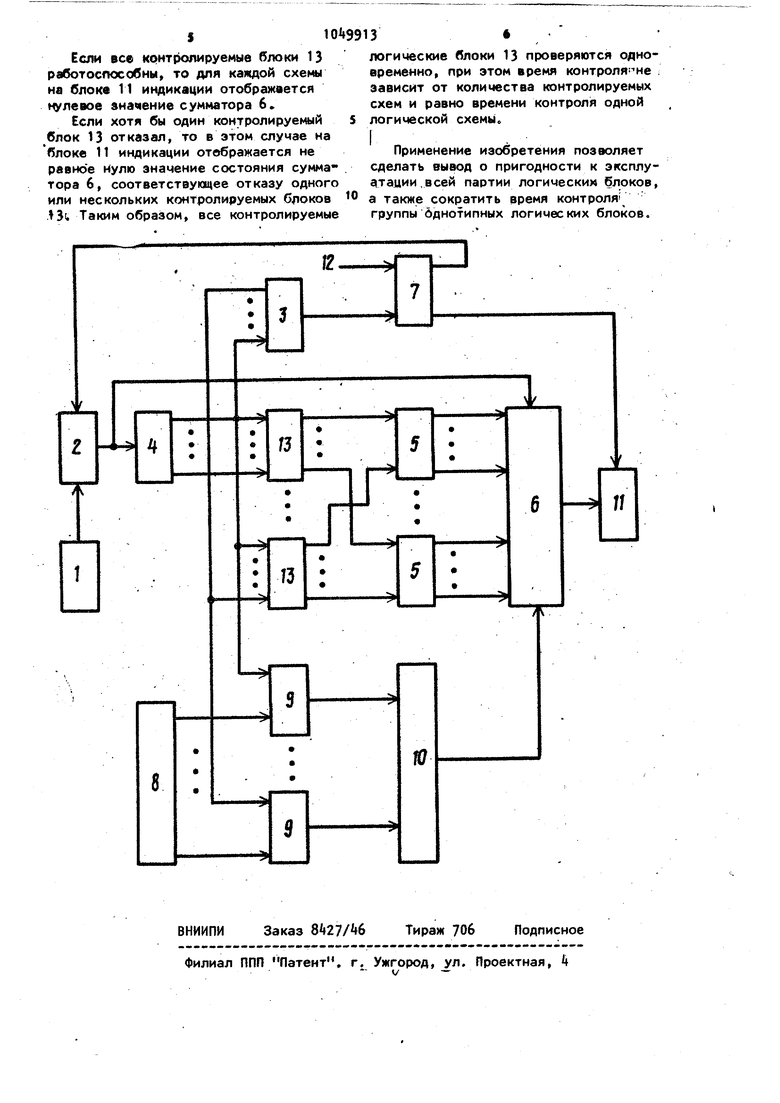

} Изобретение относится к вычислительной технике и может быть использовано для контроля логических схем при испытаниях. Испытания могут прои водиться по методу однократной выбор ки, когда из партии однотипных логи ческих схем испытываются К логически схем; При этом, если из выборки К ло гических схем хотя бы одна отказала, бракуется вся партия схем, В случае, если все К логических схем в выборке работоспособности - партия принимает ся. Известно устройство для контроля логических блоков, содержащее мульти плексор, блок управления, блок хране ния эталонных выходных наборов, блок хранения эталонных входных выборов, на капливающий сумматор - l . Однако в этом устройстве время контроля зависит от количества выхо дов контролируемого блока. Наиболее близким к изобретению техническим решением является устройство для контроля логических схем, содержащее генератор функций Уолша, коммутатор, счетчик тактовых импульсов, алгебраический сумматор, блок установления направления счета и блок индикации, причем выходы генератора функций Уолша соединены с соответствующими входами контролич руемой логической схемы и коммутатора, выход, которого соединен с входом блока установления направления смета, выходы которого соединены с управляющими входами алгебраического сумматора, информационные входы которого соединены с выходами контролируемой логической схемы,выход счетчика тактовых импульсов сое. динен с синхронизирующим входом алгебраического сумматора, выходы кото рого соединены.с входом блока индикации z „ Однако в этом устройстве выходы одной контролируемой схемы связаны с информационными входами алгебраического сумматора, что обуславлива- ет возрастание времени контроля группы логических схем по сравнению с временем контроля одной логической схемы. Цель изобретения - сокращение времени контроля группы однотипных логических блоков. Поставленная цель достигается тем что в устройстве для контроля логи32ческих блоков, содержащее счетчик тактовых импульсов, сумматор-вычитатель, блок индикации, причем выход сумматора-вычитателя соединен с информационным входом блока индикации, введены регистр, сумматор по модулю два, триггер, два элемента И, группа элементов И, группа комбинационных сумматоров, генератор тактовых им-пульсов, причем ыход генератора тактовых импульсов соединен с первым входом первогр элемента И, выход которого соединен с тактовЫм входом сумматора-вычитателя и входом счетчика тактовых импульсов, выходы которого соединень с входами контролируемых логических блоков и входами второго ;элемр.нта И и первыми входами соответствующих элементов И группы, вторые входы которых соединены с соответствующими выходами регистра, выходы элементов И группы соединены с входами сумматоров по модулю два, выход второго элемента И соединен с нулевым входом триггера, единичный вход которого являемся запускащмм входом устройства, нулевой и единичный выходы триггера соединены соответственно с управляющим входом блока индикации и вторым входом первого элемента И, информационные входы сумматора-вычитателя соединены с выходами к-мбинационных сумматоров.группы, входы которых соединены с соответствующимивыходами контролируемых логических блоков, выход сумматора по модулю два соединен с входом суммы (разности)сумматора-вычитателя, На чертеже приведена структурная схема устройства для контроля логических блоков Устройство содержит генератор 1 тактовых импульсов, первый 2 и второй 3элементы И, счетчик k тактовых им-, пульсов, группу комбинационных сумматоров 5, сумматор-вычитатель 6, триггер 7, регистр 8, группу элементов И 9, сумматор 10 по модулю два, блок 11 индикации, запускающий вход 12 устройства, группу контролируемых логических блоков 13. , Выход генератора Т тактовых импульсов соединен с первым входом первого элемента И2, Выход первого элемента И2 соединен с входом счетчика 4тактовых импульсов и тактовым входом -Алгебраического сумматора 6. Вы ходы счетчика 4 тактовых импульсов соединены с входами второго элемент ИЗ, контрол1;1руемых логических блоко ИЗ и первыми входами элементов И9 группы,выходы регистра 8 соединены с вторыми входами соответствующих элементов И9 группы. Выходы элементов И9 группы соедине;ны с входами сумматора 10 по модулю два, выход которого соединен с входом суммы (разности) сумматора вычитателя 6, Выходы сумматора-вычи дателя 6 соединены с информационны входами блока 11 индикации,а входы с выходами комбинационных сумматоров S группы. Количество комбинациоь(ных л сумматоров 5 группы равно количеству выходов контролируемых логических блоков 13, причем к входам первого комбинационного сумматора 5 подключены первые выходы всех контролируемых логических блоков 13, к входам второго комбинационного сумматора 5 подключены все вторые выходы контролируемых логических блоков 13 и т.д..Выход второго элемента ИЗ соединен с нулевым входом триггера 7. Выходы тригг15ра 7 соединены с вто- рым входом первого элемента И2 и управляющим входом блока 11 ин дикации. Единичный выход триггера. 7 ,является запускающим входом 12 уст ройства. Устройство работает следующим образом. После подами питания устройство устанавливается в исходное состоя ние: триггер 7 и счетчик k устанав. ливается в нулевое состояние, в регистр 8 записывается константа в сумматор-вычитатель 6 запксывается эталонное значение результата контроля с противоположным знаком. (Цепи установки устройства в исходное состояние на чертеже не показаны). На вход 12 устройства подается импульс запуска, который устанавли а ет триггер 7 в единичное состояние. При этом единичный сигнал с единичного выхода триггера 7 поступает на второй вход элемента И2 и разре. шает поступление импульсов с выхода генератора 1 на счетный вхрд счетчика i и на тактовый вход суммато- ; ра 6, С выхода счетчика М на входы контролируемых блоков 13 начинают поступать комбинации входных сигналов. Эти же сигналы одновременно поступают на первые входы элементов 134 И9 группы и на входы элемента ИЗ. На вторые входы элементов ИЗ группы поступают сигналы, храняи|иеся в регистре 8, На выходах элементов И9 появляются сигналы, которые поступают на выходы сумматора 10.С выхода сумматора 10 на управляющий вход сумматора-вычитателя 6 поступает сигнал, „ определяющий режим работы сумматора-вычитателя 6 - сложение или вычи- , тание„ Сигналы с выходов контролируемых блоков 13 поступают на входы сумматоров 5 группыо При этом на входы первого суммётюра 5 группы поступают сигналы с первых выходов контролируемых блоков 13 на входы второго сумматора 5 группы поступают сигналы с вторых выходов блоков 13 и т.д. Каждый сумматор 5 группы производит сложение двоичных сигналов. Сигналы с выходов сумматоров 5 группы посту;пают на информационные входы сумматора 6. Сумматор 6 по сигналу, поданному на его управляющий вход с выхода сумматора 10 по модулю два, производит сложение значений сигналов, прдтупивших на его информационные входы с результатом предыдущего действия (если на его управляющий вход подан сигнал или вычитание значений сигналов, поступивших на его информационные входы, из результата предыдущего действия (если на его управляющий вход подан сигнал 1), Синхронизация работы сумматора 6 осуществляется тактовыми импульсами, поступающими на его тактовый вход с выхода элемента И2, « После поступления с в.ыходом счетчика последней комбинации сигналов (lt1ooo,1) на выходе элемента ИЗ появляется единичный сигнал, который устанавливает триггер 7 в нулевое состояние. При этом нулевой сигнал с единичного выхода триггера 7,поступая на второй вход элемента И2, запрещает прохождение тактовых импульсов с выхода генератора 1 на счетный вход счетчика k и тактовый ход сумматора 6„ Одновременно диничный сигнал с нулевого выхода риггера 7 поступает на управляющий вход блока 1 индикации и разреliiaeT отображение результата контроля.

Если все контролируемые блоки 13 работоспособны, то для каждой схемы на блоке 11 индикации отображается нулевое значение сумматора 6.

Если хотя бы один контролируемый блок 13 отказал, то в этом случае на блоке 11 индикации отображается не равное Нулю значение состояния сумма тора 6, соответствующее отказу одного или нескольких контролируемых блоков .3(. Таким образом, все контролируемые

логические блоки 13 проверяются одновременно, при этом время контроля-не зависит от количества контролируемых схем и равно времени контрол:я одной логической схемы.

Применение изобретения позволяет сделать вывод о пригодности к эксплуатации, всей партии логическим блоков, а также сократить время контроля группы Однотипных логических блоков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1984 |

|

SU1185342A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Устройство для контроля родовой деятельности | 1988 |

|

SU1605259A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1234841A1 |

| Устройство для контроля электропотребления | 1988 |

|

SU1566371A1 |

| Сигнатурный анализатор | 1985 |

|

SU1336006A1 |

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее счетчик тактовых импульсов, сумматор-вычитатель, блок индикации, причем выход сумматора-вычитателя соединен с информационным входом блока индикации, отличающееся тем, что, с целью сокращения времени контроля группы однотипных логических ,JB него введены регистр, сумг матор по модулю два,триггер,два эле7«нта И, группа элементов И, группа комбинационных сумматоров, генератор тактовых импульсов, причем выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен с тактовым входом сумматора-вычитателя и входом счетчика тактовых импульсов, вь1ходы которого соединены с входами контролируемых логических блоков и входами .второго элемента И и первыми входами соответствующих элементов И группы, вторые входы которых соединены с соответствующими выходами регистра, выходы элементов И группы соединены со входами сумматора по модулю два, выход второго элемента И соединен с нулевым входом триггера, единичный вход которого является запускающим входом устройства, нулевой i и единичный выходы триггера соединены соответственно с управляющим вхо-. (Л дом блока индикации и вторым входом первого элемента И, информационные входы сумматора-вычитателя соединены с выходами комбинационных сумматоров группы, входы которых соединены с соответствующими выходами контролируемых логических блоков, выход сумматора по модулю два соединен с входом .1 со суммы (разность) сумматора-вычитате:ля. . V DO

Авторы

Даты

1983-10-23—Публикация

1981-12-08—Подача