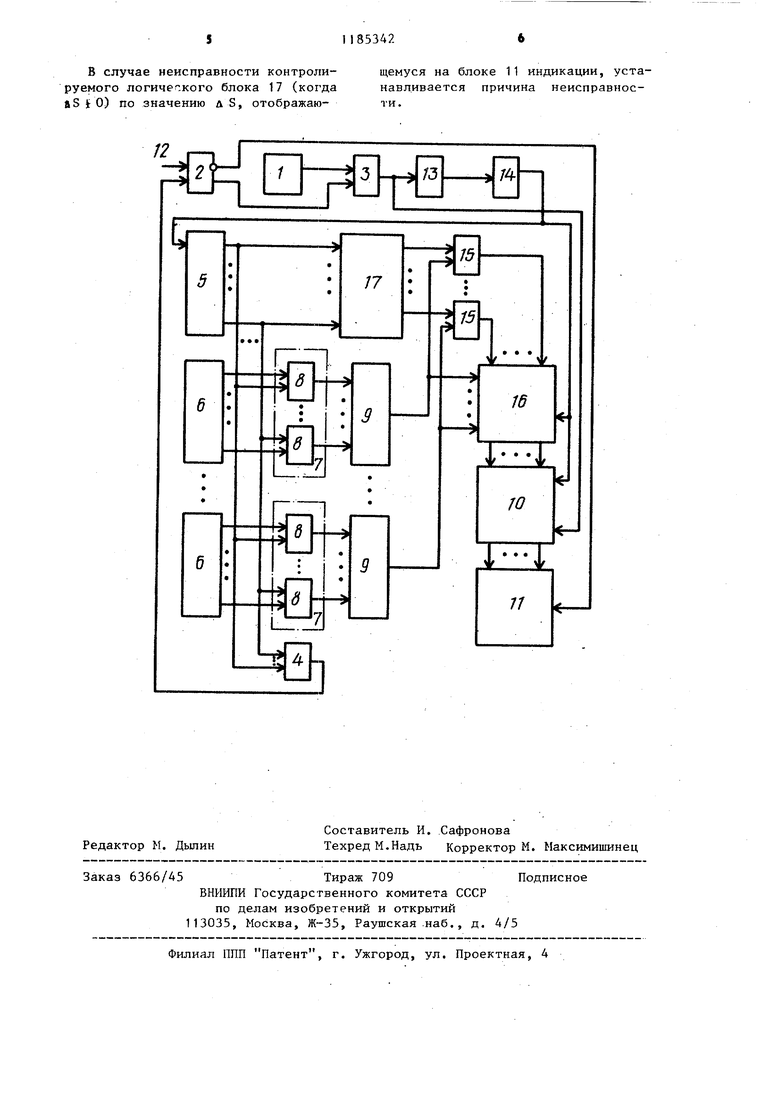

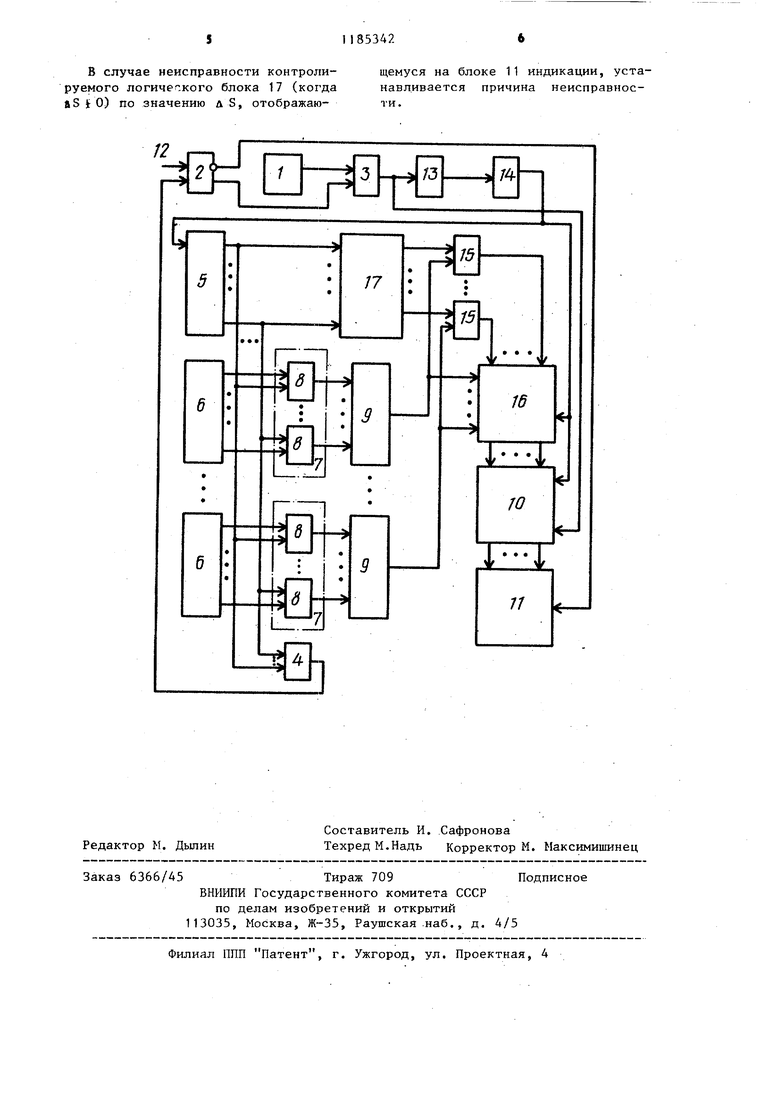

Изобретение относится к вычислительной технике и может быть использовано при контроле работоспособности логических блоков по значениям спектральных коэффициентов Уолша выходных функций. Цель изобретения - расширение фун циональных возможностей устройства з счет обеспечения проверки значений различных спектральных коэффициентов для разных выходов контролируемого логического блока. На чертеже представлена структурная схема устройства. Устройство для контроля логических блоков содержит генератор 1 тактовых импульсов, первый триггер 2, первый 3 и второй 4 элементы И, счет чик 5, группу регистров 6,h гругш 7 элементов И 8, первую группу сумматоров 9 по модулю два, сумматор-вычитаталь 10, блок 11 индикации, вход запуска 12, элемент 13 задержки, вто рой триггер 14, вторую группу сумматоров 15 по модулю два, коммутатор 1 Выходы счетчика 5 соединены с входам контролируемого логического блока 17 выходы которого подключены к вторым входам сумматоров 15 по модулю два второй группы,. Устройство работает следующшч образом. После подачи питания устройство устанавливается в исходное состояние счетчик 5 и триггеры 2 и 14 устанавливаются в нулевое состояние; в реги стры 6 группы записываются в двоичном коде номера cj , aJ,ijJm спектрал ных коэффициентов S (tj,) , S(cJj) ,... S((u)), выбранных в качестве контролируемых параметров для соответствую щих выходов (1,2,...т) контролируемого логического блока 17, tjj ( l u)|) в сумматор-вычитатель 10 записывается число - S - 83 ° -tS J, (u),)-h2S5 (u)) + .. .,(uU где m - количество .выходов контроли М «VV Jiri ic: - 1 J5U СО1ЛиЛ и1Э JXUni UJlW руемого логического блока 17; S,, (оЗ. . 51 эталонное значение спектрального коэ фициента для i, -го выхода блока 1 7. )1((41, &з.(. J--0 . где X j - набор двоичных сигналов (х,, х,,.., Xf,), подаваемых на входы контролируемого логического блока 17J WLJI(X;)- значение функции Уолша; . 1 2 f (xj)- эталонная нулевая функция i-ro выхода контролируемого блока 17. Сигнал О с вьсхода триггера 14 поступает на управляющий вход коммутатора 16 и вход суммы (разности) сумматора-вьгчитателя 10. При этом коммутатор 16 осуществляет подключение выходов сумматора 15 по модулю два к информационным входам сумматора-вычитателя 10, а сумматор-вычитатель 10 настраивается на выполнение опер.ации сложения числа, соответствующего поданным на его информационные входы сигналам, с результатом предыдущего действия. Нулевая комбинация сигналов Хо (О, О, 0,0) с выходов счетчика 5 поступает на входы контролируемого логического блока 17, с выходов которого поступают сигналы, соответствующие значениям выходных булевых функций (х), fi(x,),..., frt,(xo). Комбинация сигналов Хо поступает также через элементы И 8 группы 7 на входы сумматоров 9 по модулю два первой группы. На вьпсодах сз маторов 9 по модулю два образуются сигналы у (х,,), У(.ХО),..., Ут(о), где У; (xj) ®xj( Здесь символ ф означает операцию суммы по модулю два. . Сигналы yj (х) соответствуют значениям функции Уолша: W)-, (xj) yi(Kj) -Ti(xi). Сумматоры 15 по модулю два второй группы производят вычисление логических выражений вида у,- (xj)®fi (xj). Сигналы с выходов сумматоров 15 второй группы поступают на первые входы коммутатора 16, на вторые входы которого поступают сигналы с выходов сумматоров 9 по модулю два первой группы. При этом значения сигналов на вторых входах коммутатора 16 соответствуют В( (x,i) ,X,.-L 2у (xj) +...+2 ), а сигналы на первых его.входах соответствуют числу A(xi) y, (xj)@fL(xj)(xi) ©fi(xj) +.о.(х)(ха) . В данном случае j 0. На вход запуска 12 устройства подается импульс запуска, который устанавливает триггер 2 в единичное состояние. При этом единичньш сигнал с прямого выхода триггера 2 поступает на второй вход элемента И 3 и разрешает поступление импульсов с вы хода генератора 1 на синхронизирующий вход сумматора-вьгчитателя 10 и через элемент 13 задержки на счетный вход триггера 14. После поступления первого тактового импульса с выхода генератора 1 через элемент И 3 на синхронизируюпщ вход сумматора-вьгчитателя 10 последний производит сложение числа А(Хо) У1 (х„)@, (x5)+y(xo)®f2.( + ...+y(Xo)®f(xe), .соответствующего сигналам, поступившим на его информационные входы, с результатом предьщущего действия S. Затем задержанный в элементе 13 задержки S на время, необходимое для выполнения операции сложения (вы читания) сумматором-вычитателем 10, первый импульс генератора 1 поступает на счетный вход триггера 14 и устанавливает его в единичное состоя ние. Сигнал 1, поступая с прямого вы хода триггера 14 на управляющий вход коммутатора 16 и вход суммы (разности) сумматора-вычитателя 10, обес печивает подключение вторых входов коммутатора 16 к информационным входам сумматора-вычитателя 10 и настра ивает сумматор-вычитатель 10 на выполнение операции вычитания числа В(ХО)У (x,)+2y(x) + ... + (xJ соответствующего поступившим на его информационные входы сигналам, из результата предьщущего действия. Когда второй тактовый импульс с выхода генератора 1 поступает на син хронизирующий вход сумматора-вычи- ателя 10, последний производит вычита ние числа B(XO) из результата предыдущего действия Sj + А(хд). При этом получается число (XO)-B(XO)-S, +Lf, (x).o +2f(xe).W(x) + ..,(xo)-W4xJ поскольку Yi (xj )®fi (xj)y (хз) fl(xj).WuJi(xj). После вьшолнения сумматором-вычитателем 10 операции вычитания задержанный элементом 13 задержки второй импульс генератора 1 поступает на счетньш вход триггера 14. Триггер 14 устанавливается в нулевое состояние, что приводит к увеличению числа, записанного в счетчик 5, на единицу (счетчик 5 изменяет свое состояние по заднему фронту импульса, формируемого на прямом выходе триггера 14). Теперь на входы контролируемого логического блока 17 и на первые входы элементов И 8 поступает комбинация сигналов Х,(0,0,..., 0,1), коммму|Татор 16 снова настраивается на подачу сигналов с выходов сумматоров 15 по модулю два на входы сумматора-вычитателя 10, а сумматор-вычитатель подготавливается к вьтолнению операции сложения числа А(х) с результатом предьщущего действия. Таким образом, по нечетному (2;+1)-му тактовому импульсу генератора 1 происходит сложение числа A(xi) с содержимым сумматора-вычитателя 10 (,1,2, ...,), НПО четному (2i+ 2)-мунмпульсу происходит вьгаитание числа В(хО из результата, записанного в сумматорвычитатель 10.. , После поступления последнего 2 -го импульса генератора 1 в суъшатор-вычитатель 10 будет записано AS S-S-p S(u)p+2Si(iJ) + ...+ + (JJ-S, где Si(cJ;) - действительное значение спектрального коэффициента, выбранного в качестве контролируемого параметра для I-го выхода блока 17. Si(Ji)i:f,(xjy.Wu)i(x). Задержанный элементом. 13 задержки этот имрульс установит триггер 14 в нулевое состояние. При этом счетчик 5 переполнится и установится из соотношения (1,1,... 1) в нулевое состояние. Последнее приводит к cfieне сигнала на выходе элемента И 4 с единичного на нулевой, в результате чего триггер 2 устанавливается в нулевое состояние. Сигнал О на его прямом выходе запрещает прохождение импульсов с выхода генератора 1 через элемент И 3. Сигнал 1 на инверсном выходе триггера 2, поступая на управляющий вход блока 1 1 индикации, разрешает отображение результата контроля. Если на блоке индикации отобразится число О, соответствующее совпадению эталонных и действи-г тельных значений спектральных коэффициентов, то контролируемый логический блок 17 признается работоспособным

В случае неисправности контролируемого логического блока 17 (когда ftS t0) по значению д S, отображаю/IJ-TJ

--

tiJn

щемуся на блоке 11 индикации, устанавливается причина неисправное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Устройство для контроля логических блоков | 1981 |

|

SU1049913A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1448346A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1149266A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛО ГИЧЕСКИХ БЛОКОВ, содержащее генератор тактовых импульсов, первый триггер, два элемента И, счетчик, группу из и регистров, и групп элементов И, первую группу сумматоров по модулю два, сумматор-вычитатель, блок индикации, причем выход генератора тактовых импульсов подключен к первому входу первого .элемента И, второй вход которого связан с прямым выходом первого триггера, инверсный выход которого подключен к входу блока индикации, единичный вход первого триггера является входом запуска устройства, нулевой вход первого триггера соединен с выходом второго элемента И, входы которого связаны с первыми входами соответствующих элементов И I -и группы (), вторые входы элементов И L-и группы связаны с соответствующими выходами L-го регистра, выходы элементов И каждой группы подключены к соответствующим входам сумматоров по модулю два первой группы, синхронизирующий вход сумматора-вычитателя связан с выходом первого элемента И, группа выходов сумматора-вычитателя связана с группой входов блока индикации, выходы счетчика подключены к соответствующим входам контролируемого блока и к соответствующим входам элементов И i -и группьт, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения проверки значений различных спектральных коэффициентов для разных выходов контролируемого блока, в него введены элемент заi держки, второй триггер, вторая группа сумматоров по модулю два, комму(Л татор, причем прямой вход второго триггера через элемент задержки подключен к выходу первого элемента И, прямой выход второго триггера соединен с управляющими входами коммутатора, сумматора-вычитателя и счетным входом счетчика, первая и вторая СХ) группы информационных входов коммуСП |Татора связаны соответственно с выоо ходами сумматоров по модулю два пер4 вой и второй групп, группа выходов to коммутатора соединена с группой информационных входов сумматора-вычитателя, первые входы сумматоров по модулю два второй группы соединены с соответствующими выходами контролируемого блока, вторые входы сумматоров по модулю два второй группы связаны с соответствующими выходами сумматоров по модулю два первой rpyn-t пы.

г 4

Щ

-

| Устройство для контроля логическихСХЕМ | 1979 |

|

SU830392A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1981 |

|

SU1049913A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-15—Публикация

1984-04-03—Подача