Изобретение относится к вычислительной технике, в частности к авто- матиэированным системам контроля цифровых устройств, и может быть использовано для контроля цифровых устройств в процессе их производства и эксплуатации.

Целью изобретения является расши рение области применения устройства- и повышение достоверности контроля.

Сущность изобретения состоит в расширении области .применения путем обеспечения возможности получения ди агностической информации за счет записи реакции объекта в ячейки памяти, где хранятся соответствующие тестовые сигналы без увеличения объема блока памяти, а также в повышении до- стоверности контроля путем проверки соответствия реакции объекта контрольному признаку и организации само контроля, что позволяет обнаруживать ошибки нечетной кратности, возникакг щие в результате неисправностей в объекте контроля и в самом устройстве на том шаге контроля, на котором

они появились.

I-

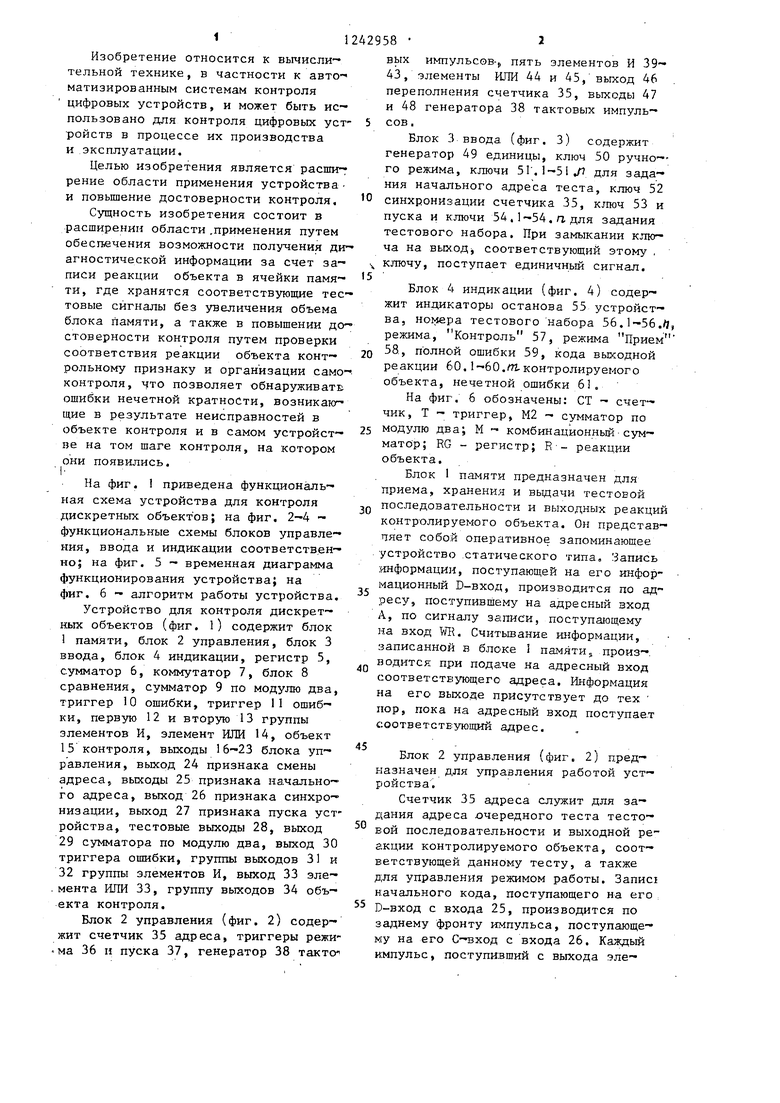

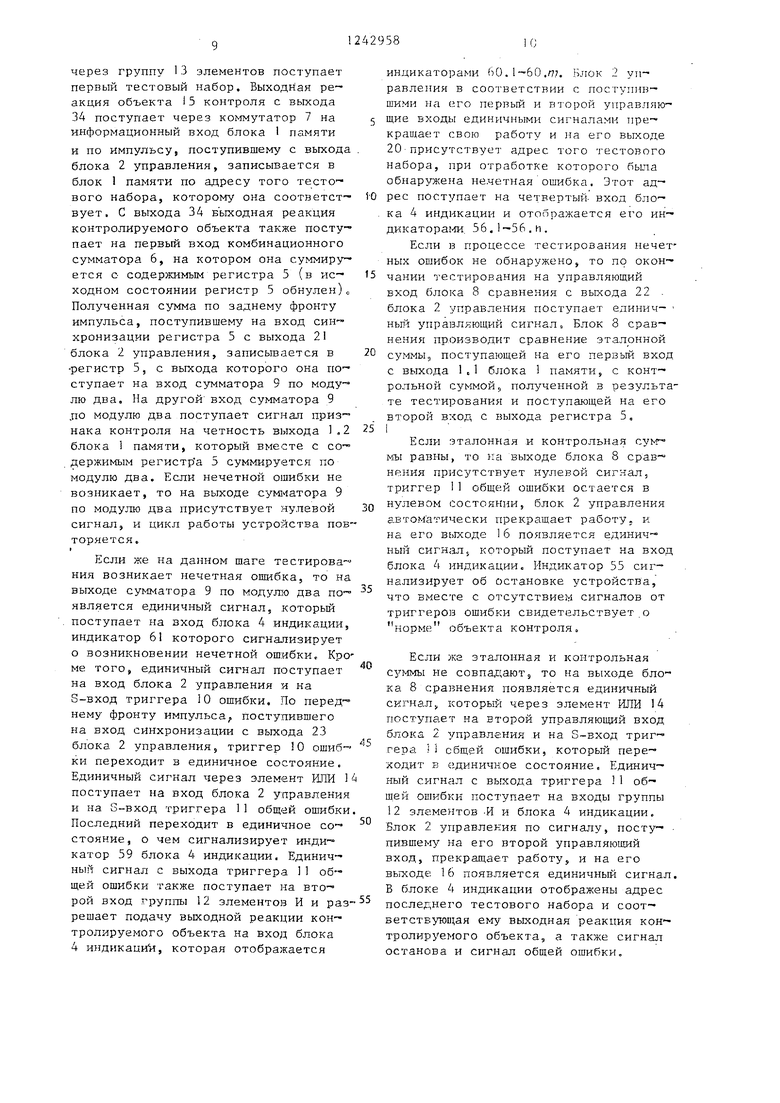

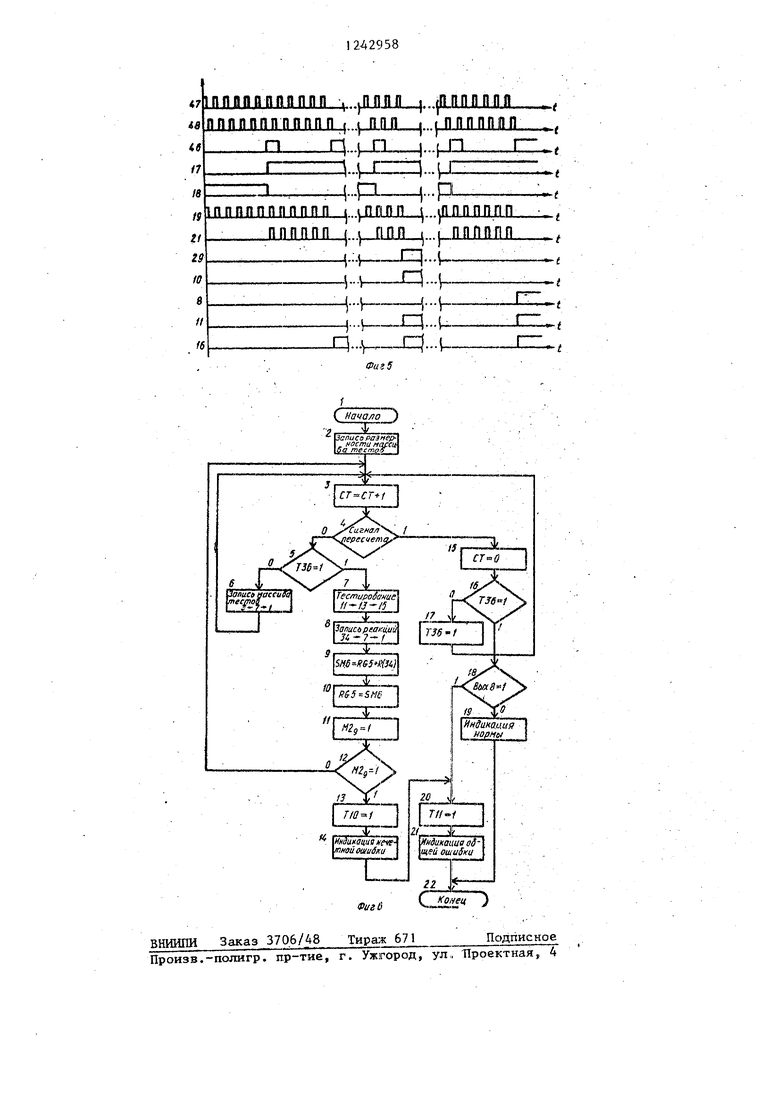

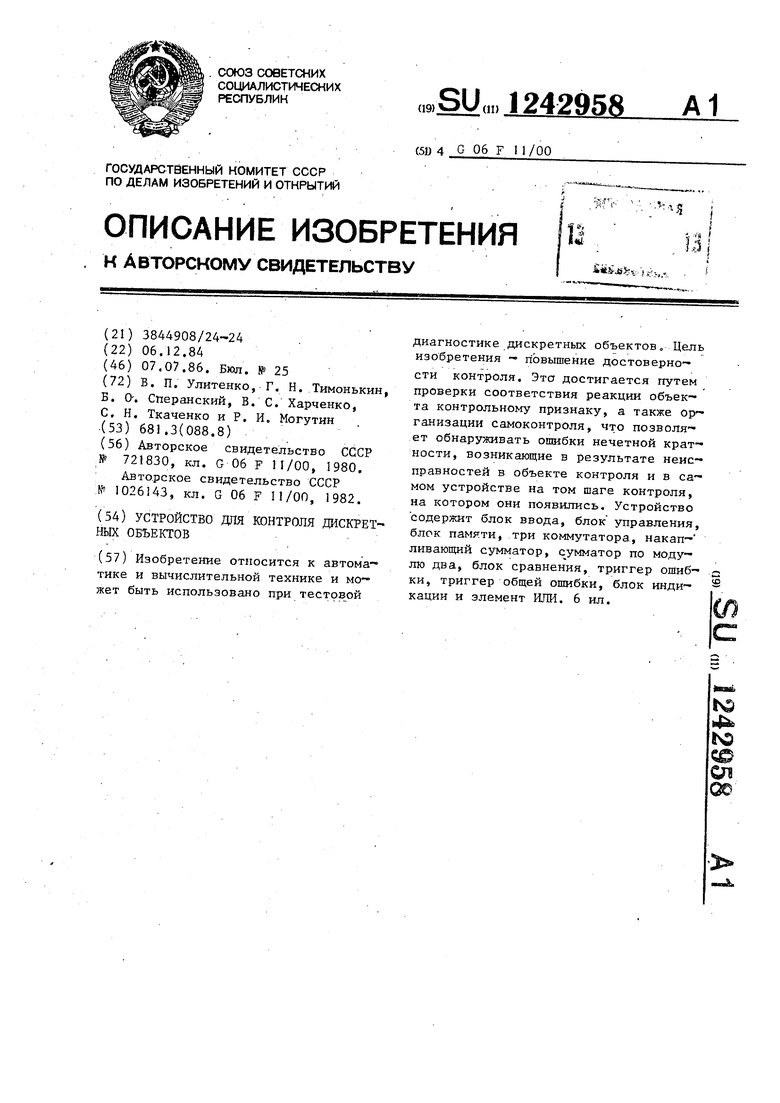

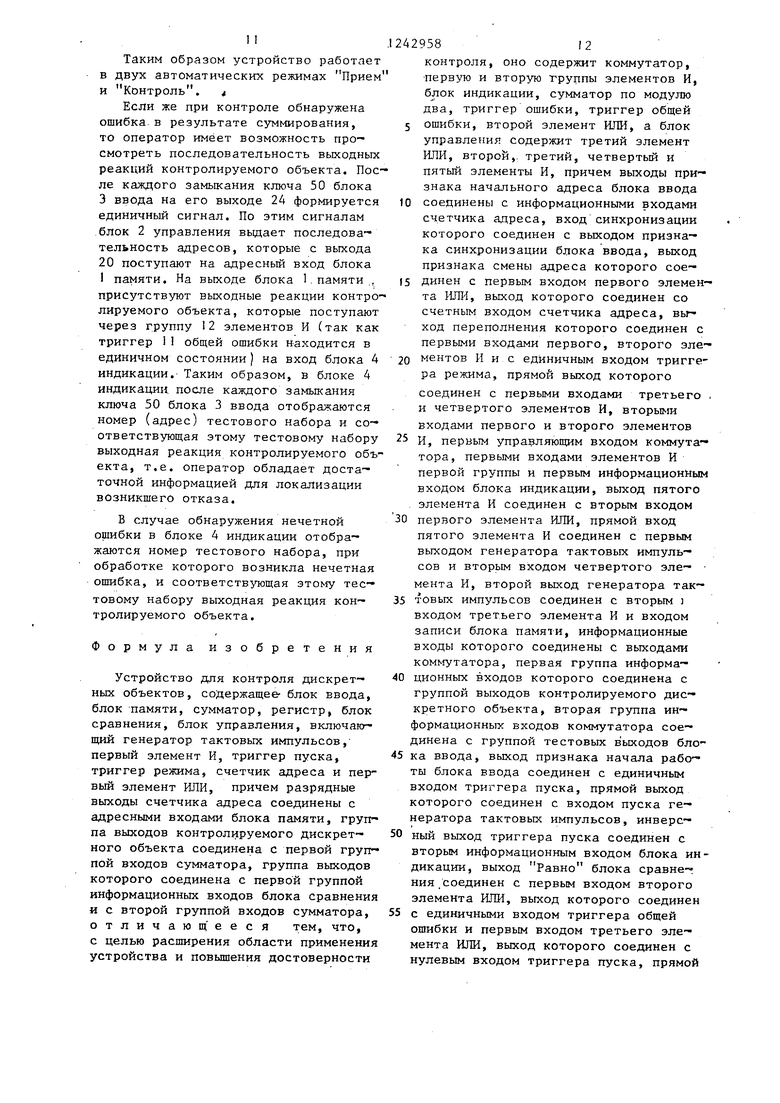

На фиг. i приведена функциональная схема устройства для контроля дискретных объект ов; на фиг. 2-4 - функциональные схемы блоков управления, ввода и индикации соответственно; на фиг. 5 - временная диаграмма функционирования устройства; на фиг. 6 - алгоритм работы устройства. Устройство для контроля дискретных объектов (фиг. 1) содержит блок памяти, блок 2 управления, блок 3 ввода, блок 4 индикации, регистр 5, сумматор 6, коммутатор 7, блок 8 сравнения, сумматор 9 по модулю два, триггер 10 ошибки, триггер 11 ошибки, первую 12 и вторую 13 группы элементов И, элемент ИЛИ 14, объект 15 контроля, выходы 16-23 блока управления, выход 24 признака смены адреса, выходы 25 признака начального адреса, выход 26 признака синхронизации, выход 27 признака пуска устройства, тестовые выходы 28, выход 29 сумматора по модулю два, выход 30 триггера ошибки, группы выходов 31 и 32 группы элементов И, выход 33 эле- мента ИЛИ 33, группу выходов 34 объекта контроля.

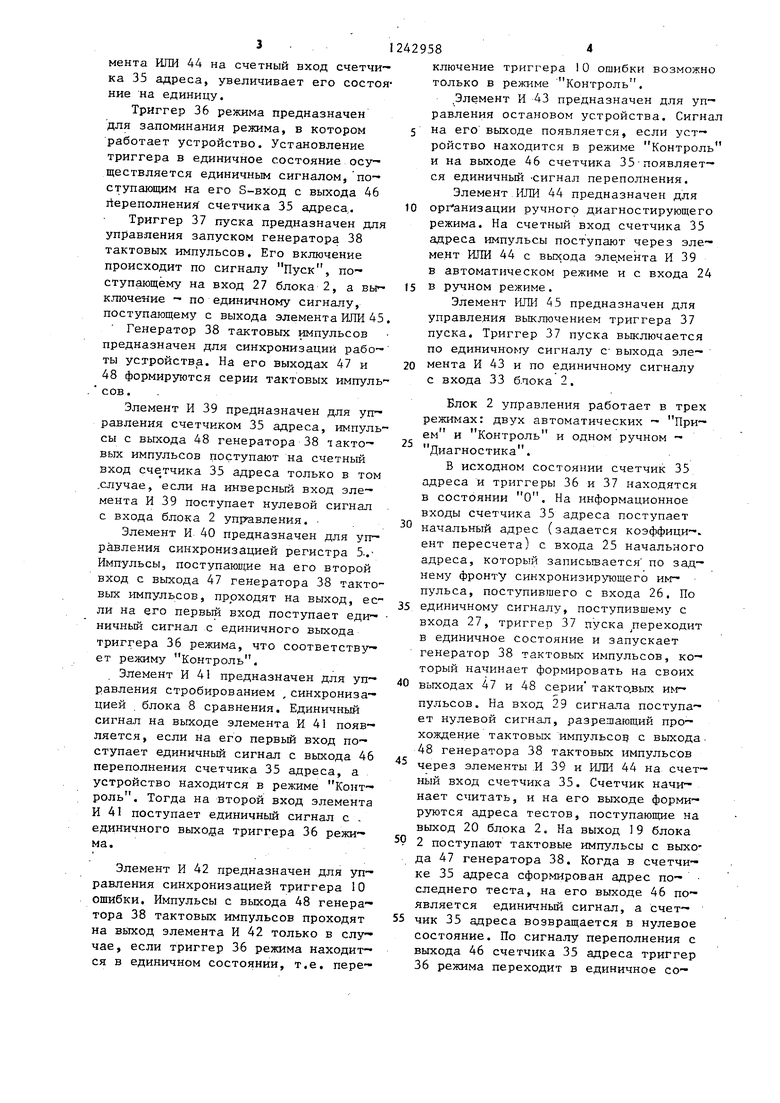

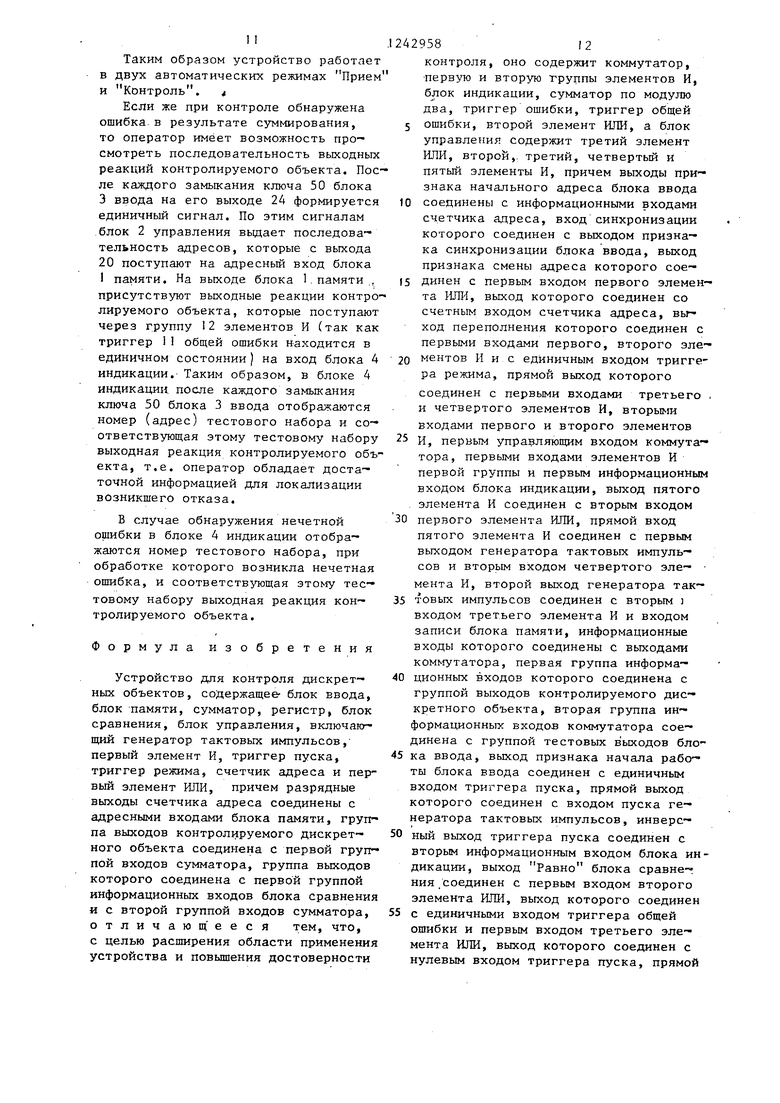

Блок 2 управления (фиг. 2) содержит счетчик 35 адреса, триггеры режи.ма 36 и пуска 37, генератор 38 тактсг

0

5

0

5

0

5

0

5

вых импульсов-,, пять элементов И 39- 43, элементы ИЛИ 44 и 45, выход 46 переполнения счетчика 35, выходы 47 и 48 генератора 38 тактовых импульсов.

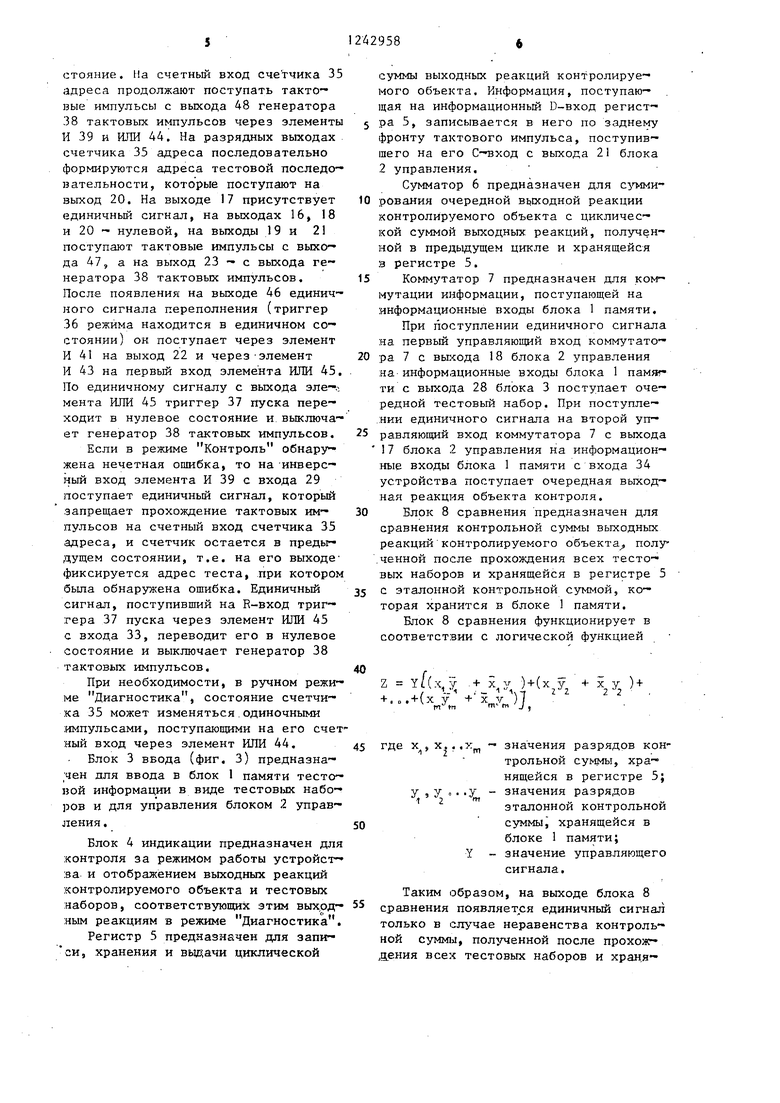

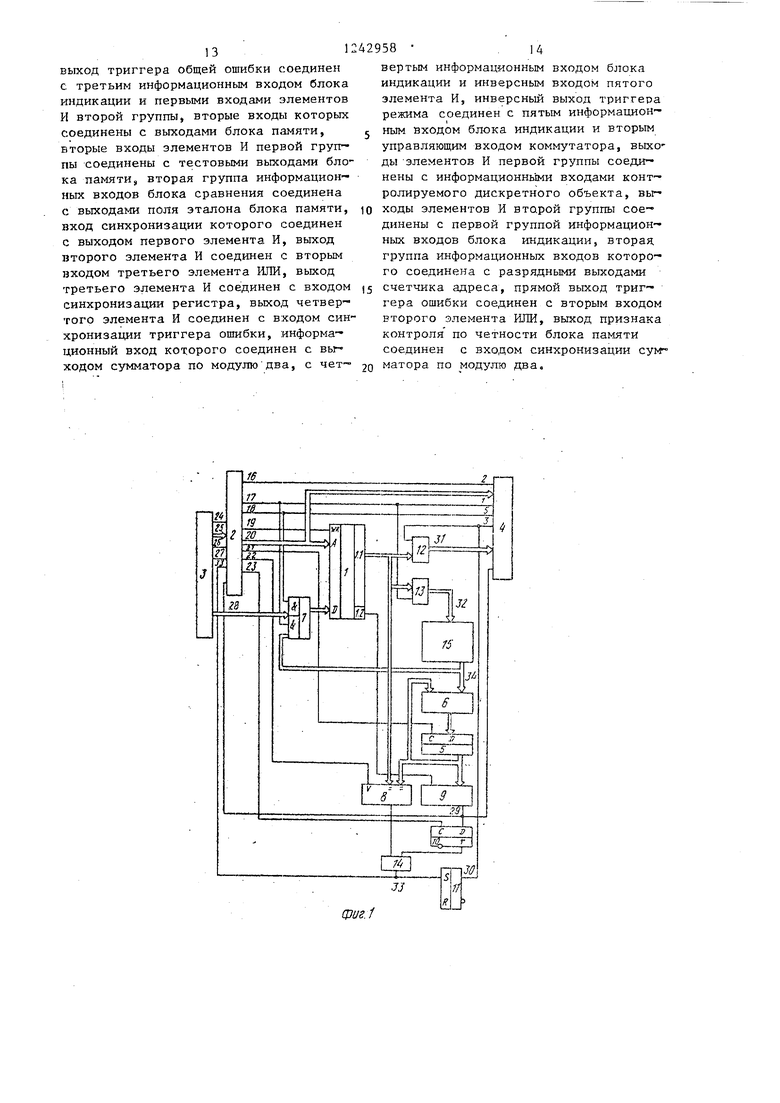

Блок 3 ввода (фиг, 3) содержит генератор 49 единицы, ключ 50 ручно-- го режима, ключи 51, 1-51 ./1 для задания начального адреса теста, ключ 52 синхронизации счетчика 35, ключ 53 и пуска и ключи 54.1-54./г для задания тестового набора. При замыкании ключа на вькод соответствующий этому , ключу, поступает единичный сигнал.

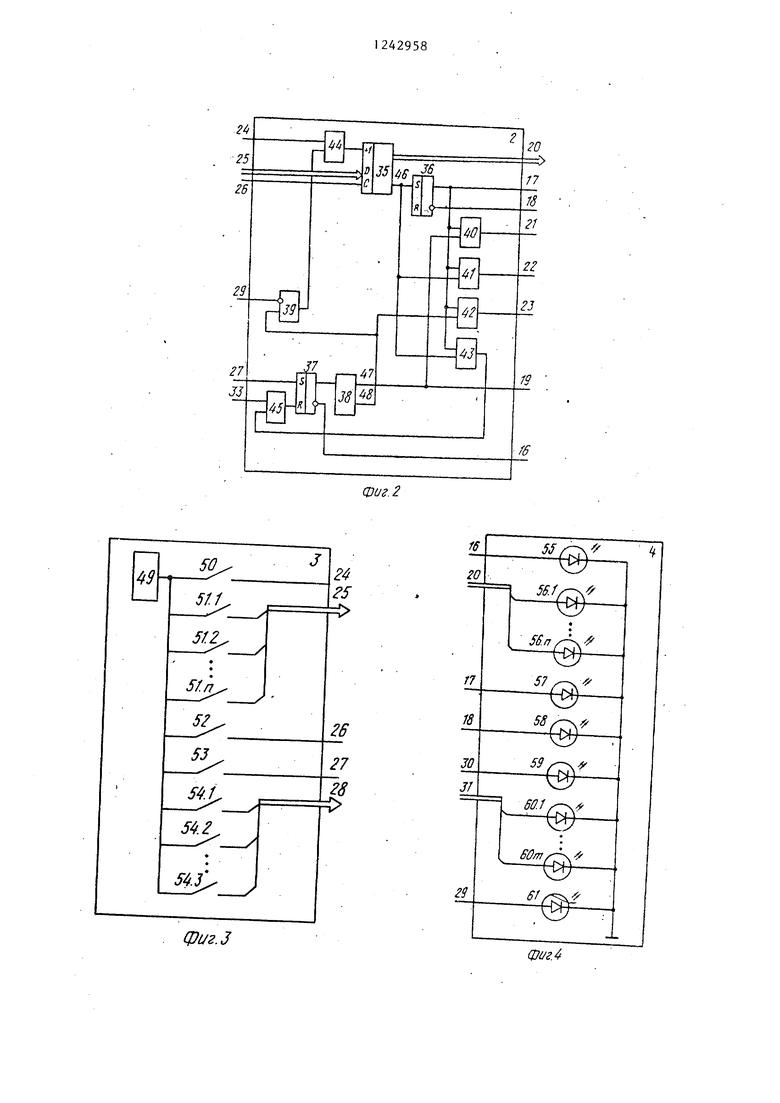

Блок 4 индикации (фиг. 4) содержит индикаторы останова 55 устройства, номера тестового набора 56.1-56., режима, Контроль 57, режима Прием 58, п олной ошибки 59, кода выходной реакции 60,1-60,/71 контролируемого объекта, нечетной ошибки 61.

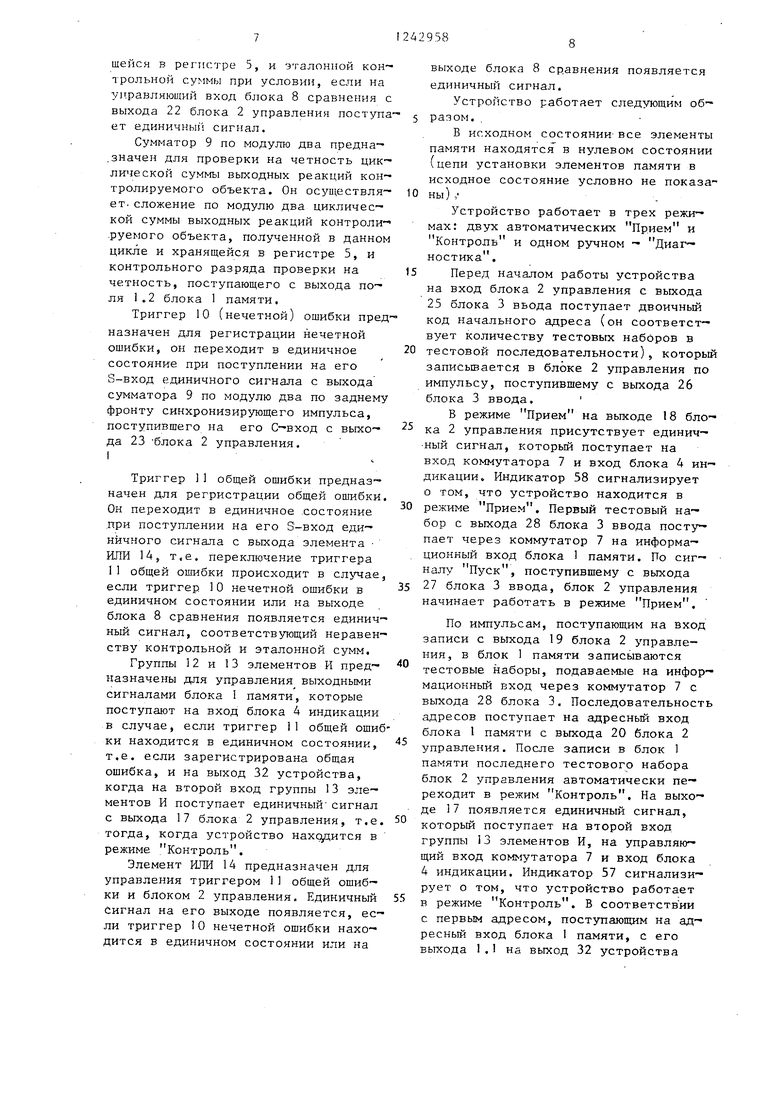

На фиг, 6 обозначены: СТ - счетчик, Т - триггер, М2 - сумматор по модулю два; М - комбинационныйсумматор; RG - регистр; R - реакции объекта.

Блок 1 памяти предназначен для приема, хранения и выдачи тестовой последовательности и выходных реакций контр олируемого объекта. Он представ- пяет собой оперативное запоминающее устройство .статического типа. Запись :информации, поступающей на его информационный D-вход, производится по адресу, поступившему на адресный вход А, по сигналу записи, поступающему на вход WR, Считьшание информации, записанной в блоке 1 памяти, производится: при подаче на адресный вход соответствующего адреса. Информация на его выходе присутствует до тех пор, пока на адресный вход поступает соответстЕ:ующий адрес.

Блок 2 управления (фиг. 2) предназначен для управления работой устройства.

Счетчик 35 адреса служит для задания адреса очередного теста тестовой последовательности и выходной реакции контролируемого объекта, соответствующей данному тесту, а также для управления режимом работы. Запис начального кода, поступающего на его D-вход с входа 25, производится по заднему фронту кмпульса, поступающему на его С-вход с входа 26. Каждый импульс, поступивший с выхода эле3

мента ИЛИ 44 на счетный вход счетчика 35 адреса, увеличивает его состояние на единицу.

Триггер 36 режима предназначен для запоминания режима, в котором работает устройство. Установление триггера в единичное состояние осуществляется единичным сигналом, поступающим на его S-вход с выхода 46 йереполнения счетчика 35 адреса,.

Триггер 37 пуска предназначен для управления запуском генератора 38 тактовых импульсов, Его включение происходит по сигналу Пуск, поступающему на вход 27 блока 2, а выключение - по единичному сигналу, поступающему с выхода элемента ИЛИ 45

Генератор 38 тактовых импульсов предназначен для синхронизации рабо- ты устройства. На его выходах 47 и 48 формируются серии тактовых импульсов . .

Элемент И 39 предназначен для управления счетчиком 35 адреса, импульсы с выхода 48 генератора 38 тактовых импульсов поступают на счетный вход сче тчика 35 адреса только в том .случае, если на инверсный вход элемента И 39 поступает нулевой сигнал с входа блока 2 управления.

Элемент И 40 предназначен для управления синхронизацией регистра 5.. Импульсы, поступаюпдае на его второй вход с выхода 47 генератора 38 тактовых импульсов, проходят на выход, если на его первый вход поступает единичный сигнал с единичного выхода триггера 36 режима, что соответствует режиму Контроль.

Элемент И 41 предназначен для управления стробированием , синхронизацией блока 8 сравнения. Единичный сигнал на выходе элемента И 41 появляется , если на его первьй вход поступает единичный сигнал с выхода 46 переполнения счетчика 35 адреса, а устройство находится в режиме Контроль. Тогда на второй вход элемента И 41 поступает единичный сигнал с . единичного выхода триггера 36 режима.

Элемент И 42 предназначен для управления синхронизацией триггера 10 ошибки. Импульсы с выхода 48 генератора 38 тактовых импульсов проходят на выход элемента И 42 только в случае, если триггер 36 режима находится в единичном состоянии, т.е, пере-

42958

ключение триггера 10 ошибки возможно только в режиме Контроль.

.Элемент И 43 предназначен для управления остановом устройства. Сигнал

5 на его выходе появляется, если устройство находится в режиме Контроль и на выходе 46 счетчика 35-появляется единичный -сигнал переполнения. Элемент.ИЛИ 44 предназначен для

10 орг анизации ручного диагностирующего режима. На счетный вход счетчика 35 адреса импульсы поступают через элемент ИЛИ 44 с выхода эле.мента И 39 в автоматическом режиме и с входа 24

(5 в ручном режиме.

Элемент ИЛИ 45 предназначен для управления выключением триггера 37 пуска. Триггер 37 пуска выключается по eдиничнo ry сигналу с- выхода эле-

20 мента И 43 и по единичному сигналу с входа 33 блока 2.

Блок 2 управления работает в трех режимах: двух автоматических - Прием и Контроль и одном ручном - Диагностика.

В исходном состоянии счетчик 35 адреса и триггеры 36 и 37 находятся в состоянии О. На информационное входы счетчика 35 адреса поступает

30 начальный адрес (задается коэффици-. ент пересчета) с входа 25 начального адреса, который записьтается по нему фронту синхронизирующего импульса, поступившего с входа 26. По

35 единичному сигналу, поступившему с входа 27, триггер 37 пуска переходит в единичное состояние и запускает генератор 38 тактовых импульсов, который начинает формировать на своих

40 выходах 47 и 48 серии такто,вьгх импульсов. На вход 29 сигнала поступает нулевой сигнал, разрешающий прохождение тактовых импульсов с выхода. 48 генератора 38 тактовых импульсов

через элементы .И 39 и ИЛИ 44 на счетный вход счетчика 35. Счетчик начинает считать, и на его выходе формируются адреса тестов, поступающие на выход 20 блока 2. На выход 19 блока

59 2 поступают тактовые импульсы с выхо да 47 генератора 38. Когда в счетчике 35 адреса сформирован адрес по- следнего теста, на его выходе 46 появляется единичный сигнал, а счет-

55 чик 35 адреса возвращается в нулевое состояние. По сигналу переполнения с выхода 46 счетчика 35 адреса триггер 36 режима переходит в единичное со-

стояние. На счетный вход счетчика 35 адреса продолжают поступать тактовые импульсы с выхода 48 генератора 38 тактовых импульсов через элементы И 39 и ИЛИ 44. На разрядных выходах счетчика 35 адреса последовательно формируются адреса тестовой последовательности, которые поступают на выход 20. На выходе 17 присутствует единичный сигнал, на выходах 16, 18 и 20 - нулевой, на выходы 19 и 21 поступают тактовые импульсы с выхода 47, а на выход 23 - с выхода ге нератора 38 тактовых импульсов. После появления на выходе 46 единичного сигнала переполнения (триггер 36 режима находится в единичном состоянии) он поступает через элемент И 41 на выход 22 и через-элемент И 43 на первый вход элемента ИЛИ 45. По единичному сигналу с выхода эле-о. мента ИЛИ 45 триггер 37 пуска переходит в нулевое состояние и выключает генератор 38 тактовых импульсов.

Если в режиме Контроль обнаружена нечетная ошибка, то на -инверсный вход элемента И 39 с входа 29 поступает единичный сигнал, который запрещает прохождение тактовых импульсов на счетный вход счетчика 35 адреса, и счетчик остается в преды- рдущем состоянии, т.е. на его выходе- фиксируется адрес теста, при котором бьша обнаружена ошибка. Единичный сигнал, поступивший на R-вход триггера 37 пуска через элемент :ШШ 45 с входа 33, переводит его в нулевое состояние и выключает генератор 38 тактовых импульсов.

При необходимости, в ручном режиме Диагностика, состояние счетчи- jca 35 может изменяться . одиночными :импульсами, поступающими на его счет ный вход через элемент ИЛИ 44.

Блок 3 ввода (фиг. 3) предназначен для ввода в блок 1 памяти тестовой информации в виде тестовых наборов и для управления блоком 2 управления .

Блок 4 индикации предназначен для контроля за режимом работы устройства и отображением выходных реакций контролируемого объекта и тестовых наборов, соответствующих этим выхрд- ным реакциям в режиме Диагностика.

Регистр 5 предназначен для запи- си, хранения и вьщачи циклической

суммы выходных реакций контролируемого объекта. Информация, поступающая на информационный D-вход регист- ра 5, записывается в него по заднему фронту тактового импульса, поступившего на его С-вход с выхода 21 блока 2 управления.

С-умматор 6 предназначен для С1 1мирования очередной В1 1ходной реакции контролируемого объекта с циклической сумной выходных реакций, полученной в предыдущем цикле и хранящейся в регистре 5.

Коммутатор 7 предназначен для коммутации информации, поступающей на информационные входы блока 1 памяти.

При поступлении единичного сигнала на первый управляющий вход коммутатора 7 с выхода 18 блока 2 управления на. информационные входы блока 1 памят ти с выхода 28 блока 3 поступает очередной тестовый набор. При поступлении единичного сигнала на второй уп-

равляющий вход коммутатора 7 с выхода 17 блока 2 управления на информацион- :ные входы блока 1 памяти с входа 34 устройства поступает очередная выходная реакция объекта контроля.

Блок 8 сравнения предназначен для сравнения контрольной суммы выходных реакций контролируемого объекта полу .ченной после прохождения всех тестовых наборов и хранящейся в регистре 5 с эталонной контрольной суммой, которая хранится в блоке 1 памяти.

Блок 8 сравнения функционирует в соответствии с логической функцией

40

Z Y(X,: .4- )( ) + + , о. + (х у н- х„у )

i J,

где х, х..:„ У,, .

значения разрядов контрольной су№1ы, хранящейся в регистре 5; значения разрядов эталонной контрольной суммыi хранящейся в блоке 1 памяти; значение управляющего сигнала.

Таким образом, на вьпсоде блока 8 сравнения появляет.ся единичный сигнал только в случае неравенства контрольной суммы, пол гченной после прохояг Аения всех тестовых наборов и хран.я-

Y

шейся в регистре 5, и эталонной контрольной суммы при условии, если на у травляюи1ий вход блока 8 сравнения с выхода 22 блока 2 управления поступает единичный сигнал.

Сумматор 9 по модулю два предна- .значен для проверки на четность циклической суммы выходных реакций контролируемого объекта. Он осуществляет, сложение по модулю два циклической суммы выходных реакций контроли- .руемого объекта, полученной в данном цикле и хранящейся в регистре 5, и контрольного разряда проверки на четность, поступающего с выхода поля 1.2 блока 1 памяти.

Триггер 10 (нечетной) ошибки пред назначен для регистрации нечетной ошибки, он переходит в единичное состояние при поступлении на его S-вход единичного сигнала с выхода сумматора 9 по модулю два по заднему фронту синхронизирующего импульса, поступившего на его С-вход с выхода 23 -блока 2 управления. I

Триггер 11 общей ошибки предназначен для регристрации общей ошибки. Он переходит в единичное .состояние .при поступлении на его единичного сигнала с выхода элемента ИЛИ 1А, т.е. переключение триггера II общей ошибки происходит в , если триггер 10 нечетной ошибки в единичном состоянии или на выходе блока 8 сравнения появляется единичный сигнал, соответствующий неравенству контрольной и эталонной сумм.

Группы 12 и 13 элементов И предназначены для управления выходными сигналами блока 1 памяти, которые поступают на вход блока 4 индикации в случае, если триггер 11 общей ошибки находится в единичном состоянии, т.е. если зарегистрирована общая ошибка, и на выход 32 устройства, когда на второй вход группы 13 элементов И поступает единичный сигнал с выхода 17 блока 2 управления, т.е тогда, когда устройство нахо/ ится в режиме Контроль.

Элемент ИЛИ 14 предназначен для управления триггером 11 общей ошибки и блоком 2 управления. Единичньй сигнал на его выходе появляется, если триггер 10 нечетной ошибки находится в единичном состоянии или на

выходе блока 8 сравнения появляется единичный сигнал.

Устройство работает следующим об- 5 разом.

В исходном состоянии- все элементы памяти находятся в нулевом состоянии (цепи установки элементов памяти в исходное состояние условно не показа0 ны) ,

Устройство работает в трех режимах: двух автоматических Прием и Контроль и одном ручном - Диагностика .

5 Перед началом работы устройства на вход блока 2 управления с выхода 25 блока 3 ввода поступает двоичный код начального адреса (он соответствует количеству тестовых наборов в

0 тестовой последовательности), который записьшается в блоке 2 управления по импульсу, поступившему с выхода 26 блока 3 ввода.

В режиме Прием на выходе 18 бло-

5 ка 2 управления присутствует единич- ный сигнал, который поступает на вход коммутатора 7 и вход блока 4 индикации. Индикатор 58 сигнализирует о том, что устройство находится в

0 режиме Прием. Первый тестовый набор с выхода 28 блока 3 ввода поступает через коммутатор 7 на информационный вход блока 1 памяти. По сигналу Пуск, поступившему с выхода

5 27 блока 3 ввода, блок 2 управления начинает работать в режиме Прием.

По импульсам, поступающим на вход записи с выхода 19 блока 2 управления, в блок 1 памяти записываются тестовые наборы, подаваемые на информационный вход через коммутатор 7 с выхода 28 блока 3. Последовательность адресов поступает на адресный вход блока 1 памяти с выхода 20 блока 2

управления. После записи в блок 1 памяти последнего тестового набора блок 2 управления автоматически переходит в режим Контроль. На выходе 17 появляется единичный сигнал, который поступает на второй вход группы 13 элементов И, на управляющий вход коммутатора 7 и вход блока 4 индикации. Индикатор 57 сигнализирует о том, что устройство работает

- в режиме Контроль. В соответствии с первым адресом, поступающим на адресный вход блока 1 памяти, с его выхода 1.1 на выход 32 устройства

0

0

через группу 13 элементов поступает первый тестовый набор. Выходная реакция объекта 15 контроля с выхода 34 поступает через коммутатор 7 на информационный вход блока 1 памяти и по импульсу, поступившему с выхода блока 2 управления, записывается в блок 1 памяти по адресу того тесто вого набора, которому она соответст- вует. С выхода 34 в ыходная реакция контролируемого объекта также поступает на первый вход комбинационного сумматора 6, на котором она суммиру- ется с содержимым регистра 5 (в ис- ходном состоянии регистр 5 обнулен)с Полученная сумма по заднему фронту импульса, поступившему на вход синхронизации регистра 5 с выхода 2 блока 2 управления, записывается в регистр 5, с выхода которого она поступает на вход сумматора 9 по модулю два. На другой вход сумматора 9 J1O модулю два поступает сигнал признака контроля на четность выхода 1,2 блока 1 памяти, которьм вместе с содержимым регистр а 5 суммируется по модулю два. Если нечетной ошибки не возникает, то на выходе сум1 атора 9 по модулю два присутствует нулевой сигнал, и цикл работы устройства повторяется.

Если же на данном шаге тестирова- ния возникает нечетная опшбка, то на выходе сумматора 9 по модултю два по- является единичный сигнал, которьш поступает на вход блока 4 индикации, индикатор 61 которого сигнализирует о возникновении нечетной ошибки, Кро ме того, единичный сигнал поступает на вход блока 2 управления и на S-вход триггера Ю ошибки. По переднему фронту импульса, поступившего на вход синхронизации с выхода 23 блока 2 управления, триггер 0 ошиб- ки переходит в единичное состояние. Единичный сигнал через элемент ИЛИ 1 поступает на вход блока 2 управления и на S-вход триггера 11 общей ошибки Последний переходит в единичное со- стояние, о чем сигнализирует индикатор 59 блока 4 индикации. Единичный сигнал с выхода триггера 11 общей ошибки также поступает на второй вход группы 12 элементов И и раз решает подачу выходной реакции контролируемого объекта на вход блока 4 индикаций, которая отображается

индикаторами hO. 1-60./77. Блок 2 управления в соответствии с поступившими на его первый и второй управляющие входы единичными сигналами прекращает свою работу и на его выходе 20 присутствует адрес того тестового набора, при отработке которого бьша обнар окена не.четная ошибка. Этот адрес поступает на четвертый- вход блока 4 индикации и отображается его ин- дикатора1-1и. 56.1-56. и.

Если в процессе тестирования нечетных ошибок не обнаружено, то по окончании тестирования на управляющий вход блока 8 сравнения с выхода 22 - блока 2 управления поступает единиц- ньй управляющий сигнал. Блок 8 сравнения производит сравнение эталонной суммы, поступающей на его первый вход с выхода 1,1 блока 1 памяти, с контрольной суммой,, полученной в результте тестирования и поступающей на его второй вход с выхода регистра 5, i

Если эталонная и контрольная суммы равны, то ка выходе блока В сравнения присутствует нулевой сигнал, триггер 11 общей ошибки остается в нулевом состоянии, блок 2 управления автоматически прекращает работу, и на его выходе 16 появляется единичный сигнгал, который поступает на вход блока 4 индикации. Индикатор 55 сигнализирует об остановке устройства, что вместе с отсутствием сигналов от триггеров ошибки свидетельствует о норме объекта контроля.

Если жг этахгонная и контрольная суммы не совпадают, то на выходе блока В сравнения появляется единичный сигналS который через элемент ИЛИ 14 поступает на второй управляющий вход блока 2 управления и на триггера J 1 общей ошибки, который переходит в единичное состояние. Единичный сигнал с выхода триггера 11 обшей ошибки поступает на входы группы 12 элементов -И и блока 4 индикации. Блок 2 управления по сигналу, посту- пившему на его второй управляющий вход, прекращает работу, и на его выходе 16 появляется единичный сигнал В блоке 4 индикации отображены адрес последнего тестового набора и соот- ветствутош;ая ему выходная реакция контролируемого объекта, а также сигнал останова и сигнал общей ошибки.

Таким образом устройство работает в двух автоматических режимах Прием и Контроль. 4

Если же при контроле обнаружена ошибка, в результате суммирования, то оператор имеет возможность просмотреть последовательность выходных реакций контролируемого объекта. После каждого замьшания ключа 50 блока 3 ввода На его выходе 24 формируется единичный сигнал. По этим сигналам блок 2 управления выдает последовательность адресов, которые с выхода 20 поступают на адресный вход блока 1 памяти. На выходе блока 1. памяти ., присутствуют выходные реакции контролируемого объекта, которые поступают через группу 12 элементов И (так как триггер 11 общей ошибки находится в единичном состоянии) на вход блока А индикации. Таким образом, в блоке 4 индикации, после каждого замьжания ключа 50 блока 3 ввода отображаются номер (адрес) тестового набора и соответствующая этому тестовому набору выходная реакция контролируемого объекта, т.е. оператор обладает достаточной информацией для локализации возникшего отказа.

В случае обнаружения нечетной ошибки в блоке 4 индикации отображаются номер тестового набора, при обработке которого возникла нечетная ошибка, и соответствующая этому тестовому набору выходная реакция контролируемого объекта.

Формула изобретения

Устройство для контроля дискретных объектов, содержащее блок ввода, блок памяти, сумматор, регистр, блок сравнения, блок управления, включаю щий генератор тактовьгх импульсов, первый элемент И, триггер пуска, триггер режима, счетчик адреса и первый элемент ИЛИ, причем разрядные выходы счетчика адреса соединены с адресными входами блока памяти, группа выходов контролируемого дискретного объекта соединена с первой груп пой входов сумматора, группа выходов которого соединена с первой группой информационных входов блока сравнения и с второй группой входов сумматора, отличаю щ ееся тем, что, с целью распшрения области применения устройства и повышения достоверности

4295812

контроля, оно содержит коммутатор, первую и вторую группы элементов И, блок индикации, сумматор по модулю два, триггер ошибки, триггер общей 5 ошибки, второй элемент Ш1И, а блок управления содержит третий элемент ИЛИ, второй,, третий, четвертый и пятый элементы И, причем выходы признака начального адреса блока ввода 0 соединены с информационными входами счетчика адреса, вход синхронизации которого соединен с выходом признака синхронизации блока ввода, выход признака смены адреса которого сое- 15 динен с первым входом первого элемента ИЛИ, выход которого соединен со счетным входом счетчика адреса, выход переполнения которого соединен с первыми входами первого, второго эле- 0 ментов И и с единичным входом триггера режима, прямой выход которого соединен с первыми входами третьего , и четвертого элементов И, вторыми входами первого и второго элементов 5 и, первым управляющим входом коммута- тора, первыми входами элементов И первой группы и первым информационным входом блока индикации, выход пятого элемента И соединен с вторым входом 0 первого элемента ИЛИ, прямой вход пятого элемента И соединен с первым выходом генератора тактовых импульсов и вторым входом четвертого эле- мента И, второй выход генератора так- 5 товых импульсов соединен с вторым i входом третьего элемента И и входом записи блока памяти, информационные входы которого соединены с выходами коммутатора, первая группа информа- 0 ционных входов которого соединена с группой выходов контролируемого дискретного объекта, вторая группа информационных входов коммутатора соединена с группой тестовых в ыходов бло- 5 ка ввода, выход признака начала работы блока ввода соединен с единичным входом триггера пуска, прямой выход которого соединен с входом пуска генератора тактовых импульсов, инверс- 0 ный выход триггера пуска соединен с вторым информационным входом блока индикации, выход Равно блока сравне- кия соединен с первым входом второго элемента ИЛИ, выход которого соединен 5 с единичными входом триггера общей ошибки и первым входом третьего элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска, прямой

13iвыход триггера общей ошибки соединен с. третьим информационным входом блока индикации и первыми входами элементов И второй группы, вторые входы которых соединены с выходами блока памяти, вторые входы элементов И первой группы соединены с тестовыми выходами блока памяти, вторая группа информационных входов блока сравнения соединена с вькодами поля эталона блока памяти, вход синхронизации которого соединен с выходом первого элемента И, выход второго элемента И соединен с вторым входом третьего элемента ИЛИ, выход третьего элемента И соединен с входом синхронизации регистра, выход четвертого элемента И соединен с входом синхронизации триггера ошибки, информационный вход которого соединен с выходом сумматора по модулю два, с чет58 .14

вегртым информационным входом блока индикации и инверсным входом пятого элемента И, инверсный выход триггера режима соединен с пятым информационным входом блока индикации и вторым управляющим входом коммутатора, выходы -элементов И первой группы соединены с информационнь гми входами контролируемого дискретного объекта, вьг

ходы элементов И второй группы соединены с первой группой информационных входов блока индикации, вторая группа информационных входов которого соединена с разрядными выходами

счетчика адреса, прямой выход триггера ошибки соединен с вторым входом второго элемента ИЛИ, выход признака контроля по четности блока памяти соединен с входом синхронизации cyif

матора по модулю два.

2 It

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для тестового диагностирования | 1984 |

|

SU1213481A1 |

| Устройство для тестового диагностирования | 1982 |

|

SU1045230A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Система для контроля и испытаний блоков памяти бортовых ЭВМ | 1984 |

|

SU1182526A1 |

| Устройство для управления с контролем | 1983 |

|

SU1156074A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Измерительное устройство с самоконтролем | 1984 |

|

SU1226417A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

Изобретение относится к автома тике и вычислительной технике и может быть использовано при тестовой диагностике дискретных объектов. Цель изобретения - повышение достоверности контроля. Это достигается путем проверки соответствия реакции объекта контрольному признаку, а также организации самоконтроля, что позволяет обнаруживать ошибки нечетной кратности, возникающие в результате неисправностей в объекте контроля и в самом устройстве на том шаге контроля, на котором они появились. Устройство содержит блок ввода, блок управления, блок памяти, три коммутатора, накап- ливающий сумматор, сумматор по модулю два, блок сравнения, тр|Иггер ошибки, триггер общей ошибки, блок инди- кации и элемент ИЛИ. 6 ил. ю 4 чЭ

фиг.З

Начало )

| Время-импульсное делительное устройство | 1977 |

|

SU721830A1 |

| Устройство для контроля дискретных объектов | 1982 |

|

SU1026143A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-12-16—Подача