второго элемента И, выход первого триггера подключен к первому входу пятого элемента И, второй вход которого подключен к выходу блока ввода информации, выход первого элемента И подключен к входу установки О второто триггера, выход второго элемента И подключен к второму входу блока ввода информации, выход второго триггерй. подключен к четвертым входам третьего и четвертого элементов И, выходы третьего и четвертого элементов И подключены к управляющим входам регистра, выход пятого элемента И подключен к третьему входу установ-ки 1 второго тригге15а и к другому информационному входу преобразователя

108

кодов, информационные выходы которого подключены к входам шестого дешифратора, регистра и одним из информационных входов второго дешифратора, дру-гие информационные входы которого подключены к выходам регистра, первый выход шестого дешифратора подключен к пятым входам третьего и четвертого элементов И и к первому управляющему входу второго коммутатора, второй управляющий вход которого подключен к одному, из выходов шестого дешифратора, выходы второго коммутатора подключены к входам пятого дешифратора, контрольный выход преобразователя кодов подключен к четвертому входу установки 1 второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода графичес-КОй иНфОРМАции | 1979 |

|

SU798916A1 |

| Устройство для управления вводом информации | 1988 |

|

SU1566337A1 |

| Устройство для ввода информации | 1985 |

|

SU1312557A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1092562A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1049966A1 |

| Устройство для синхронизации координатных пультов ввода информации | 1982 |

|

SU1045238A1 |

УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В ОПЕРАТИВНУЮ ПАМЯТЬ, содержащее генератор импульсов, счетчик, первый триггер, дешифраторы с первого по пятый; первый элемент И, блок ввода информации, преобразователь кодов, первый коммутатор, причем первый выход генератора импульсов подключен к счетному входу счетчика, второй вькод - к управляющему входу первого дешифратора, выходы счетчика подключены соответственно к входам первого и второго дешифраторов, к одним из информационных входов преобразователя кодов, к входам третьего и четвертого дешифраторов, первые выходы первого и второго дешифраторов подключены к первому и второму входам первого элемента И, выходы с пятого по восьмой второго дешифратора подключены к управляющим входам с первого по четвертый преобразователь кодов, первый выход третьего дешифратора подключен к третьему входу первого элемента И и пятому управляющему входу преобразователя кодов, второй и третий выходы третьего дешифратора подклю 4ены соответственно к шестому и седьмому управляющим входам преобразователя кодов, первый выход четвертого дешифратора подключен к управляющему входу третьего дешифратора, выход первого элемента И подключен к входу установкиопреобразователя кодов, выходы пятого дешифратора подключены к управляющим входам первого коммутатора, входы которого являются информационными входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй триггер, элементы И с второго по пятый, шестой дешифратор, регистр и второй коммутатор, причем второй i выход первого дешифратора подключен к .первому входу второго элемента И, чет(Л вертый выход первого дешифратора подключен к входу установки 1 первого с триггера, первому входу третьего элемента И, первому входу блока ввода информации, шестой выход первого де; шифратора, подключен к входу установки О первого триггера и первому входу четвертого элемента И, второй выход второго дешифратора подключен к первому входу установки 1 второго триггера, четвертый выход второго дешифратора подключен к вторым входам третьего и четвертого элементов И, четвертый выход третьего дешифратора подключен к второму входу установки 1 второго триггера и третьим входам третьего и четвертого эле ментов И, первый выход четвертого дешифратора подключен к второму входу

1

Изобретение относится к вычислителной технике и может быть- использовано для записи информации в оперативную память.

Известны устройства для записи информации в оперативную память J

Одно из известных устройств содержит генератор, счетчик, дешифраторы, блок ввода, преобразователь кода Щ .

Однако это устройство имеет малое быстродействие.

Наиболее близким техническим решением к предлагаемому является устройство для записи информации в оперативную память, содержащее генератор импульсов, счетчик, первый триггер, дешифраторы с первого по пятьш, первый элемент И, блок ввода информации, npe образователь кодов, первый коммутатор, причем первый выход генератора импульсов- подключен к счетному йходу счетчика, второй выход генератора импульсов подключен к управляющему входу первого дешифратора, первые выходы счетчика подключены к входам первого дешифратора, вторые выходы счетчик подключены к входам второго дешифратора и к входам ввода параллельного кода преобразователя кодов, третьи и четвертые выходы счетчика подключены к входам третьего и четвертого дешифраторов соответственно, первые вькоды

первого и второго дешифраторов подключены к первому и второму входу первого элемента И, выходы с пятого по восьмой второго дешифратора подключены к управляющим входам с первого по четвертый преобразователь кодов, первый выход третьего дешифратора подключен к третьему входу первого элемента И и пятому управляющему входу преобразователя кодов, второй и третий выходы третьего дешифратора подключены соответственно к шестому и седьмому управляющим входам преобразователя кодов, первый выход четвертого дешифратора подключен к управляющему входу третьего дешифратора, выход первого элемента И подключен к входу установки О преобразователя кодовS выходы пятого дешифратора подключены к управляющим входам первого коммутатора, входы которого подключены к информационным входам устройства 2j .

Однако это устройство также обладает малым быстродействием при коммутации информационных сигналов с целью последовательного вывода их на элементы индикации, количество которых ограничено. Кроме того, большое число электрических связей с блоком ввода препятствует удалению его на большие расстояния от устройства для создания более выгодных условий работы.

Цель изобретения - повышение быстродействия .

Указанная цель достигается тем, что в устройство для записи информации в оперативную память, содержащее генератор импульсов, счетчик, первый триггер, дешифраторы с первого по пятый-, первый элемент И, блок ввода информации, преобразователь кодов, первый коммутатор, причем первый выход генератора импульсов подключен к счетному входу счетчика, второй выход - к управляющему входу первого дешифратора, выходы счетчика подключены соответственно к входам первого и второго дешифраторов, к одним из информационных входов преобразователя кодов, к входам третьего и четвертого дешифраторов, первые выходы первого и второго дешифраторов подключе- 20 тов

ны к первому и второму входам первого элемента И, выходы с пятого по восьмой второго дешифратора подключены к управляющим входам с первого по четвертый преобразователь кодов, первый выход третьего дешифратора подключен к третьему входу, первого элемента И и пятому управляющему входу преобразователя кодов, второй и третий выходы третьего дешифратора подключены соответственно .к шестому и седьмому управляющим входам преобразователя кодов, первьй выход четвертого дешифратора подключен к управляющему входу третьего дешифратора, выход первого элемента И подключен к входу установки преобразователя кодов, выходы пятого дешифратора подключены к управляющим входам первого коммутатора, входы которого являются информационными входами устройства, введены второй триггер, элементы И с второго по пятый, шестой дешифратор, регистр и второй коммутатор, причем второй выход первого дешифратора подключен к первому входу второго элемен та И, четвертый выход первого дешифратора подключен к входу установки 1 первого триггера, первому входу третьего элемента И, первому входу блока ввода информации, шестой выход первого дешифратора подключен к входу установки О первого триггера и первому входу четвертого элемента И, второй выход второго дешифратора подключен к первому вхо-ду установки 1 второго триггера, четвертый выход второга дешифратора подключен к вторым входам третьего

и четвертого элементов И, четвертый выход третьего дешифратора подключен к второму входу установки 1 второго триггера и третьим входам третьего и четвертого элементов И, первьш выход четвертого дешифратора поД|КЛючен к второму входу второгс элемента И, выход первого триггера подключен к первому входу пятого элемента И, второй вход которого подключен к выходу блока ввода информации, выход первого элемента И подключен к входу установки О второго триггера, выход второго элемента И подключен к второму входу блока ввода информации, выход второго . триггера подключен к четвертым входам третьего и четвертого элементов И, выходы третьего и четвертого элеменрегистра, выход пятого элемента И подключен к третьему входу установки 1 второго триггера и к другому информационному входу преобразователя кодов, информационные выходы которого подключены к входам шестого дешифратора, регистра и одним из информационных входов второго дешифратора, другие информационные входы которого подключены к выходам регистра, первый выход шестого дешифратора подключен к пятым входам третьего и четвертого элементов И и к первому управляющему входу второго коммутатора, второй управляющий вход которого подключен к одному из выходов шестого дешифратора, выходы второго коммутатора подключены к входам пятого дешифратора, контрольный выход преобразователя кодов подключен к четвертому входу установки 1 второго триггера.

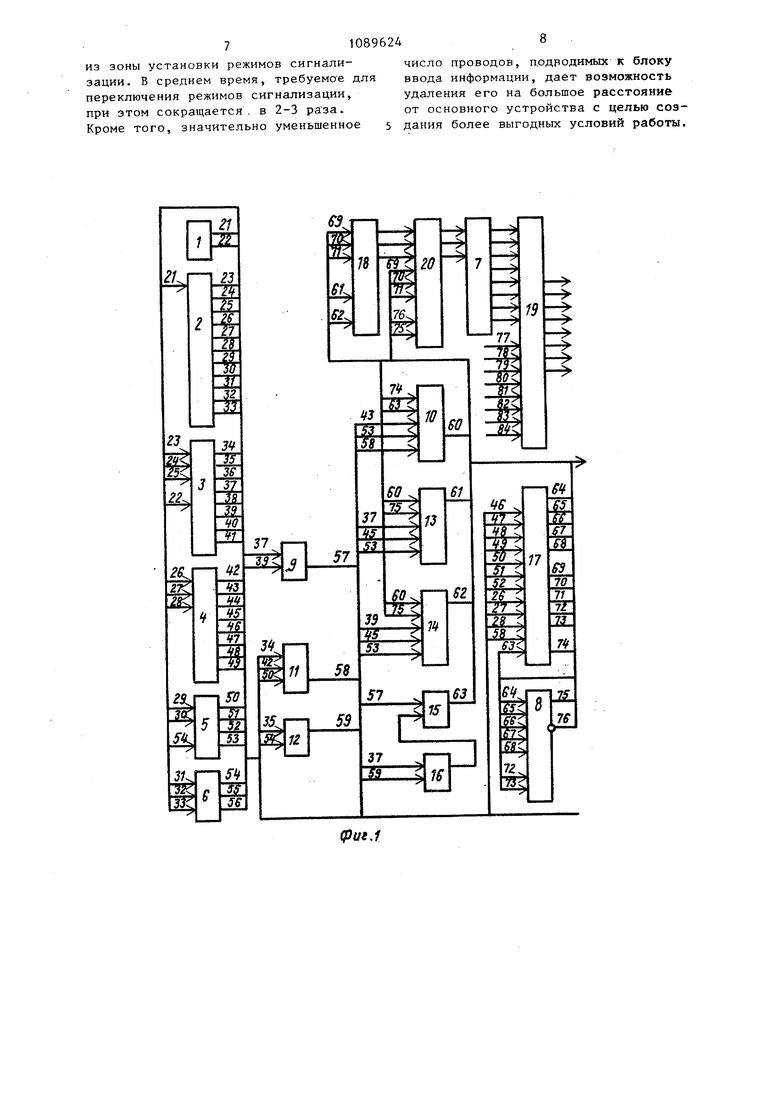

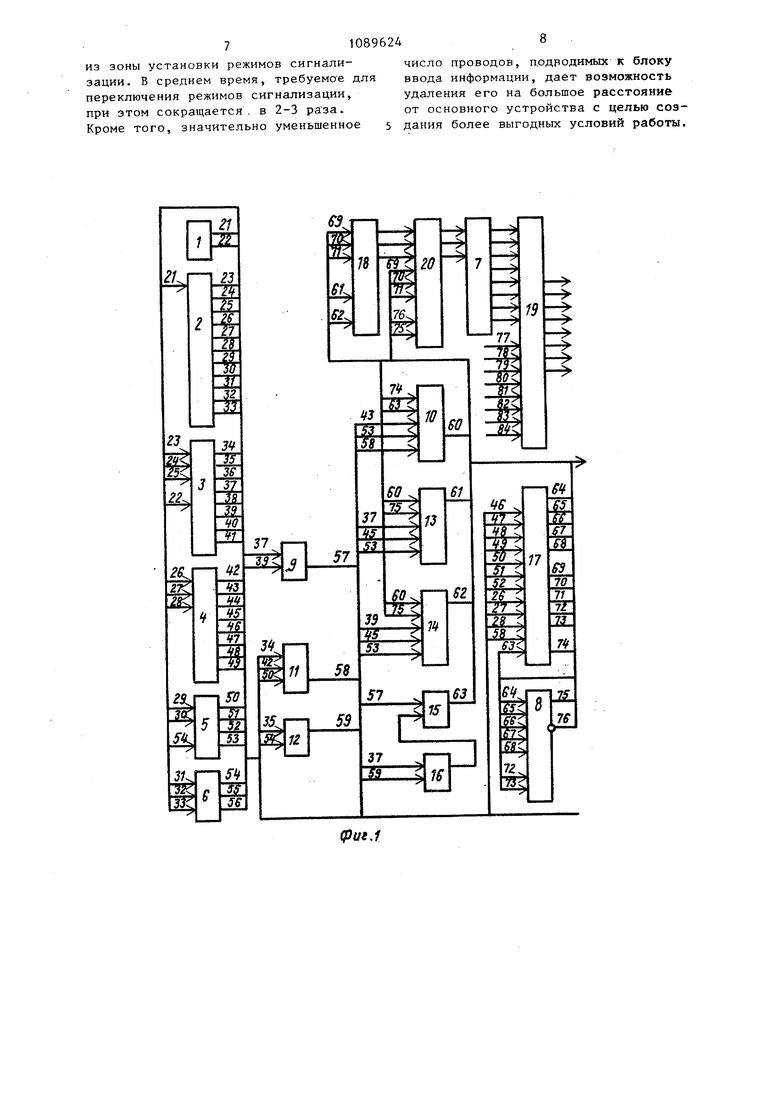

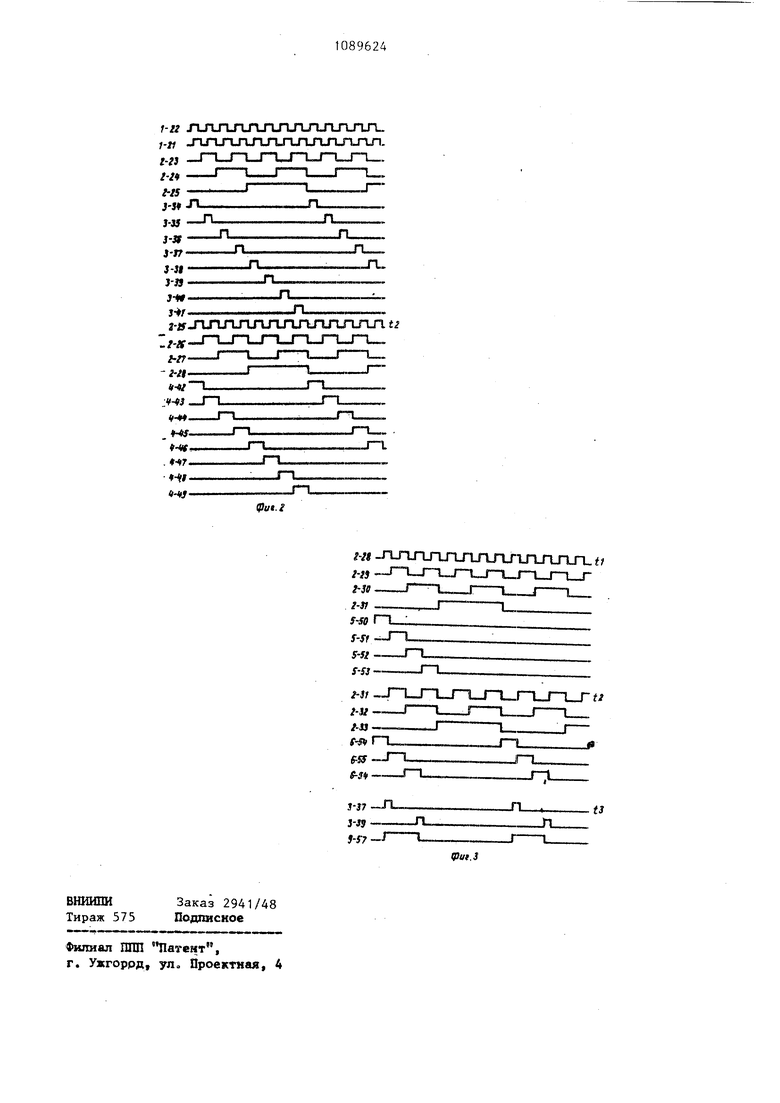

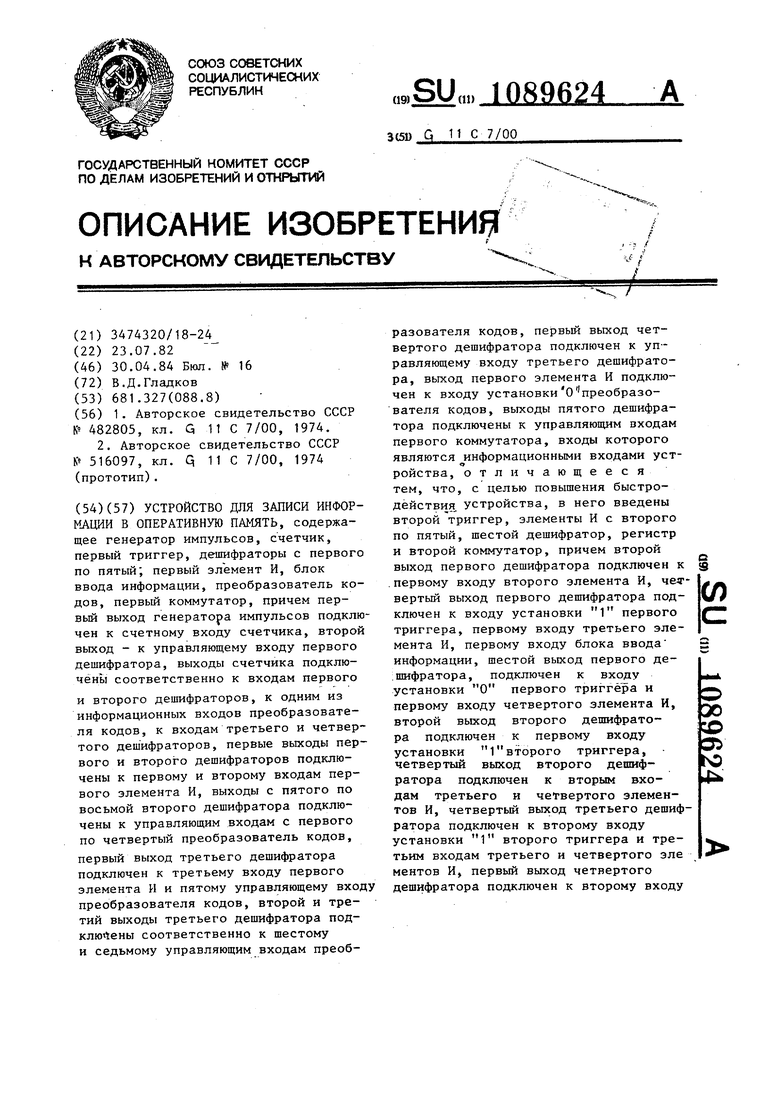

На фиг.1 изображена структурная схема устройства для записи информации в оперативную памятьJ на фиг.2 и 3 И подключены к управляющим входам временные диаграммы, иллюстрирующие работу устройства. Устройство (фиг.1) содержит генератор 1 импульсов, счетчик 2, дешифраторы 3-8 с первого по шестой, первый 9 и второй 10 триггеры, элементы И 11-15 с первого по пятый, блок 16 ввода информации, преобразователь 17 кодов, регистр 18, первый 19 и второй 20 коммутаторы. Позициями 21-76 обозначены соединения между блоками устройства, 77-84 - многоразрядные информационные входы устройства. Блок 16 содержит схему опроса кодирующих 1 обмоток, датчик кодов и кнопку ввода (на фиг.1 не показаны). Координатное поле блока 16 разделено на зоны ввод байтов, установки режимов работы и сигнализации. Устройство работает следующим образом. На выходах генератора 1, счетчика 2, дешифраторов 3-6 непрерывно вырабатываются импульсы, обеспечиваю щие упорядоченную во времени работу всех блоков устройства (фиг.2,3). Начало каждого цикла работы устройст ва определяется наличием импульса на выходе 58 элемента И 11. В это время на выходах 23-33 счетчика 2 код равен О, а на первых выходах 34, 42, 50, 54 дешифраторов 3-6 код равен 1. Импульс на выходе 58 элемента И 11 устанавливает в исходное состояние триггер 10 и преобразователь 17. этого в блок 16 посы даются на все время действия сигнала на выходе 54 дешифратора 6 импульсы с выходов 35, 37 дешифратора 3. Под воздействием этих импульсов в блоке 16 начинается опрос кодирующих обмоток, в результате чего на выходе блока 16 появляются сигналы последовательного комбинированного кода. В момент действия импульсов на выходах 50-52 дешифратора 5 эти сигн лы через элемент И 15 поступают в преобразователь 17. На выходах 64-68 преобразователя 17 формируется парал лельный двоичный код для координаты X , на выходах 69-73 формируется двоичный код для координаты Y , а при правильной работе блока 16 формируется сигнал на контрольном выходе 74. В момент действия импульса на выходе 53 дешифратора 5 в случае наж тия кнопки ввода блока 16ч одиночный сигнал на его выходе устанавливает триггер 10 в положение 1. Сигнал на выходе 75 шифратора 8 появляется при положении датчика кодов блока 16 в зоне установки режимов сигнализаци В этом случае через коммутатор 20 на вход дешифратора 7 проходит код, по-ступающий с выходов 69-71 преобразователи 17. Число выходов дешифратора 7 равно числу режимов сигнализации, названия которых изображены в прямоугольниках зоны установки режимов сигнализации блока 16. Дешифратор 7 управляет прохождением через коммутатор 19 групп информационных си 4 налов, поступающих со входов 77-84 устройства. С выходов коммутатора 19 сигналы поступают на элементы индикации (не показаны). Переключение режимов сигнализации достигается перемещением датчика кодов блока 16 в зоне установки режимов сигнализации. Для перевода какого-либо режима сигнализации в основной режим необходимо нажать кнопку ввода блока 16 при положении датчика кодов над соответствующим прямоугольником зоны установки режимов сигнализации. В этом случае код с выходов 69-71 преобразователя 17 запишется в регистр 18 под воздествием сигналов на выходах 61, 62 элементов И 13 и 14. При выводе датчика кодов из зоны установки режимов сигнализации на выходе 76 дешифратора 8 появится сигнал, разрешающ1Й1 прохождение кода регистра 18 через коммутатор 20. При этом на выходе дешифратора 7 появится сигнал, разрешающий подачу на. элементы индикации группы информационных сигналов в соответствии с выбранным основным режимом сигнализации. Количество режимов сигнализации определяется количеством групп информационных сигналов, подключаемых к элементам индикации, Наибольшее число сигналов, входящих в группу, равно числу элементов индикации . Технико-экономическое преимущество предлагаемого устройства по сравнению с прототипом заключается в повышении быстродействия при переключении режимов сигнализации, число которых равно числу групп информационных сигналов, подключаемых к элементам индикации, количество которых из-за конструктивных особенностей устройства ограничено. В прототипе 2 для установки какого-либо режима сигнализации необходимо совместить датчик кодов с соответствующим квадратом зоны установки режимов сигнализации блока ввода информации, а затем нажать кнопку ввода. В пред1 ргаемом устройстве переключение режимов сигнализации достигается при перемещении датчика кодов в зоне установки режимов сигнализации без использования кнопки ввода. Кнопка ввода в предлагаемом устройстве используется при переводе требуемого реясима сигнализации в основной режим, который всегда автоматически восстанавливается при выводе датчика кодов

из зоны установки режимов сигнализации. В среднем время, требуемое для переключения режимов сигнализации, при этом сокращается, в 2-3 раза. Кроме того, значительно уменьшенное

(put.l

число проводов, п.одродимых к блоку ввода информации, дает возможность удаления его на большое расстояние от основного устройства с целью создания более выгодных условий работы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для записи информации в оперативную память | 1974 |

|

SU482805A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для записи информации в оперативную память | 1975 |

|

SU516097A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-30—Публикация

1982-07-23—Подача