второго счетчика и первому входу первого вычитателя, второй вход которого является четвертым входом блока, счетный вход второго счетчика является третьим входом блока, первый обнуляющий вход второго счетчика подключен к обнуляющему входу первого счетчика и является вторым входом блока, выход переполнения первого счетчика подключен к второму

обнуляющему входу второго счетчика, выход первого вычитателя подключен к информационному входу второго счетчика, выход схемы сравнения подключен к счетному входу первого счетчика, установочному входу второго счетчика и является третьим выходом блока, а выход второго счетчика является первым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Ультразвуковой дефектоскоп | 1990 |

|

SU1746298A1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| Устройство для передачи телеметрической информации | 1984 |

|

SU1231529A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

| Устройство для отображения формы регистрируемого процесса | 1978 |

|

SU732668A1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

1. УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ЭЛЕКТПТЧЕСКИХ СИГНАЛОВ, содержащее последовательно включенные первый коммутатор, усилитель и аналого-цифровой преобразователь, первый блок памяти, информационный вход которого подключен к выходу аналого-цифрового преобразователя, второй ком гутатор, выход которого подключен к управляющему входу первого блока памяти, и циЛроаналоговый преобразователь, выход которого подключен к третьему входу первого коммутатора, первый вход которого является информационным входом устройства, вход записи-считывания первого блока памяти объединен с первым входом второго коммутатора и является входом записи-считьтания устройства, второй и третий входы второго коммутатора являются входами тактовой частоты записи и считывания соответственно, входы кода адреса и установки адреса первого блока памяти являются адресными входами устройства, второй вход первого коммутатора является входом автокалибровкй устройства, отлич аютее с я тем, что, с целью повышения быстродействия устройства, оно содержит блок коррекции, первый и второй Входы которого подключены к выходу аналого-цифрового преобразователя и к входу автокалибровки устройства соответственно, третий и четвертый входы являются входами тактовой частоты устройства и опорного кода устройства соответственно, а первый выход подключен к входу цифроаналргового преобразователя, третий коммутатор, входы которого подключены к входу § автокалибровки устройства, четвертому выходу блока коррекции и выходу (Л первого блока памяти соответственно, второй блок памяти, адресный вход которого подкльэчен к выходу третьего коммутатора, а информационный вход и вход записи подключены соответственно к второму и третьему выходам блока коррекции соответственно, и сумел матор, входы которого подключены к выходам первого и второго блоков 4: памяти, а выход является выходом устройства. О5 2. Устройство по П.1, отли чающееся- тем, что блок коррек дии содержит первый и второй счетчики, схему сравнения, первый и второй вычитатели, причеь выход первого счетчика является четвертым выходом блока и подключен к первому входу схемы сравнения, второй вход которой является первым входом блока и соединен с первым входом второго вычитателя, вьгход которого является вторым выходом блока, второй вход второго выч1.тателя подключен к выходу

Изобретение относится к автоматике и вычислительной технике и может быть использовано для исследования. формы однократных электрических сигналов.

Известно устройство для регистрации электрических сигналов, содержащее усилитель, аналого-цифровой преобразователь, блок памяти, преобразователь кодов, матричную индикаторную панель, распределитель, счетчик, дешифратор, делитель, двухчастотный генератор, блок управления, три коммутатора, два триггера, сумматор, блок запрета и переключатель Щ .

. К недостаткам данного устройства относятся относительно высокие погрешности преобразования, обусловленные нелинейностью усилителя, аналого-цифрового преобразователя и дрейфом их параметров в зависимости от условий работы и времени, а также недостаточно высокое быстр.одействие устройства, ограничивающееся быстродействием блока памяти.

Наиболее близким к предлагаемому по технической сущности является устройство для регистрации электрических сигналов, содержащее последовательно соединенные усилитель, аналого-цифровой преобразователь, первый коммутатор, блок памяти, преобразователь кодов, соединенный с горизонтальными шинами индикаторНой панели, вертикальные пп1ны которой соединены с выходами распределителя, вход которого соединен с |тактовым входом блока памяти и вы|ходом второго коммутатора, имеютртч.-i

совместно с первым коммутатором несколько входов, два входа и выход компаратора кодов соединены с выходами аналого-цифрового преобразователя, блока памяти и с одним из Входов второго коммутатора, а два выхода цифроаналогового преобразователя связаны соответственно через входной коммутатор с входом усилителя и с одним из входа з первого коммутатора 2 ,

Однако быстродействие известного устройства остается невысоким и ограничивается тем, что автокалибровка производится после каждого цикла регистрации и время ее проведения прямо пропорционально емкости блока памяти.

Цель изобретения - повышение бысродействия устройства за счет уменьшения времени перехода от режима записи к режиму считывания и времени проведения автокалибровки.

Уменьшение времени проведения автокалибровки достигается тем, что в отличие от известного предлагаемое устройство осуществляет к.глибровку не каждого отсчета, зарегистрированного в блоке памяти, а вычисляет поправки к каждому значению выходного кода аналогог -цифрового преобразователя. Кроме того, в предлагаемом устройстве время«затрачиваемое на калибровку одной точки, существенно меньше за счет использования априорной информации о диапазоне возможных отклонений калибруемого уровня квантования.

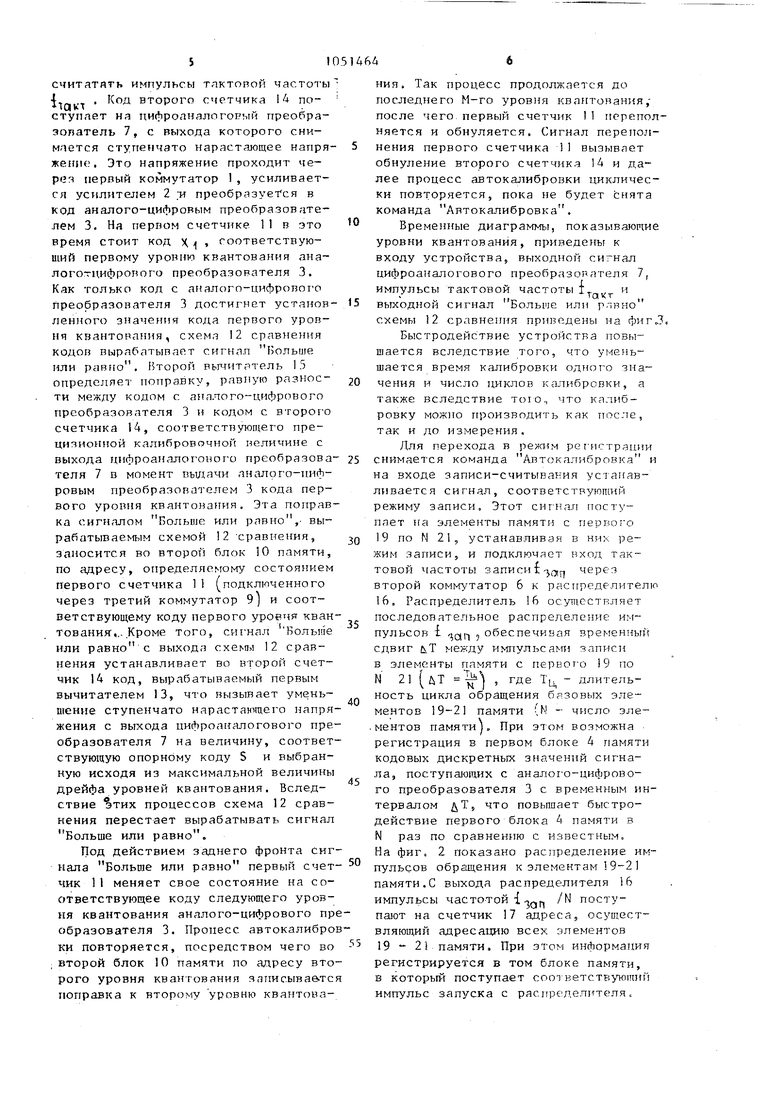

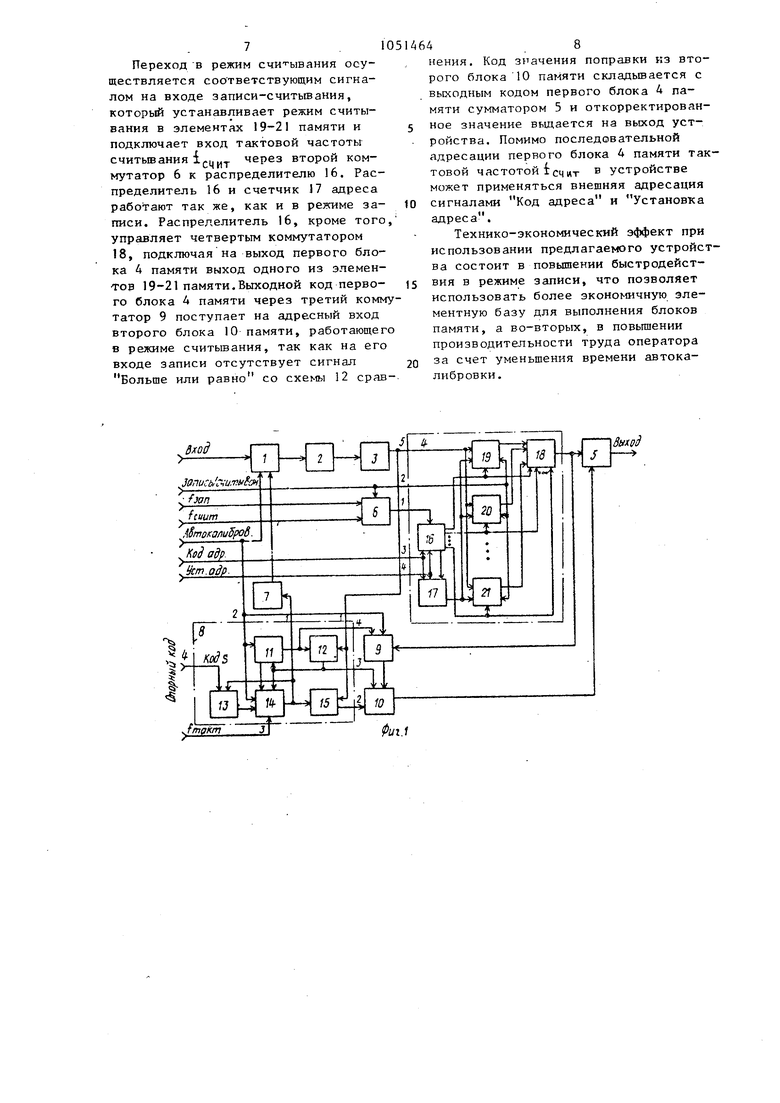

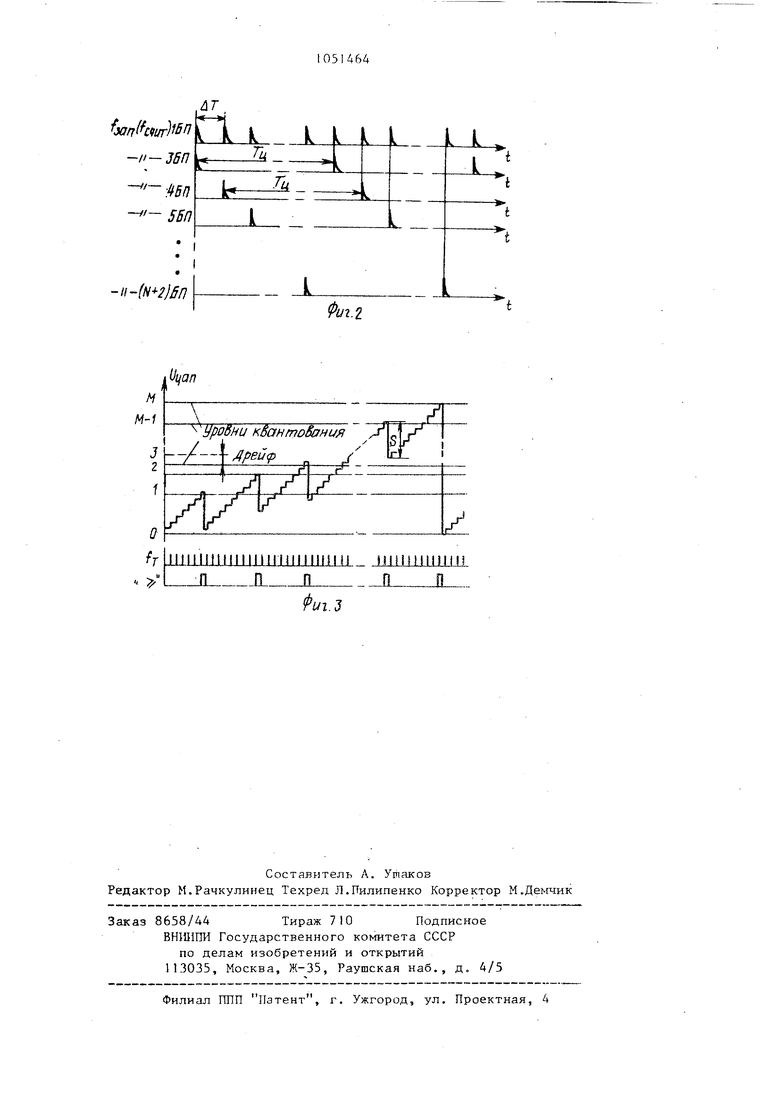

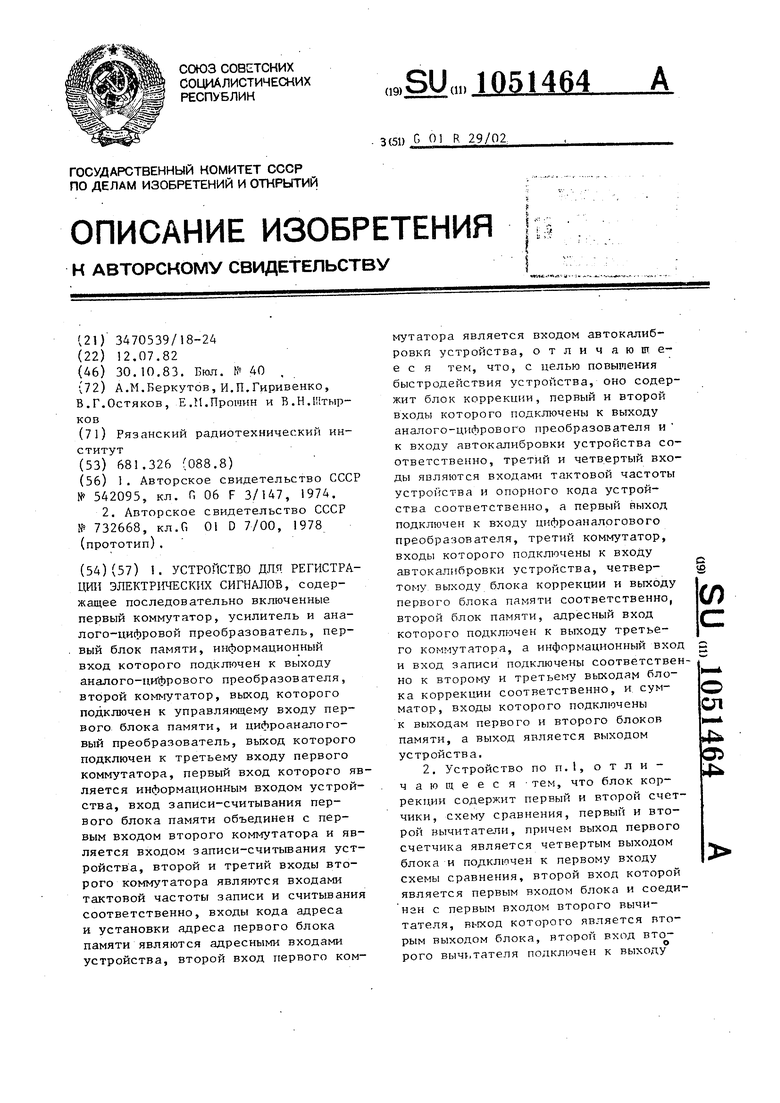

Поставленная цель достигается тем, что устройство для регистрации электрических сигналов, содержащее последовательно включенные первый коммутатор, усилитель и аналого-цифровой преобразователь, первый блок памяти, информационный вход которого подключен к выходу аналого-цифрового преобразователя, второй коммутатор, выход которого подключен к управляющему входу первого блока памяти, и цифроаналоговый преобразователь, вьгход которого подключен к третьему входу первого коммутатора, первый вход которого является информационным входом устройства, вход записи-считывания первого блока памяти объединен с первым входом вто рого коммутатора и является входом записи-считывания устройства, второй и третий входы второго коммутатора являются входами тактовой частоты записи и считывания.соответственно входы кода адреса и установки адреса первого блока памяти являются адресными входами устройства, второй Вход первого коммутатора является входом автокалибровки устройства, дополнительно содержит блок коррекции, первый и второй входы которого подключены к выходу аналого-цифрового преобразователя и к входу автокалибровки устройства соответственно третий и четвертый входы являются входами тактовой частоты устройства и опорного кода устройства соответственно, а первый выход подключен к входу цифроаналогового преобразователя, третий коммутатор, входы которого подключены к входу автокалиб. ровки устройства, четвертому выходу блока коррекции и выходу первого бло ка памяти соответственно, второй блок памяти, адресный вход которого подключен к выходу третьего коммутатора, а информационный вход и вход записи подключены соответственно к второму и третьему выходам блока коррекции соответственно, и сумматор, входы которого подключены к выходам первого и второго блоков памяти, а выход является выходом устройства. Кроме того, блок коррекции содержит первый и второй счетчики, схему сравнения, первый и второй вычитатели- причем выход первого счетчика является четвертым выходом блока и подключен к первому входу схемы сравнения, второй вход которой является первым входом блока и соединен с первым входом второго вычитателя, выход которого является вторым выходом блока, второй вход второго вычитателя подключен к выходу второго счетчика и первому входу первого вычитателя, второй вход которого является четвертым вхоДом блока, счетный вход второго счетчика является третьим входом блока, первый обнуляющий вход второго счетчика подключен к обнулякж1ему входу первого счетчика и является вторым входом блока, выход переполнения первого счетчика подключен к второму обнуляющему входу вторго счетчика, вьгход первого вычитателя подключен к информационному входу второго счетчика, выход схемы сравнения подключен к счетному входу первого счетчика, установочному входу второго счетчика и является третьим выходом блока, а выход второго счетчика является первым выходом блока На фиг. приведена блок-схема предлагаемого устройства; на фиг,2 и 3 - диаграммы, поясняющие его работу. Устройство для регистрации электрических сигналов содержит первый коммутатор 1, усилитель 2, аналогоцифровой преобразователь 3, первый блок 4 памяти, сумматор 5, второй коммутатор 6, цифроанапоговый преобразователь 7, блок 8 коррекции, третий коммутатор 9 и второй .блок 1 О памяти. Блок 8 коррекции (фиг.1) содержит первый счетчик 11, схему 12 сравнения, первый вычитатель 13, второй счетчик 14 и второй вычитатель 15. Первый блок 4 памяти содержит (фиг.1) распределитель 16, счетчик 17 адреса, четвертый комьгутатор 18, элементы памяти с первого 19 по. t4 21. Устройство работает следующим образом. Перед началом регистрации, как правило, производится автокапибровка устройства по команде Автокалибровка. Отсутствие этой команды устанавливает первый 11 и второй 14 счетчики в нуль. Подача команды Автокалиброзка разрешает работу этим счетчикам, подключает выход цифроаналогового преобразователя 7 к входу усилителя 2 через первый коммутатор 1, а адресный вход второго блока 10 памяти - к выходу первого счетчика 11 через третий коммутатор 9. Второй счетчик 14 начинает считатять импульсы тлктопон частоты { , Код второго счетчика 1i поступает ня пифроаналогорый преобразопатель 7, с выхода которого снимается ступенчато нарастающее напряжеиие, Это напряжение проходит че- Рзя первый коммутатор , усиливается усилителем 2 v преобразуется в код аналого-цифровым преобразователем 3. На первом счетчике 11 в это время стоит код х i соответствующий первому уровню квантования аналоготцифрового преобразователя 3. Как только код с аналого-цифрового Преобразователя 3 достигнет установленного зпачеи я кода первого уровня квантования, схема 12 сравнения кодов вырабатывает сигнал Больше или равно. Второй вычитятель 15 определяет ноправку, равную разности между кодом с аналого-цифрового преобразователя 3 и кодом с второго счетчика 14, соответствующего прецизионной калибровочной неличине с выхода цифроаналогоного преобразова теля 7 в момент въщачи аналого-нифровым преобразователем 3 кода первого уровня квантования. Эта поправ ка сигналом Больше или равно,- вырабатываемым схемой 12 сравнения, заносится во второй блок 10 памяти, по адресу, определяемому состоянием гтервого счетчика 1 1 (подключенного через третий коммутатор 9 и соответствующему коду первого уровня кван тования,.. Кроме того, сигнал Больше или равно с выхода cxeNn,i 12 сравнения устанавливает во второй счетчик 14 код, вырабатываемый первым вычитателем 13, что вызывает уменьшение ступенчато нарастающего напря жения с выхода цифроаналогового пре образователя 7 на величину, соответ ствующую опорному коду S и выбранную исходя из максимальной величины дрейфа уровней квантования. Вследствие тих процессов схема 12 сравнения перестает вырабатывать сигнал Больше или равно. Под действием заднего фронта сиг нала Больше или равно первый счет чик 11 меняет свое состояние на соответствующее коду следующего уровня квантования аналого-цифрового пр образователя 3. Процесс автокалибро ки повторяется, посредством чего во второй блок 10 памяти по адресу вто рого уровня квантования записываетс поправка к второму уровню квантования. Так процесс продолжается до последнего М-го уровня квантования,после чего, первый счетч1тк 1 1 переполняется и обнуляется. Сигнал переполнения первого счетчика 11 вызывает обнуление второго счетчика 14 и далее процесс автокалибровки циклически повторяется, пока не будет снята команда Автокалибровка. BpeMeinfbie диаграммы, показывающие уровни квантования, приведеньг к входу устройства, выходной сигнал цифроаналогового преобразователя 7, импульсы тактовой частоты 1 и выходной сигнал Болыие или рлнно схемы 12 сравнения приведены на фигЛ Быстродействие устройства пов,шается вследствие того, что уменьшается время калибровки одного значения и число циклов калибровки, а также вследствие тою, что калибровку можно производить как после, так и до измерения. Для перехода в режим регистрации снимается команда Автокалибровка и на входе записи-считывания yciaiiaBливается сигнал, соответствующий режиму записи. Этот сигнал поступает на элементы памяти с первого 19 по N 21, устанавливая в них режим записи, и подключает вхо/х тактовой частоты записи ) через второй коммутатор 6 к распределителю 16, Распределитель 16 осутпссттзляет последовательное распределение импульсов i ,g|., j обеспечивая вреь енный сдвиг b.T между импульс записи в элементы памяти с первог-о 19 по N 21 (дТ , где Тц - длительность цикла обращения базовых элементов 19-21 памяти ,N - число элементов памяти. При этом возможна регистрация в первом блоке 4 памяти кодовых дискретных значений сигнала, поступающих с аналого-цифрового преобразователя 3 с временным интервалом и Т, что повышает быстродействие первого блока 4 памяти в N раз по сравнению с известным. На фиг. 2 показано распределение импульсов обращения к элементам 9-2 1 памяти.С выхода распределителя 16 импульсы частотой i /N поступают на счетчик 17 адреса, осуществляющий адресацию всех элементов 19 - 21 памяти. При этом информация регистрируется в том блоке памяти, в который поступает cooiветствуюшиП импульс запуска с распределителя.

Переход/в режим счи- ывания осуществляется соответствующим сигналом на входе записи-считьшания, который устанавливает режим считывания в элементах 19-21 памяти и подключает вход тактовой частоты считьшания через второй коммутатор 6 к распределителю 16. Распределитель 16 и счетчик 17 адреса работают так же, как и в режиме записи. Распределитель 16, кроме того управляет четвертью коммутатором 18, подключая на выход первого блока 4 памяти выход одного из элементов 19-21 памяти.Выходной код первого блока Д памяти через третий коммтатор 9 поступает на адресный вход второго блока 10 памяти, работающег в режиме считьюания, так как на его входе записи отсутствует сигнал Больше или равно со схемы 12 сравнения. Код значения поправки кз второго блока 10 памяти складьшается с выходным кодом первого блока А памяти сумматором 5 и откорректированное значение выдается на выход устройства. Помимо последовательной адресации первого блока 4 памяти тактовой частотой Тсщдт в устройстве может применяться внешняя адресация сигналами Код адреса и Установка адреса.

Технико-экономический эффект при использовании предлагаемого устройства состоит в повышении быстродействия в режиме записи, что позволяет использовать более экономичную элементную базу для выполнения блоков памяти, а во-вторых, в повышении производительности труда оператора за счет уменьшения времени автокалибровки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для отображения формы регистрируемого процесса | 1974 |

|

SU542095A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для отображения формы регистрируемого процесса | 1978 |

|

SU732668A1 |

Авторы

Даты

1983-10-30—Публикация

1982-07-12—Подача