ходы третьего, восьмого, девятого и одиннадцатого элементов И подкл чены соответственно к первому, второму, третьему и четвертому входам третьего элемента ИЛИ, выход которого является третьим выходом запоминающего элемента, выходы четвертого и десятого элементов И подключены соответственно к третьему и четвертому входам первого элемента ИЛИ., выходы двенадцатого, пятнадцатого и шестнадцатого элементов И подключены соответственно к первому, второму и третьему входам четв.ертого элемента ИЛИ, выход которого является четвертым выходом эапоминакядего элемента, а выходы пятого, шестого и седьмого элементов И подключены соответственно к первому, второму и третьему входам пятого элемента ИЛИ, выход которого является пятым выходом запоминаюи1его элемента .

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный запоминающий элемент | 1982 |

|

SU1057988A1 |

| Блок поиска информации для ассоциативного запоминающего устройства | 1982 |

|

SU1049973A1 |

| Блок поиска информации для ассоциативного запоминающего устройства | 1982 |

|

SU1057989A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1092566A1 |

| Устройство для синтаксического контроля | 1987 |

|

SU1474679A1 |

| Логическая ячейка для ассоциативного запоминающего устройства | 1981 |

|

SU980162A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| Конвейерное устройство для умножения шестнадцатиразрядных чисел | 1984 |

|

SU1291970A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

АССОЦИАТИВНЫЙ ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ, содержащий триггер, первый и второй элементы ИЛИ и пер вый и второй элементы И, первые входы которых Объединены и являются первым входом запоминающего элемента, второй вход первого зле-) мента И .подключен к первому вы.- , ходу триггера, второй вход второго элемента И является вторым входом запоминающего элемента, а выходы элементов И подключены соответственно к первому и второму входам первого элемента ИЛИ, вы-. ход которого является первым выходом запоминающего элемента, первый вход и выход второго элемента ИЛИ являйтся соответственно третьим входом и четвертым выходом запоминающего элемента, о т л и ч аю щ и и с я тем, что, с целью ; расширения области его применения за счет осуществления поиска по большему числу критериев, в него введены элемент И-НЕ, элементы НЕ., эле менты И с третьего по семнадцатый и элементы ИЛИ с третьего по пятый, причем первые входы элементов И с третьего по седьмой подключены к перво мУ входу запоминающего элемента, первые входы восьмого, девятого и десятого и вторые входы второго, шестого и седьмого элементов И подключены к второму входу запоминающего элемента, первый вход элемента И-НЕ подключен к третьему входу запоминающего элемента, первый вход одиннадцатого и второй вход третьего элементов И, первые входы двенадцатого, тринадцатого и четыр.надцатого и вторые входы восьмого, девятого, десятого и одиннадцатого элементов И, первые входы пятнадцатого, шестнадцатого и семнадцатого элементов И, вход первого элемента НЕ, выход семнадцаi того и третий вход третьего элементов И, вход второго элемента НЕ, (Л выход тринадцатого и второй вход двенадцатого элементов И, выход элемента И-НЕ и третьи входы десятого, одиннадцатого и двенадцатого элементов И объединены соответственно и являются входами запоминающего элемента с четвертого по девятый, первый выход триггера подключен к вторьм входам первого, пятого, тринадцатого,четырнадцатого, пятнадцатого и семнадцатого, ел третьим входам шестого и восьмого оо и четвертым входам десятого и одиннадцатого элементов и, второй выход триггера подключен к третьему № ю входу девятого и четвертым входам третьего и двенадцатого элементов И, выход второго элемента НЕ подключен к четвертому входу девятого элемента И, выход первого элемента НЕ подключен к вторым входам четвертого и шестнадцатого, .третьим входам пятого и седьмого и пятым входам девятого, десятого и оди р н адца то го элеме н то в И, выход четырнадцатого элемента И .подключен к вторые входам второго ИЛИ и элемента И-НЕ, вы

1

Изобретение от;носится к вычислительной технике, в частности к запоминающим устройствам.

Известен ассоциативный эапомин квдий элемент, содержащий триггер и элементы И-НЕ, причем первый и второй входы первого элемента И-НЕ подключены соответственно к первому выходу триггера и первому выводу элемента, первый и второй входы второго элемента И-НЕ подключены соответственно к второму выходу триггера и второму выводу, а выходы первого и второго элементов И-НЕ подключены к третьему выводу элемента -1

Недостатком этого ассоциативно запоминакюдего элемента является ограниченность поисковых возможностей. .

Наиболее близким техническим ршением к изобретению является ассоциативный запоминакяций элемент, содержащий триггер, элементы И и элементы ИЛИ, причем первый вывод элемента подключен к первым входам первого и второго элементов И, вторые входы которых подключены соответственно к первому выходу триггера и второму выводу элемента, а выходы-подключены соответственно к первому и второму входам первого элемента ИЛИ, выход которого подключен к третьему выводу элемента, а первый вхо второго элемента ИЛИ, выход-которого подключен к четвертому выводу элемента, подключен к пятому выводу элемента 2J .

Недостатком данного элемента являются ограниченные поиском по максимуму функциональные возможности, что снижает область применения устройства.

Целью изобретения является расширение области применения ассоциативного запоминающего элемента

за - счет осуществления поиска по большему числу критериев, в частности осуществления поиска в массиве хранимых признаков ,i ATi 5 таких признаков Хк то

-VE-,n; XK-XJ V,

или

4l--,Y , Xg- ,

где Y - признак-опроса.

Поставленная цель достигается тем, что в ассоциативный запоминакяций элемент, содержащий триггер, первый и второй элементы ИЛИ и первый и второй элементы и, первые входы которых объединены и являются первым входом запоминаквдего элемента, второй вход первого элемента И подключен к первому выходу триггера, второй вход второго

элемента И является вторым входом запоминающего элемента, а выходы элементов И подключены соответственно к первому и второму входам первого элемента ИЛИ, выход которого является первым выходом запоминающего элемента, первый вход и выход второго элемента ИЛИ я-вля.ются соответственно третьим входом и четвертым выходом запоминаюцего элемента, введены элемент И-НЕ, элементы НЕ, элементы И с третьего по семнадцатый и элементы ИЛИ с третьего по пятый, причем первые входы элементов И с

третьего по седьмой подключены к первому входу запоминакяцего элемента, первые входы восьмого, девятого и десятого и вторые входы второго, шестого и седьмого

элементов И подключены к второму входу запоминаюв;его элемента, первый вход элемента И-НЕ подключен к третьему входу запоминанвдего элемента, первый вход одиннадцатого и второй вход третьего элементов И, первые входы двенадцатого, тринадцатого и четырнадцатого и вторые входы восьмого, девятого, Десятого и одиннадцатого элементов И, первые входы пятнадцатого, шестнадцатого и семнадцатого элементов И, вход первого элемента НЕ, выход семнадцатого и третий вход третьего элементов И вход второго элемента НЕ, выход тринадцатого и второй вход двенадт цатого элементов- И, выход элемента И-НЕ и третьи входы десятого одиннадцатого и двенадцатого элементов И объединены соответственно .и являются входами запоминающего элемента с четвертого по девятвлй, первый выход триггера подключен к вторым входам первого, пятого, тринадцатого, четырнадцатого, пят.надцатого и семнадцатого, третьим входам шестого и восьмого и четвертьм вхсадам десятого и одиннадцатого элементов И, второй выход триггера подключен к третьему входу девятого и четвертым входам третьего и двенадцатого элементов выход второго элемента НЕ подключен к четвертому входу девятого элемента и, выход первого элемента НЕ подключен к вторым входам четвертого и шестнадцатого, третьим входам пятого и седьмого и пятым входам девятого, десятого и од надцатого элементов И, выход че- . тырнадцатого элемента И подключен к вторым входам второго элемента ИЛИ и элемента. И-НЕ, выходы третьего, восьмого, девятого и одиннадцатого элементов И подключены соответственно к первому, второму, третьему и четвертому входам третьего элемента ИЛИ, выход которого является третьим выходом запоминающего элемента, выходы четвертог и десятого элементов И подключены соответственно к третьему и четвертому входам первого элемент.а ИЛИ, выходы двенадцатого, пятнадцатого и шестнадцатого элементов И подключены соответственно к первому , второму и третьему входам четвертого элемента ИЛИ, выход кбторого является четвертым выходом запоминающего элемента, а выходы пятого, шестого и седьмого элементов И подключены соответственно к первому, второму и третьему входам пятого элемента ИЛИ, выход которого является пятым выходом запоминающего элемента.

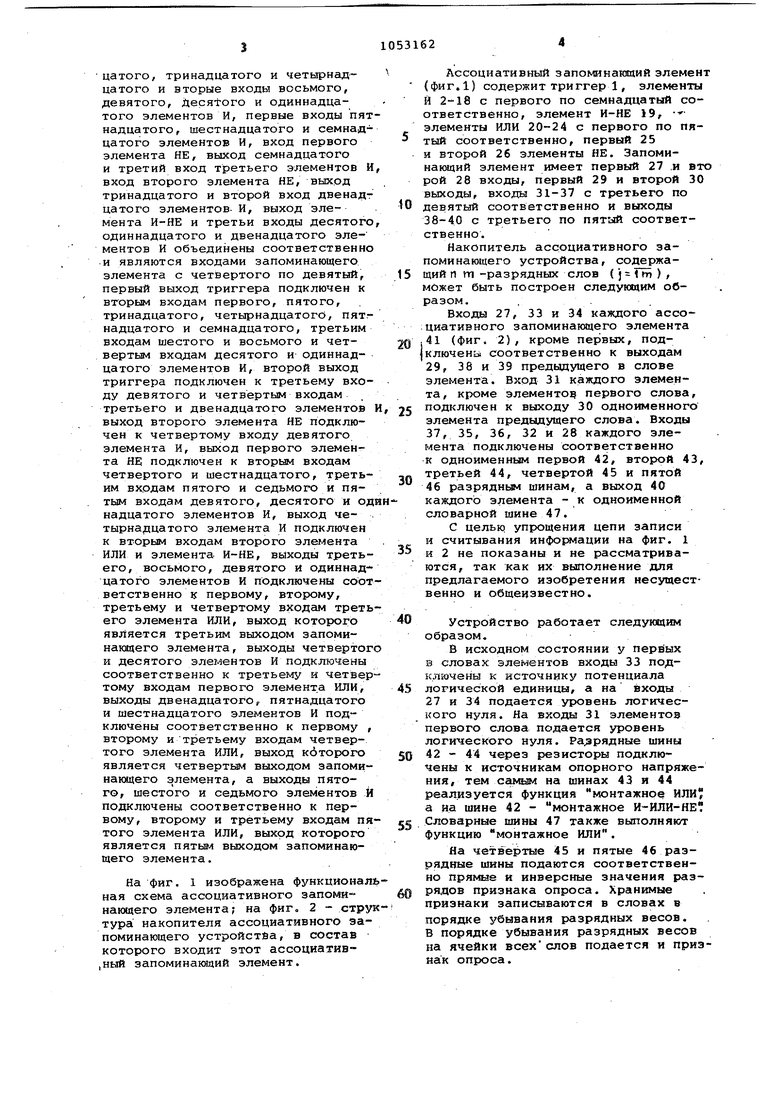

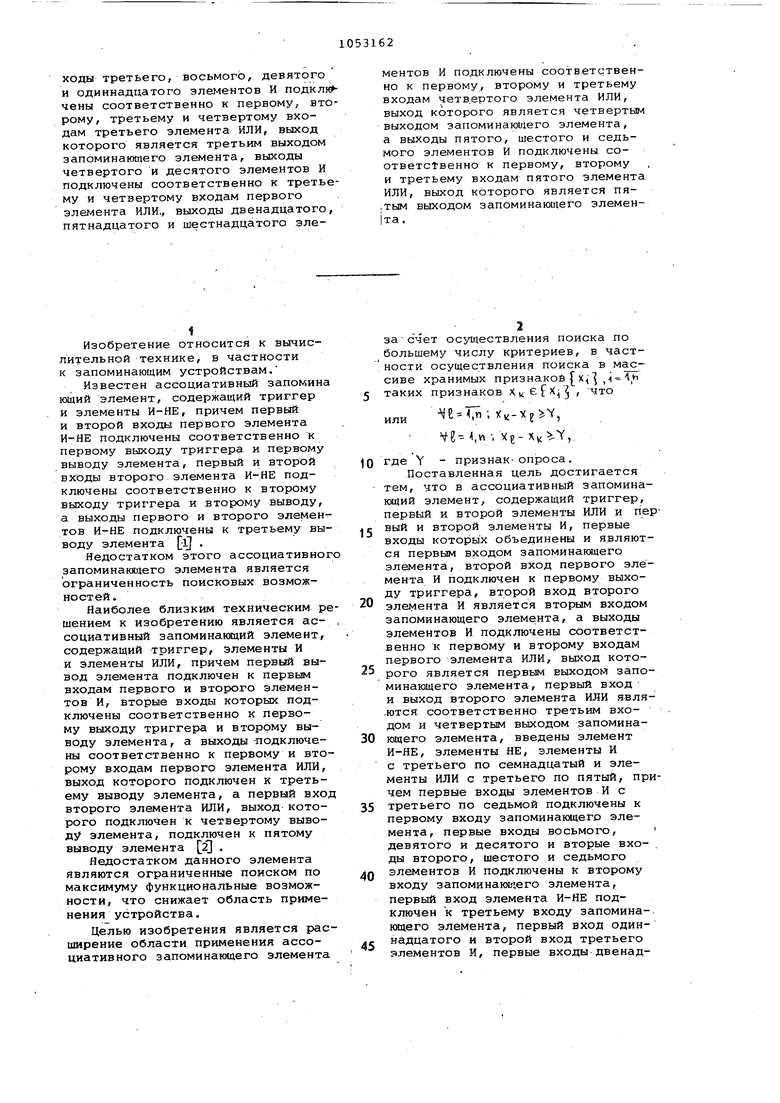

На фиг. 1 изображена функциональная схема ассоциативного запоминающего элемента на фиг. 2 - структура накопителя ассоциативного запоминающего устройстйа, в состав которого входит этот ассоциатив.ный запоминаквдий элемент.

Ассоциативный запоминающий элемент (фиг.1) содержит триггер 1, элементы И 2-18 с первого по семнадцатьлй соответственно, элемент И-НЕ 19, элементы ИЛИ 20-24 с первого по пя тый соответственно, первый 25 и второй 26 элементы НЕ. Запоминающий элемент имеет первый 27 ,и вто рой 28 входы, первый 29 и второй 30 выходы, входы 31-37 с третьего по

0 девятый соответственно и выходы 38-40 с третьего по пятый соответственно.

Накопитель ассоциативного запоминающего устройства, содержа5 щий п m-разрядных слов (j rm), может быть построен следующим образом. . .

Входы 27, 33 и 34 каждого ассоциативного запоминающего элемента

Q ,41 (фиг. 2), кроме первых, под|ключень1 соответственно к выходам 29, 38 и 39 предыдущего в слове элемента. Вход 31 каждого элемента, кроме элементов первого слова,

5 подключен к выходу 30 одноименного элемента предыдущего слова. Входы 37, 35, 36, 32 и 28 каждого элемента подключены соответственно к одноименным первой 42, второй 43, третьей 44, четвертой 45 и пятой

0 46 разрядньви шинам, а выход 40 каждого элемента - к одноименной словарной шине 47.

С целью упрющения цепи записи и считывания информации на фиг. 1

5 и 2 не показаны и не рассматриваются, так как их выполнение для предлагаемого изобретения несущественно и общеизвестно.

0 Устройство работает следующим образом.

В исходном состоянии у первых в словах элементов входы 33 подключены к источнику потенциала

5 логической единицы, а на входы 27 и 34 подается уровень логического нуля. На входы 31 элементов первого слова подается уровень логического нуля. Разрядные шины

0 42 - 44 через резисторы подключены к источникам опорного напряжения, тем caivffiiM на шинах 43 и 44 реализуется функция монтажное ИЛИ а на шине 42 - монтажное И-ИЛИ-НЕ

5 Словарные шины 47 также выполняют функцию монтажное ИЛИ.

На четвертгые 45 и пятые 46 разрядные шины подаются соответственно пряьоле и инверсные значения разрядов признака опроса. Хранимые признаки записываются в словах в порядке убывания разрядных весов. В порядке убывания разрядных весов на ячейки всехслов подается и признак опрюса. Накопитель ассоциативного зап минающего устройства, за исключе нием триггеров 1, в которых запи саны значения разрядов Хранимых признаков и которые не изменяют с состояния в процессе ассоциативного поиска, представляет собой итеративную комбинационную логическую сеть, в которой ассоциати ный поиск осуществляется за один такт, причем поиск (переходный процесс в схеме) инициируется изменением логической переменной на любом из выходов накопителя или изменением состояния любого триггера 1. При этом на выходах 38, 29, 39 и 40 j-го элемента слова вырабатываются соответстве но функции ot,,- , , и 8,j , и на j -X первой 42, второй 43 и третьей 44 разрядных шинах выра батываются соответственно функции А j, В1 и Cj , а на -и словарной шине 47 вырабатывается функцияD которые определяются следующими выражениями .i-n ii i M jAjeivZ-.Y ejCjy P;j- -,H 3 iAj8jVpj.,(,.,vY, );p«l..,2;.A,Cjvy- 2i-v8i). М .,iiYjVVjBjV, e. , . . i.i.M-o . -.-s.. 1И . где o,j ,pi,j. - логические Функции на выходах 38, 29 и .39 j -го элемента i-го слова; и 7., - логические переменны на первом и втором соответственно выходах триггера 1 элемента 41,j ; Vj и Yj - прямое и инвег сное значения j-го разряда признака опроса. Результат поиска определяется как функция состояний на словарных шинах 47 {D;) и на выходах 38 (Л,,)) и 29 (i,,) последних в словах элементовyr- i4 m P.«,№ причем равенство f логической единице означает, что признак К удовлетворяет условию поиска. Если хранимые признаки записаны в прямом коде, т. e. г.хл, где X(j - значение j -го разряда признака Х , то в результате поиска выбираются такие признаки х , что Ме,и;х;-х. Если хранимые признаки записаны в инверсном виде, т.е. Z ,-j. х , j , то в результате поиска выберутся такие признаки х; , что I - . че-Ь; xt-x. Другими словами, в результате ассоциативного поиска отмечаются максимальные (или минимальные) среди хранимых признаков, причем только те, которые отличаются от следующих в порядке убывания (возрастания) на величинуне менееY . Такой вид поиска может быть полезен, например, в автоматизированных системах управления для обнаружения опасных локальных экстремумов. Поиск максимума и минимума является частным случаем реализованного в предлагаемом устройстве по.иска и осуществляется При задании . Технико-экономическое пре-имущество предлагаемого ассоциативного запоминающего элемента по сравнению С известным заключается, таким образом, в расширении его рбласти применения.

J2 гв

0vf.2

/v/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ассоциативная запоминающая матрица | 1976 |

|

SU615543A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Фет Я.И | |||

| Параллельные процессоры для управляюсцих систем | |||

| М., Энергоиздат, 1981, с | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

Авторы

Даты

1983-11-07—Публикация

1982-06-18—Подача