Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных процессоров цифровьпс вы- числительньк машин.

Цель изобретения - повышение производительности устройства.

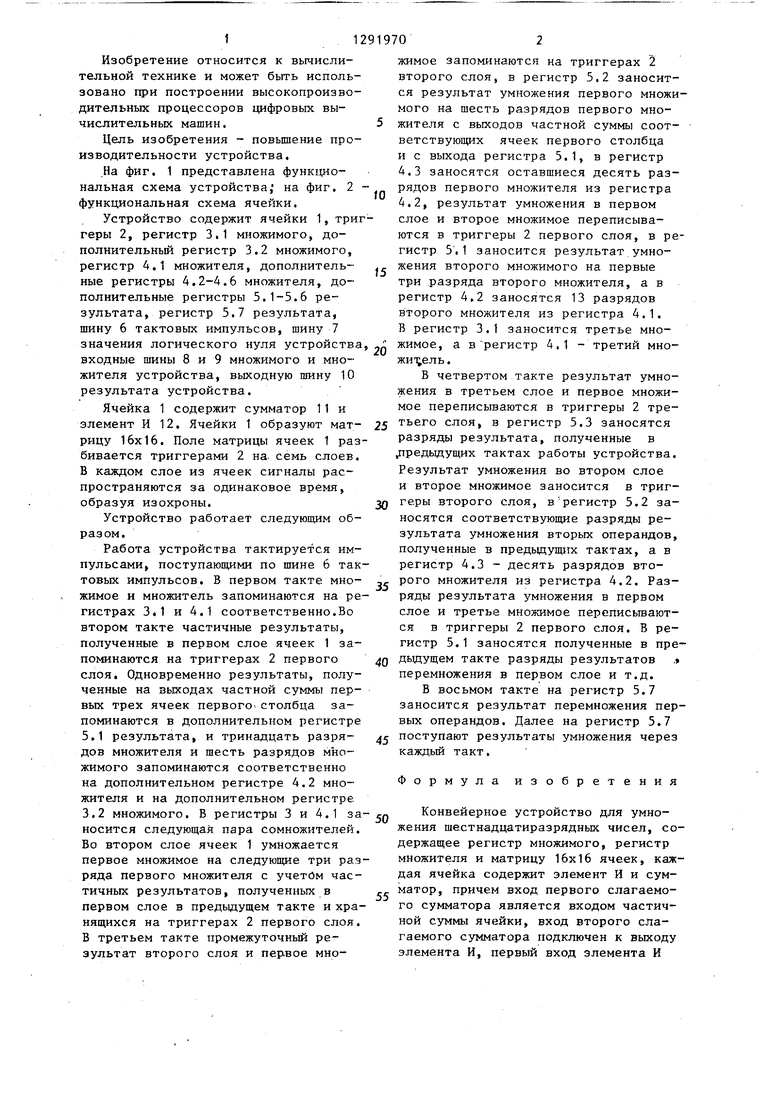

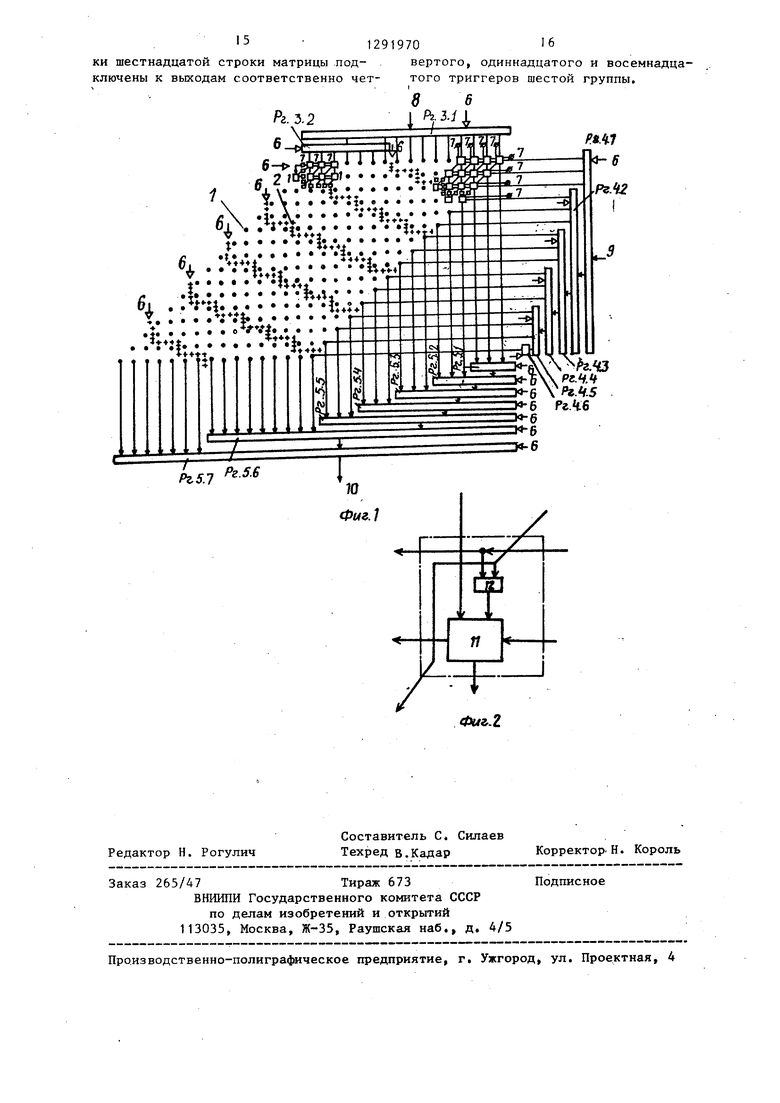

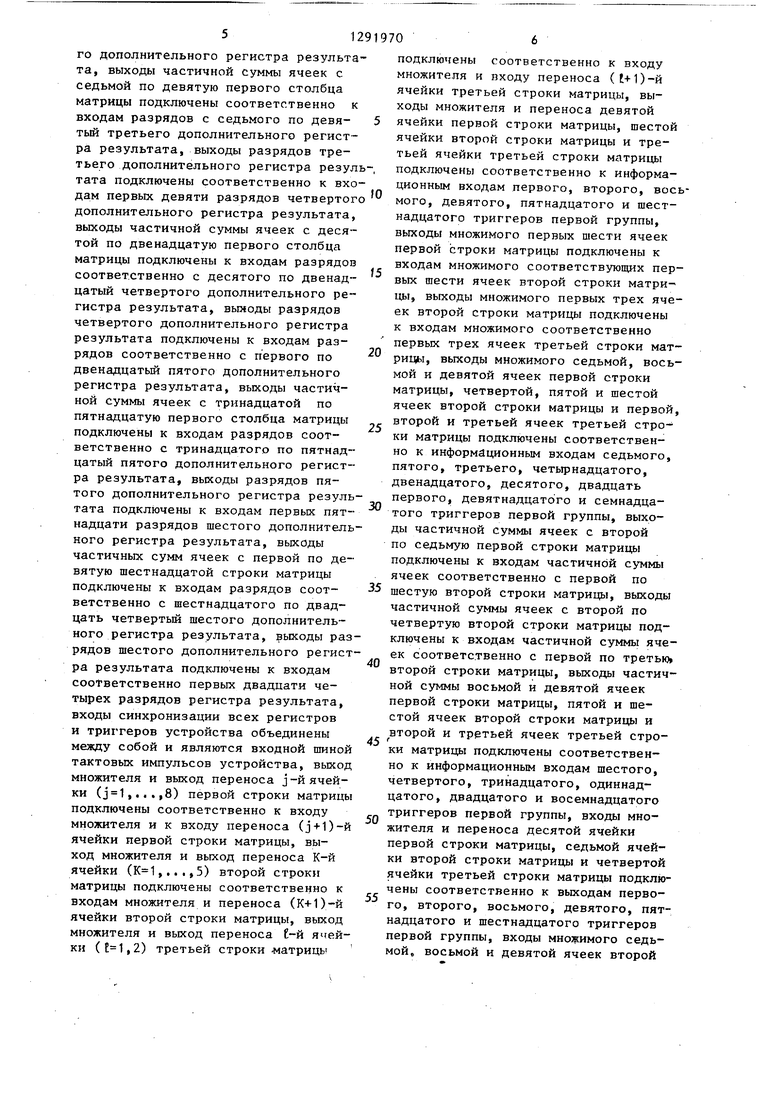

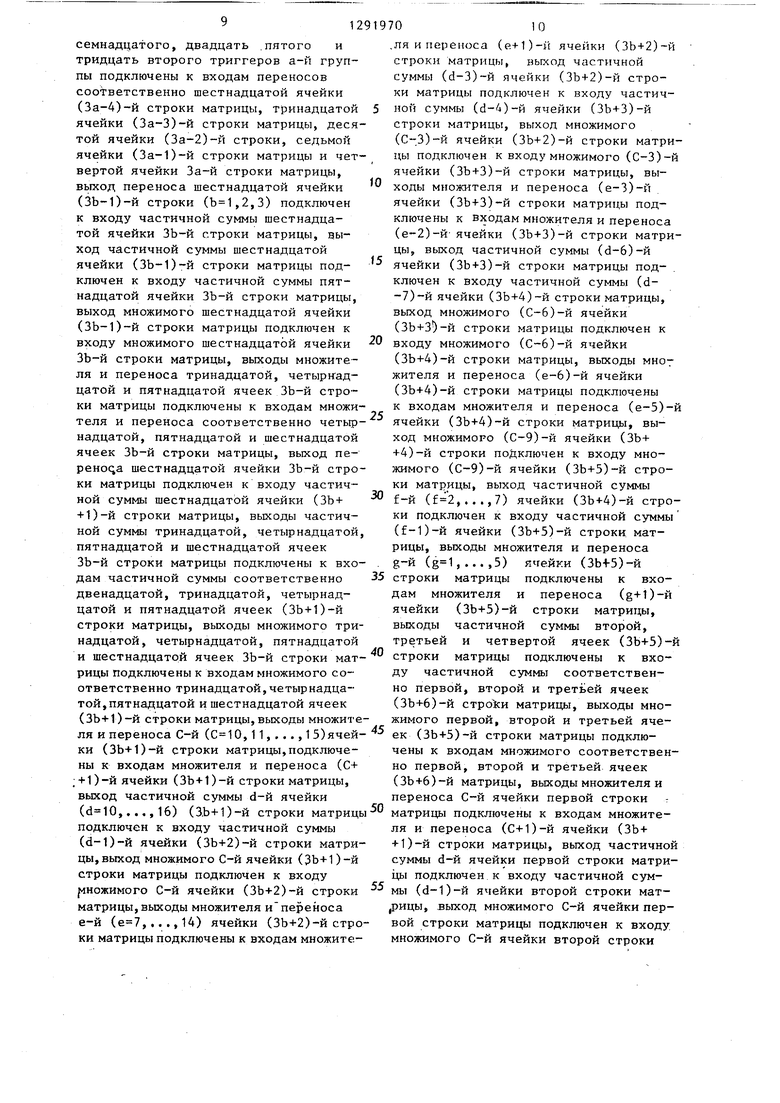

.На фиг. 1 представлена функциональная схема устройства, на фиг. 2 функциональная схема ячейки.

Устройство содержит ячейки 1, триггеры 2, регистр 3.1 множимого, до- полнительньй регистр 3.2 множимого, регистр 4.1 множителя, дополнительные регистры 4.2-4.6 множителя, дополнительные регистры 5.1-5.6 результата, регистр 5.7 результата, шину 6 тактовых импульсов, шину 7 значения логического нуля устройства, входные шины 8 и 9 множимого и множителя устройства, выходную шину 10 результата устройства.

Ячейка 1 содержит сумматор 11 и

fO

жимое запоминаются на триггерах 2 второго слоя, в регистр 5.2 заносится результат умножения первого множи мого на шесть разрядов первого множителя с выходов частной суммы соответствующих ячеек первого столбца и с выхода регистра 5.1, в регистр 4.3 заносятся оставшиеся десять разрядов первого множителя из регистра 4.2, результат умножения в первом слое и второе множимое переписываются в триггеры 2 первого слоя, в ре гистр 5. 1 заносится результат умножения второго множимого на первые три разряда второго множителя, а в регистр 4,2 заносятся 13 разрядов второго множителя из регистра 4.1. В регистр 3.1 заносится третье множимое, а в регистр 4.1 - третий мно- жит;ель.

В четвертом такте результат умножения в третьем слое и первое множимое переписьгааются в триггеры 2 тре«5

20

элемент И 12. Ячейки 1 образуют мат- 25 ьего слоя, 3 регистр 5.3 заносятся рицу 16x16. Поле матрицы ячеек 1 раз- разряды результата, полученные в

бивается триггерами 2 на- семь слоев. В каждом слое из ячеек сигналы распространяются за одинаковое время, образуя изохроны.

Устройство работает следующим образом.

Работа устройства тактируется импульсами, поступающими по шине 6 тактоБых импульсов, В первом такте мно- ,5 рого множителя из регистра 4.2. Раз40

жимое и множитель запоминаются на регистрах 3.1 и 4.1 соответственно.Во втором такте частичные результаты, полученные в первом слое ячеек 1 запоминаются на триггерах 2 первого слоя. Одновременно результаты, полученные на выходах частной суммы первых трех ячеек первого столбца запоминаются в дополнительном регистре

5.1результата, и тринадцать разрядов множителя и шесть разрядов множимого запоминаются соответственно на дополнительном регистре 4.2 множителя и на дополнительном регистре

3.2множимого. В регистры 3 и 4.1 за- Q носится следующая пара сомножителей.

Во втором слое ячеек 1 умножается первое множимое на следующие три разряда первого множителя с учетом частичных результатов, полученных в первом слое в предьщущем такте и хранящихся на триггерах 2 первого слоя. В третьем такте промежуточный результат второго слоя и первое мноряды результата умножения в первом слое и третье множимое персписьшают- ся в триггеры 2 первого слоя. В регистр 5,1 заносятся полученные в предьщущем такте разряды результатов . перемножения в первом слое и т.д, В восьмом такте на регистр 5.7 заносится результат перемножения первых операндов. Далее на регистр 5,7 поступают результаты умножения через каждый такт.

Формула изобретения

Конвейерное устройство для умножения шестнадцатиразрядных чисел, содержащее регистр множимого, регистр множителя и матрицу 16x16 ячеек, каждая ячейка содержит элемент И и сум- - матор, причем вход первого слагаемого сумматора является входом частичной суммы ячейки, вход второго слагаемого сумматора подключен к выходу элемента И, первый вход элемента И

г,

fO

2919702

жимое запоминаются на триггерах 2 второго слоя, в регистр 5.2 заносится результат умножения первого множимого на шесть разрядов первого множителя с выходов частной суммы соот ветствующих ячеек первого столбца и с выхода регистра 5.1, в регистр 4.3 заносятся оставшиеся десять разрядов первого множителя из регистра 4.2, результат умножения в первом слое и второе множимое переписываются в триггеры 2 первого слоя, в регистр 5. 1 заносится результат умножения второго множимого на первые три разряда второго множителя, а в регистр 4,2 заносятся 13 разрядов второго множителя из регистра 4.1. В регистр 3.1 заносится третье множимое, а в регистр 4.1 - третий мно- жит;ель.

В четвертом такте результат умножения в третьем слое и первое множимое переписьгааются в триггеры 2 тре«5

20

тредыдущих тактах работы устройства. Результат умножения во втором слое и второе множимое заносится в триг- 30 геры второго слоя, в регистр 5.2 заносятся соответствующие разряды результата умножения вторых операндов, полученные в предыдущих тактах, а в регистр 4.3 - десять разрядов вто

ряды результата умножения в первом слое и третье множимое персписьшают- ся в триггеры 2 первого слоя. В регистр 5,1 заносятся полученные в предьщущем такте разряды результатов . перемножения в первом слое и т.д, В восьмом такте на регистр 5.7 заносится результат перемножения первых операндов. Далее на регистр 5,7 поступают результаты умножения через каждый такт.

Формула изобретения

Конвейерное устройство для умножения шестнадцатиразрядных чисел, содержащее регистр множимого, регистр множителя и матрицу 16x16 ячеек, каждая ячейка содержит элемент И и сум- матор, причем вход первого слагаемого сумматора является входом частичной суммы ячейки, вход второго слагаемого сумматора подключен к выходу элемента И, первый вход элемента И

1291970

является входом н выходом множимого ячейки, второй вход элемента И является входом и выходом множителя ячейки, выход суммы сумматора является выходом частичной суммы ячейки, вход 5 и выход переноса сумматора являются соответственно входом и выходом переноса ячейки, информационный вход регистра множимого является входной шиной множимого устройства, информа- 0 ционный вход регистра множителя является входной шиной множителя устройства, выход регистра результата является выходной шиной результата устственно четвертой, пятом и шестои ячеек первого столбпа матрицы, выходы разрядов с четвертого по трина цатый первого дополнительного регис ра множителя подключены к соответствующим разрядам информационного входа второго дополнительного регистра множителя, выходы первых трех разрядов второго дополнительного ре гистра множителя подключен к входам множителя соответственно седьмой, восьмой и девятой ячеек первого сто бца матрицы, выходы разрядов с четвертого по десятый второго дополройства, входы множимого первых деся- -5 нительного регистра множителя под

ти ячеек первой строки матрицы подключены к выходам первых десяти разрядов регистра множимого, входы частичной суммы всех ячеек первой строк матрицы подключены к шине значения логического нуля устройства, входы переноса всех ячеек первого столбца матрицы подключены к шине значения логического нуля устройства, входы множителя первых трех ячеек первого столбца матрицы подключены к выходам первых трех разрядов регистра множителя, выход частичной суммы i-й ячей- ки шестнадцатой строки матрицы (i 10,1116) подключен к (24+i)-My

разряду информационного входа регистра результата, отличающе е- с я тем, что, с целью увеличения производительности, в него введены пять дополнительных регистров множителя, шесть дополнительных регистров результата, дополнительный регистр множимого, первую группу из двадцати од нога триггера, четьфе группы по тридцать семь триггеров и шестую группу из семнадцати триггеров, причем выходы разрядов с одиннадцатого по шестнадцатьй регистры множимого подключены к информационному входу до- полнительного регистра множимого, входы множимого ячеек с одиннадцатой по шестнадцатую первой строки матрицы подключены к вьхходам разрядов соответственно с первого по шестой дополнительного регистра множимого, выходы разрядов с четвертого по шестнадцатью регистра множителя подключены к соответствующим разрядам информационного входа первого дополнительного регистра мн жителя, выходы первых трех разрядов первого дополнительного регистра множителя подключены к входам множителя cooTBeT

ственно четвертой, пятом и шестои ячеек первого столбпа матрицы, выходы разрядов с четвертого по тринадцатый первого дополнительного регистра множителя подключены к соответствующим разрядам информационного входа второго дополнительного регистра множителя, выходы первых трех разрядов второго дополнительного регистра множителя подключен к входам множителя соответственно седьмой, восьмой и девятой ячеек первого столбца матрицы, выходы разрядов с четвертого по десятый второго допол25

35

О .

0

5

0

5

ключены к входам соответствующих разрядов третьего дополнительного регистра множителя, выходы первых трех разрядов третьего дополнительного регистра множителя подключены к входам множителя соответственно десятой, одиннадцатой и двенадцатой ячеек первого столбца матрицы, выходы разрядов с четвертого по седьмой третьего дополнительного регистра множителя подключены к входам,соответствующих разрядов четвертого дополнительного регистра множителя, выходы первых трех разрядов четвертого дополнительного регистра множителя подключены к входам множителя соответственно тринадцатой, четырнадцатой и пятнадцатой ячеек первого столбца матрицы, выход четвертого разряда четвертого дополнительного регистра множителя подключен к информационному входу пятого дополнительного регистра множителя, выход пятого дополнительного регистра множителя подключен к входу множителя шестнадцатой ячейки первого столбца матрицы, выходы частичной суммы первых трех ячеек первого столбца матрицы подключены к входам соответству- юищх разрядов первого дополнительного регистра результата, выходы разрядов первого регистра результата подключены к входам первых трех разрядов второго дополнительного регистра результата, выходы частичной суммы ячеек с четвертой по шестую первого столбца матрицы подключены к входам разрядов соответственно с четвертого по шестой второго дополнительного регистра результата,выходы разрядов второго дополнительного регистра результата подключены к входам соответственно первых шести разрядов третье

го дополнительного регистра результата, выходы частичной суммы ячеек с седьмой по девятую первого столбца матрицы подключены соответственно к входам разрядов с седьмого по девя- тый третьего дополнительного регистра результата, выходы разрядов третьего дополнительного регистра резултата подключены соответственно к входам первьгх девяти разрядов четвертог дополнительного регистра результата, выходы частичной суммы ячеек с десятой по двенадцатую первого столбца матрицы подключены к входам разрядов соответственно с десятого по двенадцатый четвертого дополнительного регистра результата, вьмоды разрядов четвертого дополнительного регистра результата подключены к входам разрядов соответственно с первого по двенадцатый пятого дополнительного регистра результата, выходы частичной суммы ячеек с тринадцатой по пятнадцатую первого столбца матрицы подключены к входам разрядов соответственно с тринадцатого по пятнадцатый пятого дополнительного регистра результата, выходы разрядов пятого дополнительного регистра результата подключены к входам первых пятнадцати разрядов шестого дополнительного регистра результата, выходы частичных сумм ячеек с первой по девятую шестнадцатой строки матрицы подключены к входам разрядов соот- ветственно с шестнадцатого по двадцать четвертый шестого дополнительного регистра результата, ыходы разрядов шестого дополнительного регистра результата подключены к входам соответственно первьпс двадцати четырех разрядов регистра результата, входы синхронизации всех регистров и триггеров устройства объединены между собой и являются входной шиной тактовых импульсов устройства, выход множителя и выход переноса j-и ячейки (,...,8) первой строки матрицы подключены соответственно к входу множителя и к входу переноса (з-н1)-й ячейки первой строки матрицы, выход множителя и выход переноса К-й ячейки (,,..,5) второй строки матрицы подключены соответственно к входам множителя и переноса (К+О-й ячейки второй строки матрицы, выход множителя и выход переноса t-й ячейки (,2) третьей строки «атрицы

O

0

5

5 -35.

30

40

50

55

подключены соответственно к входу множителя и входу переноса ()-й ячейки третьей строки матрицы, выходы множителя и переноса девятой ячейки первой строки матрицы, шестой ячейки второй строки матрицы и третьей ячейки третьей строки матрицы подключены соответственно к информационным входам первого, второго, восьмого, девятого, пятнадцатого и шестнадцатого триггеров первой группы, выходы множимого первых шести ячеек первой строки матрицы подключены к входам множимого соответствующих первых шести ячеек второй строки матрицы, выходы множимого первых трех ячеек второй строки матрицы подключены к входам множимого соответственно первых трех ячеек третьей строки матрицы, выходы множимого седьмой, восьмой и девятой ячеек первой строки матрицы, четвертой, пятой и шестой ячеек второй строки матрицы и первой, второй и третьей ячеек третьей строки матрицы подключены соответственно к информационным входам седьмого, пятого, третьего, четырнадцатого, двенадцатого, десятого, двадцать первого, девятнадцатого и семнадцатого триггеров первой группы, выходы частичной суммы ячеек с второй по седьмую первой строки матрицы подключены к входам частичной суммы ячеек соответственно с первой по шестую второй строки матрицы, выходы частичной суммы ячеек с второй по четвертую второй строки матрицы подключены к входам частичной суммы ячеек соответственно с первой по третью второй строки матрицы, выходы частичной суммы восьмой и девятой ячеек первой строки матрицы, пятой и шестой ячеек второй строки матрицы и второй и третьей ячеек третьей строки матрицы подключены соответственно к информационным входам шестого, четвертого, тринадцатого, одиннадцатого, двадцатого и восемнадцатого триггеров первой группы, входы множителя и переноса десятой ячейки первой строки матрицы, седьмой ячейки второй строки матрицы и четвертой ячейки третьей строки матрицы подключены соответственно к выходам первого, второго, восьмого, девятого, пятнадцатого и шестнадцатого триггеров первой группы, входы множимого седьмой, восьмой и девятой ячеек второй

строки матрицы, четвертой, пятой и шестой ячеек третьей строки матрицы, первой, второй и третьей ячеек четвертой строки матрицы подключены соответственно к выходам седьмого, пятого, третьего, четырнадцатого, двенадцатого, десятого, двадцать первого, девятнадцатого и семнадцатого триггеров первой группы, входы частичных сумм седьмой и восьмой ячеек второй строки, четвертой и пятой ячеек третьей строки и первой и второй ячеек четвертой строки матрицы подключены к выходам соответственно шестого, четвертого, тринадцатого, одиннадцатого, двадцатого и восемнадцатого триггеров первой группы, информационные входы первого, четвертого, одиннадцатого, восемнадцатого, двадцать пятого, тридцать второго триггеров а-й группы (,...,5 подключены к выходам переноса соответственно шестнадцатой ячейки (За- 5)-и строки матрицы, пятнадцатой ячейки (За-4)-й строки матрицы, двенадцатой ячейки (За-З)-й строки матрицы девятой ячейки (За-2)-й строки матрицы

и третьей ячейки За-й строки матрицы, информационные входы третьего, десятого, семнадцатого, двадцать четвертого и тридцать первого триггеров а-й группы подключены к выходам множителя соответственно пятнадцатой ячейки (За-4)-й строки матрицы, двенадцатой ячейки (За-З)-й строки, девятой ячейки (За-2)-й строки матрицы шестой ячейки (За-1)-й строки и третьей ячейки (За)-и строки матрицы, информационные входы второго, пятого седьмого,девятого,двенадцатого,че- тьфнадцатого,шестнадцатого,девятнадцатого,двадцать первого,двадцать третьего, двадцать шестого,двадцать восьмого ,тридцатого, тридцать третьего,тридцать пятого и тридцать седьмого триггеров а-й группы подключены к выходам множимого соответственно шестнадцатой ячейки (За-5)-й строки матрицы, пятнадцатой, четырнадцатой и тринадцатой ячеек (За-4)-й строки матрицы, двенадцатой, одиннадцатой и десятой ячеек (За-З)-й строки матрицы, девятой, восьмой и седьмой ячеек (За-2)-й строки матрицы, шесто пятой и четвертой ячеек (За-1)-й строки матрицы, третьей, второй и первой ячеек За-й строки матрицы, информационные входы шестого, восьмого

O

15

0

5

0

5

0

5

0

5

тринадцатого, пятнадцатого, двадца- то.го, двадцать второго, двадцать седьмого, двадцать девятого, тридцать четвертого и тридцать шестого триггеров а-й группы подключены к выходам частичньсх сумм соответственно пятнадцатой и четырнадцатой ячеек (За-4)-й строки матрицы, двенадцатой и одиннадцатой ячеек (За-З)-й строки матрицы, девятой и восьмой ячеек (За- 2)-и строки матрицы, шестой и пятой ячеек (За-1)-й строки матрицы, третьей и второй ячеек За-й строки матрицы , выходы первого, шестого, восьмого, тринадцатого, пятнадцатого, двадцатого, двадцать второго, двадцать седьмого, двадцать девятого, тридцать четвертого и тридцать шестого триггеров а-й группы подключены к входам частичных сумм соответственно шестнадцатой ячейки (За-4)-й строки матрицы, четырнадцатой и тринадцатой ячеек (За-З)-й строки матрицы, одиннадцатой и десятой ячеек (За-2)-й строки матрицы, восьмой и седьмой ячеек (За-1)-й строки матрицы, пятой и четвертой ячеек (За)-и строки и второй и первой ячеек (За+1)-й строки матриць, выходы второго, пятого, седьмого, девятого, двенадцатого, четьфнадцатого, шестнадцатого, девятнадцатого, двадцать первого, двадцать третьего, двадцать шестого,двадцать восьмого, тридцатого, тридцать третьего, тридцать пятого и тридцать седьмого триггеров а-й группы подключены к входам множимого соответственно шестнадцатой ячейки (За-4)-и строки матрицы, пятнадцатой, четьф- надцатой и тринадцатой ячеек (За-З)-й строки матрицы, двенадцатой, одиннадцатой и десятой ячеек (За-2)-й строки матрицы, девятой, восьмой и седьмой ячеек (За-1)-й строки матрицы, шестой, пятой и четвертой ячеек (За)-и строки матрицы и третьей,второй и первой ячеек (За-1-1)-й строки матрицы, выходы третьего десятого, семнадцатого, двадцать четвертого и тридцать первого триггеров а-й группы подключены к входам множителя соответственно шестнадцатой ячейки ,(За-4)-и строки матрицы, тринадцатой ячейки (За-З)-й строки матрицы, десятой ячейки (За-2)-й строки, седьмой ячейки (За-1)-й строки матрицы и четвертой ячейки За-й строки матрицы, выходы четвертого, одиннадцатого, во9129197010

семнадцатого, двадцать .пятого и,ля и переноса (e+1)-ii ячейки (3b-i-2)-vi тридцать второго триггеров а-й груп-строки матрицы, выход частичной пы подключены к входам переносовсуммы (d-3)й ячейки (ЗЬ+2)-й стро- соо ветственно шестнадцатой ячейкики матрицы подключен к входу частич- (За-4)-й строки матрицы, тринадцатой 5иой суммы (d- l)-й ячейки (ЗЬ+3)-й ячейки (За-З)-й строки матрицы, деся-строки матрицы, выход множимого той ячейки (За-2)-й строки, седьмой()-й ячейки (ЗЬ+2)-й строки матри- ячейки (За-1)-й строки матрицы и подключен к входу множимого (С-З)-й вертой ячейки За-й строки матрицы,ячейки (ЗЬ+3)-й строки матрицы, вы- вьпсод переноса шестнадцатой ячейкиходы множителя и переноса (е-З)-й (ЗЬ-1)-й строки (,2,3) подключенячейки (ЗЬ+3)-й строки матрицы под- к входу частичной суммы шестнадца-ключены к входам множителя и переноса той ячейки ЗЬ-й строки матрицы, вы-(е-2)-й- ячейки (ЗЬ+3)-й строки матри- ход частичной суммы шестнадцатойцы, выход частичной суммы {ё-6)-й ячейки (ЗЬ-1)-й строки матрицы под- ячейки (ЗЬ+3)-й строки матрицы под- . ключен к входу частичной суммы пят-ключен к входу частичной суммы (d- надцатой ячейки ЗЪ-й строки матрицы,-7)-й ячейки (ЗЬ+4)-и строки матрицы, выход множимого шестнадцатой ячейкивыход множимого (С-б)-й ячейки (ЗЬ-1)-й строки матрицы подключен к( строки матрицы подключен к входу множимого шестнадцатой ячейки входу множимого (С-б)-й ячейки ЗЬ-й строки матрицы, выходы множите-(ЗЬ+4)-и строки матрицы, выходы мно- ля и переноса тринадцатой, четырнад-жителя и переноса (е-б)-й ячейки цатой и пятнадцатой ячеек ЗЬ-й стро-(ЗЬ+4)-й строки матрицы подключены ки матрицы подключены к входам множи-к входам множителя и переноса (е-5)-й теля и переноса соответственно четыр-ячейки (ЗЬ+4)-и строки матрицы, вы- надцатой, пятнадцатой и шестнадцатойход множимого (С-9)-й ячейки (ЗЬ+ ячеек ЗЬ-й строки матрицы, выход пе-+4)-и строки подключен к входу мно- шестнадцатой ячейки ЗЬ-й стро-жимого (С-9)-й ячейки (ЗЬ+5)-й строки матрицы подключен к входу частич-ки матрицы, выход частичной суммы ной суммы шестнадцатой ячейки (ЗЬ+ f-й (,...,7) ячейки (ЗЬ+4)-й стро- +1)-й строки матрицы, выходы частич-ки подключен к входу частичной суммы ной суммь: тринадцатой, четырнадцатой,(-1)-й ячейки (ЗЬ+5)-й строки мат- пятнадцатой и шестнадцатой ячеекрицы, выходы множителя и переноса ЗЬ-й строки матрицы подключены к вхо- . (,...,5) ячейки (ЗЫ-5)-й дам частичной суммы соответственно 35 строки матрицы подключены к вхо- двенадцатой, тринадцатой, четырнад-дам множителя и переноса (g+1)-й цатой и пятнадцатой ячеек (ЗЬ+1)-йячейки (ЗЬ+5)-й строки матрицы, строки матрицы, выходы множимого три-выходы частичной суммы второй, надцатой, четырнадцатой, пятнадцатойтретьей и четвертой ячеек (ЗЬ+5)-й и шестнадцатой ячеек ЗЬ-й строки мат- строки матрицы подключены к вхо- рицы подключены к входам множимо го со-ДУ частичной суммы соответствен- ответственно тринадцатой,четырнадца-но первой, второй и третьей ячеек той,пятнадцатой и шестнадцатой ячеек(ЗЬ+6)-й строчки матрицы, выходы мно- (ЗЬ+1)-и строки матрицы,выходы множите-жимого первой, второй и третьей яче- ля и переноса С-й (С 10,11, , .., 1 5)ячей- ек (ЗЬ+5)-й строки матрицы подклю- ки (ЗЬ+1)-и строки матрицы,подключе-чены к входам множимого соответственны к входам множителя и переноса (С+но первой, второй и третьей ячеек ;+1)-й ячейки (ЗЬ + 1)-й строки матрицы,(ЗЬ+6)-й матрицы, выходы множителя и выход частичной суммы d-й ячейкипереноса С-й ячейки первой строки - (,..., 16) (З.Ь+1)-й строки матрицы- матрицы подключены к входам множите- подключен к входу частичной суммыля и переноса (С+1)-й ячейки (ЗЬ+ (d-1)-й ячейки (ЗЬ+2)-й строки матри-+1)-й строки матрицы, выход частичной цы,выход множимого С-й ячейки (ЗЬ+1)-исуммы d-й ячейки первой строки матри- строки матрицы подключен к входуЦЫ подключен к входу частичной сум- ножимого С-й ячейки (ЗЬ+2)-й строки мы (d-1)-й ячейки второй строки мат- матрицы, выходы множителя и переноса)ицы, выход множимого С-й ячейки пер- е-й (,...,14) ячейки (ЗЬ+2)-й стро-вой строки матрицы подключен к входу, ки матрицы подключены к входам множите-множимого С-й ячейки второй строки

матрицы, выход переноса е-й ячейки второй строки матрицы подключен к входу переноса (е+1)-й ячейки второй строки матрицы, выход множителя е-й ячейки второй строки матрицы под ключей к входу множителя е+1)-й ячейки второй строки матрицы, выход частичной суммы (d-3)-и ячейки второ строки матрицы подключен к входу частичной суммы (d-4)-й ячейки третьей строки матрицы, выход множимого (С- -3)-й ячейки второй строки матрицы подключен к входу множимого (С-З)-й ячейки третьей строки матрицы, выходы множителя и переноса (е-З)-й ячейки третьей строки матрицы подключены к входам множителя и переноса (е-2)-й ячейки третьей строки матрицы, выход частичной суммы (d- -6)-й ячейки третьей строки матрицы подключен к входу частичной суммы (d-7)-й ячейки четвертой строки матрицы, выход множимого (С-б)-й ячейки третьей строки матрицы подключен к входу множимого (С-б)-й ячейки четвертой строки матрицы, выходы множителя и переноса (е-б)-й ячейки четвертой строки матрицы подключен к входам множителя и переноса (е-5)ячейки четвертой строки матрицы, выход множимого (С-9)-й ячейки четвертой строки матрицы подключен к входу множимого (С-9)-й ячейки пятой строки матрицы, выход частичной СУММЫ -й ячейки четвертой строки подключен к входу частичной суммы (-1)-й ячейки пятой строки матрицы, выходы множителя и переноса g-й ячейки пятой строки подключены к входам множителя и переноса (g+ +1)-й ячейки пятой строки матрицы, выходы частичной суммы второй, третьей и четвертой ячеек пятой строки. матрицы подключен к входам частичной суммы соответственно первой, второй и третьей ячеек шестой строки матрицы, выходы множимого первой, второй и третьей ячеек пятой строки матрицы подключены к входам множимого соответственно первой, второй и третьей ячеек шестой строки матрицы, выход переноса шестнадцатой ячейки одиннадцатой строки матрицы подключен к входу частичной суммы шестнадцатой ячейки двенадцатой строки мат рицы, выход частичной суммы шестнадцатой ячейки одиннадцатой строки матрицы подключен к входу частичной сум

-

t5

- 5 й -й30

40

45

50

55

мы пятнадцатой ячейки двенадцатой строки матрицы, выход множимого шестнадцатой ячейки одиннадцатой строки матрицы подключен к входу множимого шестнадцатой ячейки двенадцатой строки матрицы, выходы множителя и переноса тринадцатой, четырнадцатой и пятнадцатой ячеек двенадцатой строки матрицы подключены к входам множителя и переноса соответственно четырнадцатой, пятнадцатой и шестнадцатой ячеек двенадцатой строки матрицы, выход переноса шестнадцатой я 1ейки двенадцатой строки матрицы подключен к входу частичной суммы шестнадцатой ячейки тринадцатой строки матрицы, выходы частичной суммы тринадцатой, четьфнадцатой, пятнадцатой и шестнадцатой ячеек двенадцатой строки матрицы подключены к входам частичной суммы соответственно двенадцатой, тринадцатой, .четыр-. надцатой и пятнадцатой ячеек, тринадцатой строки матрицы, выходы множимого тринадцатой, четьфнадцатой, пятнадцатой и шестнадцатой ячеек двенадцатой строки матрицы подключены к входам множимого соответственно тринадцатой, четырнадцатой, пятнадцатой и шестнадцатой ячеек тринадцатой строки матрицы, выходы множителя и переноса С-й ячейки тринадцатой строки матрицы подключены к входам множителя и переноса (С+1)-й ячейки , тринадцатой строки матрицы, выход частичной суммы d-й ячейки тринадцатой строки подключен к входу частичной суммы (ё-1)-й ячейки четырнадцатой строки матрицы, выход множимого С-й ячейки тринадцатой строки матрицы подключен к входу множимого С-й ячейки четырнадцатой строки матрицы, выходы множителя и переноса е-й ячейки четырнадцатой строки матрицы подключены к входам множителя и переноса (е+1)-й ячейки четырнадцатой строки матрицы, выход частичной суммы (d-3)-и ячейки четьфнадцатой строки матрицы подключен к входу частичной суммы (d-4)-й ячейки пятнадцатой строки матрицы, выход множимого (е-З)-й ячейки четьфнадцатой строки матрицы подключен к входу множимого (С-З)-й ячейки пятнадцатой строки матрицы, выходы множителя и переноса (е-З)-й ячейки пятнадцатой строки матрицы подключены к входам множителя и переноса (е-2)-и ячейки пятнадцатой строки матрицы, выход частичной суммы (б-б)-й ячейки пятнадцатой строки матрицы подключен к входу частичной суммы (ё-7)-й ячейки шестнадцатой строки матрицы, выход мно- ,жимого (С-б)-й ячейки пятнадцатой строки матрицы подключен к входу множимого (С-б)-й ячейки шестнадцатой строки матрицы, выходы множителя и переноса (е-б)-й ячейки шестнадцатой строки матрицы подключены к входам множителя и переноса (е-5)-и ячейки шестнадцатой строки матрицы, выход переноса шестнадцатой ячейки четьфнадцатой строки матрицы подклю- чен к входу частичной суммы пятнадцатой ячейки пятнадцатой строки матрицы, выход множимого шестнадцатой ячейки четырнадцатой строки матрицы подключен к входу множимого шестнадцатой ячейки пятнадцатой строки матрицы, выходы множителя и переноса тринадцатой, четырнадцатой и пятнадцатой ячеек пятнадцатой строки матрицы подключены к входам множителя и переноса соответственно четырнадцатой, пятнадцатой и шестнадцатой ячеек пятнадцатой строки матрицы, выход переноса шестнадцатой ячейки пятнадцатой строки матрицы подключен к входу частичной суммы шестнадцатой ячейки шестнадцатой строки матрицы, выходы частичной суммы тринадцатой, четьфнадцатой, пятнадцатой и шестнадцатой ячеек пятнадцатой строки матрицы подключены к входам частичной суммы соответствено двенадцатой, тринадцатой, четырнадцатой и пятнадцатой ячеек шестнадцатой строки матрицы, выходы множимого тринадцатой, четьфнадцатой, пятнадцатой и шестнадцатой ячеек пятнадцатой строки матрицы подключены к входам множимого соответственно тринадцатой, четырнадцатой, пятнадцатой и шестнадцатой ячеек шестнадцатой строки матрицы, выходы множителя и переноса С-й ячейки шестнадцатой строки матрицы подключены к входам множителя и переноса (С+1)-й ячейки шестнадцатой строки матрицы, выходы переносов шестнадцатой ячейки тринадцатой строки матрицы, пятнадцатой ячейки четьфнадцатой строки матрицы, двенадцатой ячейки четырнадцатой строки матрицы и девятой ячейки шестнадцатой строки матрицы подключены к информационным входам со0

5

0

5

0

5

0

45

50

55

ответственно первого, четосртого, одиниадцатог о и поссмяадцатого триггеров шестой группы, выход(1 множимого шестнадцатой ячейки тринадцатой строки матрицы, пятнадцатой, четьфнадцатой и тринадцатой ячеек четырнадцатой строки матрицы, двенадцатой, одиннадцатой и десятой ячеек пятнадцатой строки матрицы подключены к информационным входам соответственно второго, пятого, седьмого, девятого, двенадцатого, четырнадцатого и шестнадцатого триггеров шестой группы, выходы множителя пятнадцатой ячейки четьфнадцатой строки матрицы, двенадцатой ячейки пятнадцатой строки матрицы и девятой ячейки шестнадцатой строки матрицы подключены к информационным входам соответственно третьего, десятого и семнадцатого триггеров шестой группы, выходы частичной суммы пятнадцатой и четырнадцатой ячеек четырнадцатой строки матрицы, двенадцатой и одиннадцатой ячеек пятнадцатой строки матрицы подключены к информационным входам соответственно шестого, восьмого, тринадцатого и пятнадцатого триггеров шестой группы, входы частичняй суммы шестнадцатой ячейки четьфнадцатой строки матрицы, четьфнадцатой и тринадцатой ячеек пятнадцатой строки матрицы, одиннадцатой и десятой ячеек шестнадцатой строки матрицы подключены к выходам соответственно первого, шестого,восьмого, тринадцатого и пятнадцатого триггеров шестой группы, входы множимого шестнадцатой ячейки четьфнадцатой строки матрицы, пятнадцатой, четьфнадцатой и тринадцатой ячеек пятнадцатой строки матрицы, двенадцатой, одинна цатой и десятой ячеек шестнадцатой строки матрицы подключены соответственно к выходам второго, пятого, седьмого, девятого, двенадцатого, четьфнадцатого и шестнадцатого триггеров шестой группы, входы множителя шестнадцатой ячейки четырнадцатой строки матрицы, тринадцатой ячейки пятнадцатой строки матрицы и десятой ячейки шестнадцатой строки матрицы подключены к выходам соответственно третьего, десятого и семнадцатого триггеров шестой группы, входы переносов шестнадцатой ячейки четьфнадцатой строки. матрицы, тринадцатой ячейки пятнадцатой строки матрицы и десятой ячей15 129197016

ки шестнадцатой строки матрицы под- вертого, одиннадцатого и восемнадца- ключены к выходам соответственно чет- того триггеров шестой группы,

в б

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Конвейерное операционное устройство | 1985 |

|

SU1254470A1 |

| Устройство для деления 48-разрядных чисел | 1984 |

|

SU1239712A1 |

| Устройство для умножения чисел | 1990 |

|

SU1741129A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧИСЕЛ | 1971 |

|

SU290278A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU669352A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении высокопроизводительных процессоров цифровых вычислительных машин. Цель изобретения - повышение производительности устройства. Устройство содержит регистр множимого, регистр результата и ромбовидную матрицу ячеек, причем каждая ячейка содержит полный сумматор и элемент И. Новым является введение триггеров для запоминания промежуточных результатов. Нестандартная расстановка триггеров - не в горизонтальном направленин а по диагонали - и разбивка поля матрицы на ряд слоев комбинационных схем приводят к повышению производительности обработки Данных.2 ил. (Л с tsD СО со

Редактор Н. Рогулич

Составитель С. Силаев Техред В.Кадар

Заказ 265/47Тираж 673

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиъ2

Корректор. Н. Король

Подписное

| Конвейерное множительное устройство | 1980 |

|

SU903866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Макаревич О.Б | |||

| ,Спиридонов Б.Г | |||

| Цифровые процессоры обработки сигналов на основе БИС | |||

| - Зарубежная электронная техника, 1983, № 1, с.38-62, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-02-23—Публикация

1984-06-21—Подача