(54) АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная запоминающая матрица | 1979 |

|

SU886051A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU881861A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU924754A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Накопитель для ассоциативного запоминающего устройства | 1982 |

|

SU1023396A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

Изобретение относится к области запоминающих устройств и можег быть иопольаовано в качестве ассоциативного пО пя в ассоциативных процессорах.

Известны ассоциативные запоминающие матрицы.

Первая иа известных матриц содержит ячейки памяти, выполненные на МДП транзисторах и содержащие триггеры, элементы записи, считывания, сравнения Т Недостатком этого устройства являются большие аппаратурные затраты.

Из известных устройств наиболее бпи КИМ техническим решением к данному изс бретению является ассоциативная запоминающая матрица, содержащая элементы памяти, каждый иа которых выполнен из триггера, подключенного к элементам сравнения, илходы которых соединены со ответственно с шинами результата опро са, шины разрешения записи по строке и по столбцу, информационные шины опроса

Однако, во-первых, эта матрица имеет

информационные шины для задания как кйда опроса, так и кода записи, хотя при обработке информации в ассоциативном поле значение записи всегда является инверсным по отношению к значению опроса; во-вторых, ассацяативное..поле, составленное с использованием известной матрицы, имеет два канала считывания: один - для последовательного считывания слов параллельно по , другой для параллельного считывания массивов

последовательно по разрядам, хотя при использовании ассоциативной памяти в к гчестве решающего поля процессора испол гзование последовательного по словам вы- вода массивов нецелесообразно, так как при больших массввах он значительно замедпяет процесс обработки данных и, тем самым снижает эффективность использования ассоциативного поля.

Большое количество шии существенно услсоКняет матрицу, снижает уровень интеграции (количество ячеек памяти в корпусе) и надежность матрицы,

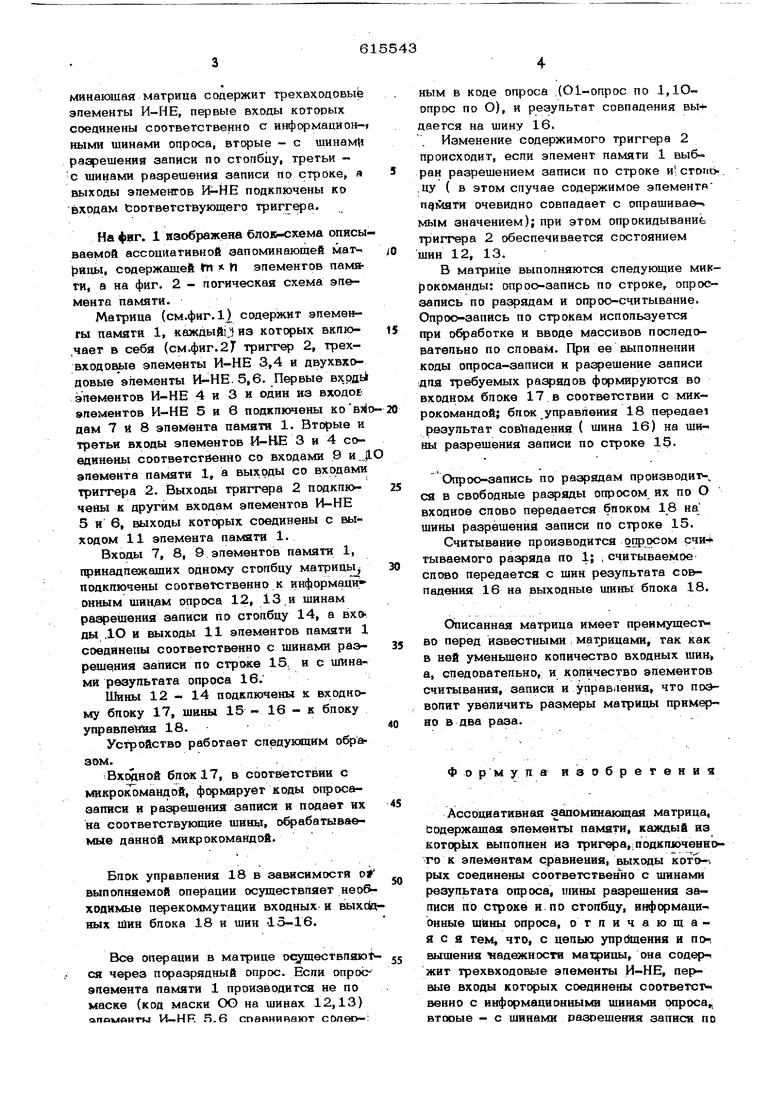

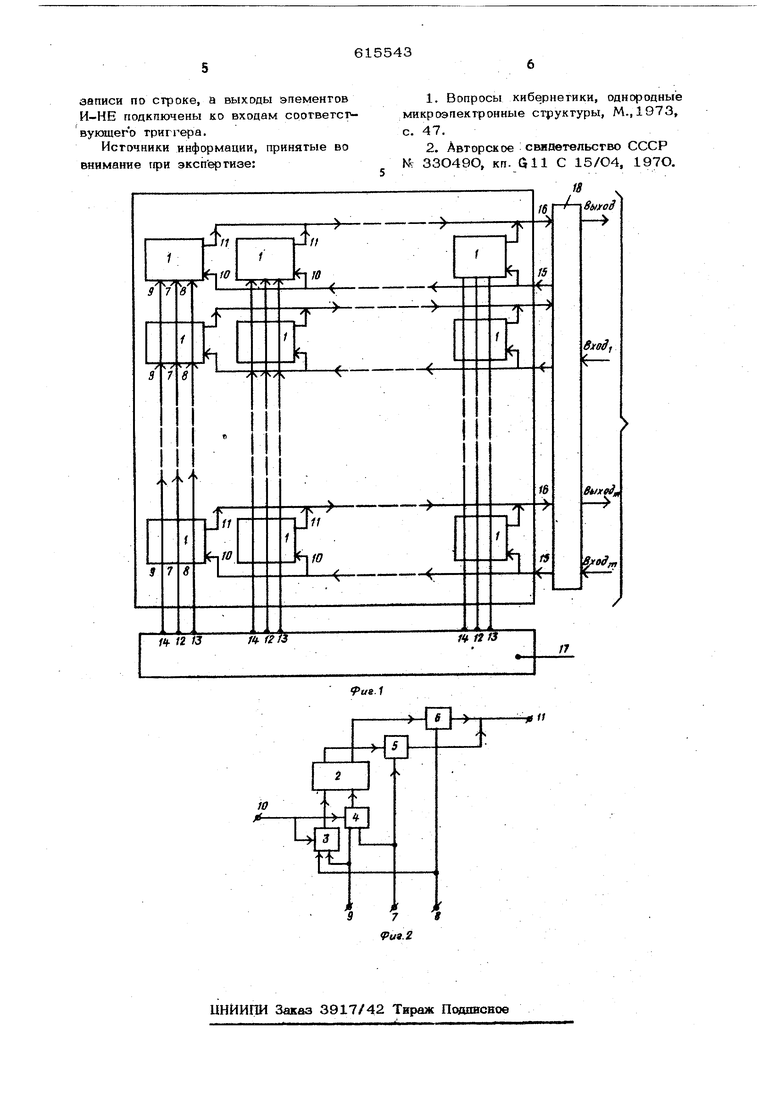

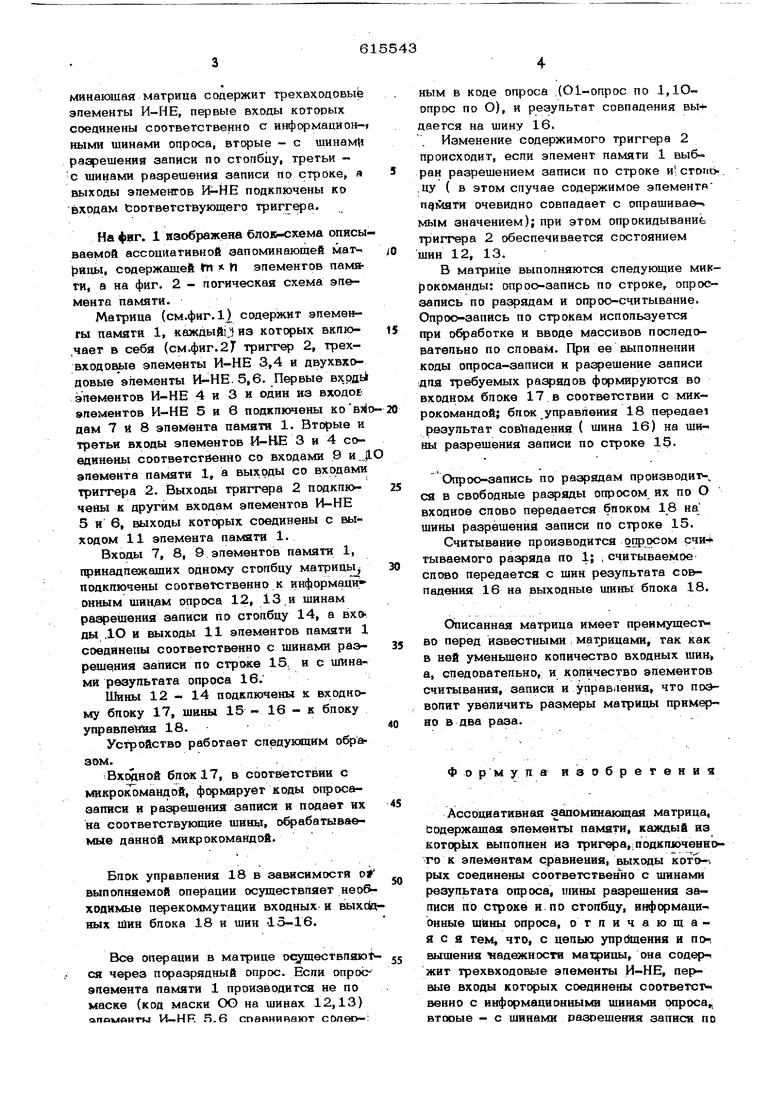

С целью улрсяценяя и повышения иадежВОСГ8 предпагаемав ассооватвввая эапоминающая матрица содержит трехвхоцовые эпементы И-НЕ, первые входы которых соединены соответственно с информацион- ными шинами опроса, вторые - с шинам разрешения записи по столбцу, третьи с шинами разрешения записи по строке, я выходы эпеменгов И-НЕ подкпючены ко Ьходам Соответствующего триггера. На фиг. 1 изображена бпок-схема описы ваемой ассоциативной запоминающей , содержащей fn П элементов памяти, а на фиг. 2 - логическая схема эпемента памяти. Матрица (см.фиг.1| содержит эпеменгы памяти 1, каждыйг;} из которых вкпкн,чаег в себя {см.фиг.2Т триггер 2, трехвходовьш эпементы И-НЕ 3.4 и двухвходовые эпементы И-НВ. 5,6. Первые вхрдь эпвментов И-НЕ 4 и 3 и один из входоЕ эпементов И-НЕ бив подкпючены ко дам 7 и 8 эпемента памяти 1. и третьи входы эпементов И-НЕ 3 и 4 соединеиы соответстйенио со входами 9 и.Д эпемента памяти 1, а выходы со входами триггера 2. Выходы триггера 2 подкпючаны к другим входам апементов И-НЕ 5 и 6, выходы которых соединены с выходом 11 эпемента памяти 1. Входы 7, 8, 9 эпементов памяти 1, принадлежащих одному столбцу матриЦ5л подключены соответственно к информации онным шинэм опроса 12, 13 и шинам разрешения записи по столбцу 14, а вх ды .Ю и выходы 11 элементов памяти 1 соединены соответственно с шинами разрешения записи по строке 15, и с шг1на-. ми результата опроса 16. Шины 12-14 подкпючены к входнсхму блоку 17, шины 15 - 16 - к блоку управления 18. Устройство работает следуклцим образом. Входной блок 17, в соответствии с микрокомандой, формирует коды опросазаписи и разрешения записи и подает их на соответствующие шины, обрабатываемые данной микрокомандой. Блок управления 18 в зависимости of выполняемой операции осуществляет необходимые перекоммутации входных и выхсЬ ных 1йин блока 18 и шин -15-16. Все операции в матрице осуществляю ся через поразрядный опрос. Если опроЬ элемента памяти 1 производится не по маске (код маски ОО на шинах 12,13) anovfOHTM И-HR 5.6 спавнивают ным в коде опроса .(О1-опрос по 1,1Оопрос по О), и результат совпадения вы- дается на шину 16. Изменение содержимого триггера 2 происходит, еспи элемент памяти 1 выб-« ран разрешением записи по строке истоиь-. ,цу ( в этом случае содержимое элемента п 1йяти очевидно совпадает с опрашива& мым значением); при этом опрокидываний триггера 2 обеспечивается состоянием шин 12, 13. В матрице выполняются следующие микрокоманды: опроо-запись по строке, опросзапись по разрядам и опрос-считывание. Опроо-запись по строкам используется при обработке и вводе массивов последовательно по словам. При ее выполнении коды опроса-записи н разрешение записи для требуемых разрядов формируются во входном блоке 17 в соответствии с микрокомандой; блок управления 18 передае результат совУгадения ( шина 16) на шины разрешения записи по строке 15Опроо-запись по разрядам пpoизвoдиtv. ся в свободные разряды опросом их по О входное слово передается блоком 18 на шины разрешения записи по строке 15. Считывание производится опросом счи- тываемого разряда по 1; .считываемое слово передается с шин результата совпадения 16 на выходные шины блока 18. Описанная матрица имеет преимущестм во перед известными , матрицами, так как в ней уменьшено количество входных шин, а, следовательно, и количество элементов считывания, записи и управления, что позволит увеличить размеры матрицы примерно в два раза. Формула изобретения Ассоциативная запоминающая матрица, Содержащая элементы памяти, каждый из которых выполнен из тригера,:подключенв{ го к элементам сравнения, выходы рых соединены соответственно с шинами результата опроса, шины разрешения записи по строке и по столбцу, информационные шины опроса, отличающаяся тем, что, с целью упр()щения н пен вышекия « ад ности мацэицы, она содерч жит трехвходовые элементы И-НЕ, первыв входы которых соединены соответственно с информационными шинами оароса„ втооые - с шинами разрешения записи по записи по строке, а выходы эпеменгов И-НЕ подкпючены ко входам соогвегсгвующего триггера. Источники информации, принятые во

внимание гфи экспертизе:

№ ЗЗО49О, кп. G11 С 15/О4, 197О, 1, Вопросы кибернетики, однородные микроэпектронные структуры, М.,1973, с. 47. 2. Авторское свидетвльсгво СССР

Авторы

Даты

1978-07-15—Публикация

1976-08-27—Подача