Изобретение относится к технике электросвязи и может быть использова но в многоканальных системах с временным разделением каналов. По основному авт.св. № 748896 известно устройство для асинхронного сопряжения каналов связи, содержащее на передающей стороне последовательно соединенные блок фазовой автоподстройки частоты (ФАПЧ) блок памяти, фаговый дискриминатор и блок управления, причем на вход блока (ФАП и на второй вход блока памяти подан абонентский сигнал, на третий вход блока памяти поданы считывающие импульсы, а четвертый вход блока памя ти соединен с первым выходом блока управления, второй выход блока памя ти подключен к основному каналу свя зи, а второй выход блока управления - к .дополнительномуканалу связи, и на приемной стороне последовательно соединенные дешифратор команд блок памяти и фазовый дискриминатор при этом вход дешифратора команд соединен с дополнительным каиалом связи, второй вход блока памяти сое динен с основным каналом связи, на третий вход блока памяти поданы импульсы записи, к четвертому входу подключен выход блока формирования частоты считывания, а выход блока памяти является выходом устройства, :а также последовательно соединенные синтезатор сигналов низких частот и блок управления скоростью считывания выход которого подключен к входу бло ка формирования частоты считывания, причем второй вход блока управления скоростью считывания соединен с первым выходом блока памяти, третий вход соединен с выходом фазового дискриминатора, выход блока формирования частоты считывания подключен к четвертому входу блока памяти, а на вход синтезатора сигналов низких частот поданы управляющие сигналы l Однако в известном устройстве расширение диапазона нестабильности частоты абонентов приводит к увеличению фазовых флуктуации выходного сигнала,, Цель изобретения - уменьшение низкочастотных флуктуации выходного сигнала в широком диапазоне нестабильности частоты абонентов. Эта цель достигается тем, что в устройство для асинхронного сопряжения каналов связи, содержащее на передающей стороне последовательно соединенные блок (ФАПЧ), блок памяти, фазовый дискриминатор и блок управления, причем на вход блока (ФАПЧ) и на второй вход блока памяти подан абонентский сигнал, на третий вход блока памяти поданы считывающие импульсы, а четвертый вход блока памяти соединен с первым выходом блока управления, второй выход блока памяти подключен к основному каналу связи, а второй выход блока управления - к дополнительному каналу связи, и на приемной стороне последовательно соединенные дешифратор команд, блок памяти и фазовый дискриминатор, при этом вход дешифратора команд соединен с дополнительным каналом связи, второй вход блока памяти соединен с основ-ным каналом связи, на третий вход блока памяти поданы и 5пyльcы записи, к четвертому входу подключен выход блока формирования частоты считывания, а выход блока памяти является выходом устройства, а также последовательно соединенные синтезатор сигналов низких частот и блок управления скоростью считывания, выход которого подключен к входу блока формирования частоты считывания, причем второй вход блока управления скоростью считывания соединен с первым выходом блока памяти, третий вход соединен с выходом фазового дискриминатора, выход блока формирования частоты считывания подключен к четвертому входу блока памяти, а на вход синтезатора сигнешов низких частот поданы управляющие импульсы, на передающей стороне введены перераспределитель . тактов передачи, блок временного выравнивания тактов и первый блок временного преобразования сигналов, причем выходы перераспредели-; теля тактов передачи подключены соответственно к первому входу первого блока временного преобразования сигналов, к второму входу блока управления и через блок временного выравнивания тактов - к входу считывания блока памяти, выход которого подключен к второму входу первого блока временного преобразования сиг налов, к третьему входу которого подключен второй выход блока управления, а выходы первого блока временного преобразования сигналов являются соответственно входами основного и дополнительного каналов связи, а на приемной стороне вв.едены второй блок временного преобразования сигналов и перераспределитель тактов приема, причем выходы второго блока временного преобразования сигналов подключены соответственно к входу дешифратора команд и к входу записи блока памяти, а выходы перераспределителя тактов приема подключены к соответствующим входам второго блока временного преобразования сигналов, дешифратора команд и блока памяти, входы второго блока временного преобразования сигналов подклюены к выходам основного и дополниельного каналов связи, а входы перераспределителей тактов передачи и приема являются соответственно входами основной и дополнительной последовательности тактовых импульсов.

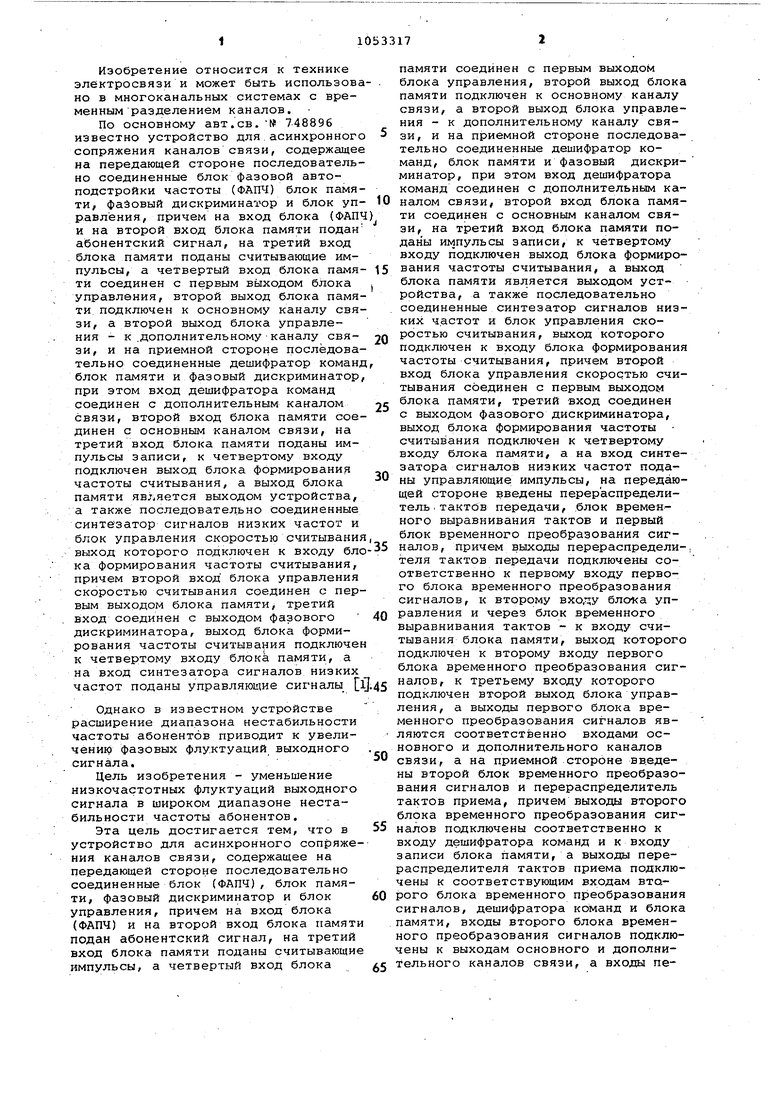

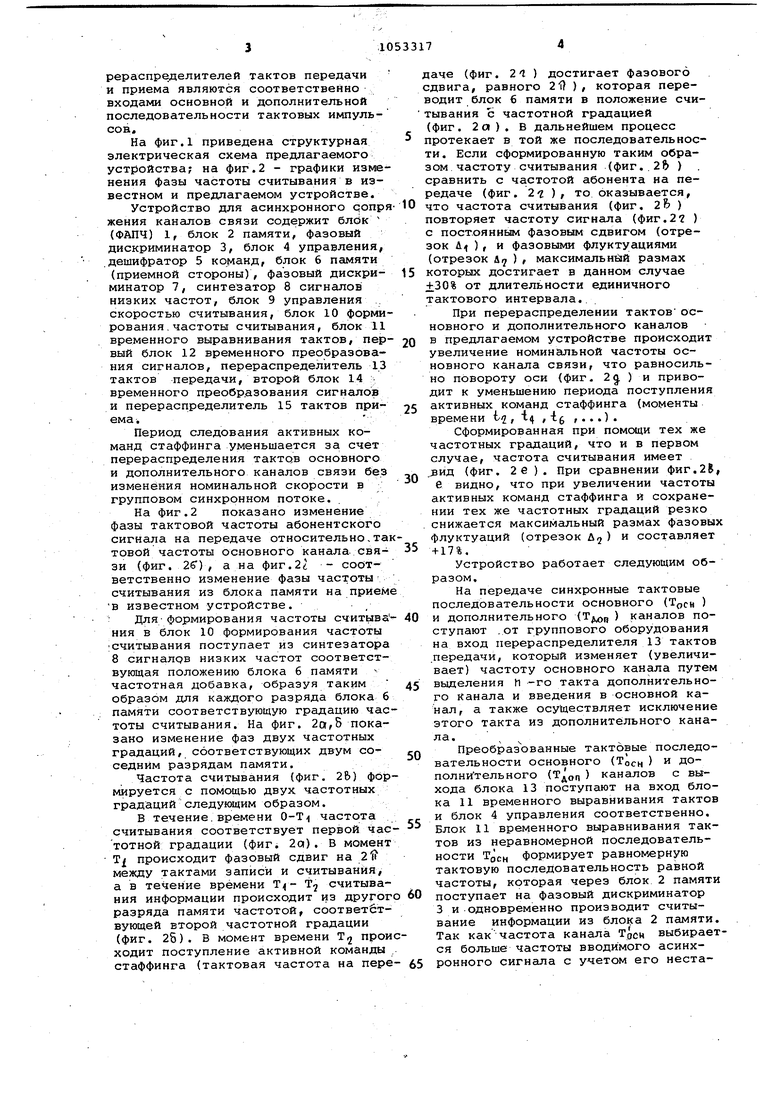

На фиг.1 приведена структурная электрическая схема предлагаемого устройства; на фиг.2 - графики изменения фазы частоты считывания в известном и предлагаемом устройстве.

Устройство для асинхронного с|опряжения каналов связи содержит блок (ФАПЧ) 1, блок 2 памяти, фазовый дискриминатор 3, блок 4 управления,

.дешифратор 5 команд, блок 6 памяти (приемной стороны), фазовый дискриминатор 7, синтезатор 8 сигналов низких частот, блок 9 управления . скоростью считывания, блок 10 формирования, частоты считывания, блокИ временного выравнивания тактов, первый блок 12 временного преобразования сигналов, перераспределитель 13 тактов передачи, второй блок 14 временного преобр.азования сигналов и перераспределитель 15 тактов приема.

Период следования активных команд стаффинга уменьшается за счет перераспределения тактов основного и дополнительного каналов связи без изменения номинальной скорости в групповом синхронном потоке.

На фиг.2 показано изменение фазы тактовой частоты абонентского сигнала на передаче относительно,татовой частоты основного канала связи (фиг. 26) , а на фиг.22 - соответственно изменение фазы частоты считывания из блока памяти на прием

В известном устройстве.

: Для- формирования частоты считывания в блок 10 формирования частоты

считывания поступает из синтезатора 8 сигналрв низких частот соответствующая положению блока 6 памяти частотная добавка, образуя таким образом для каждого разряда блока 6 памяти соответствующую градацию частоты считывания. На фиг. показано изменение фаз двух частотных градаций, соответствующих двум со седним разрядам памяти.

Частота считывания (фиг. 2&) формируется с помощью двух частотных градаций следующим образом.

В течение.времени О-Т частота считывания соответствует первой частотной градации (фиг. 2а). В момент Т| происходит фазовый сдвиг на 21 между тактами записи и считывания, а в течение времени Tj считывания информации происходит из другог разряда памяти частотой, соответбтвующей второй частотной градации (фиг. 25). В момент времени Т проиходит поступление активной команды стаффинга (тактовая частота на передаче (фиг. 21 ) достигает фазового сдвига, равного 21} ), которая переводит блок 6 памяти в положение считывания с частотной градацией (фиг. 2а ). В дальнейшем процесс протекает в той же последовательности. Если сформированную таким образом частоту считывания (ФИГ..2& ) сравнить с частотой абонента на передаче (фиг. 21), то оказывается,

0 что частота считывания (фиг. 2& ) повторяет частоту сигнала (фиг.2 ) с постоянным фазовым сдвигом (отрезок А ), и фазовыми флуктуациями (отрезок д максимальней размах

5 которых достигает в данном случае +30% от длительности единичного тактового интервала..

При перераспределении тактов основного и дополнительного каналов в предлагаемом устройстве происходит

0 увеличение номинЗшьной частоты основного канала связи, что равносильно повороту оси (фиг. 2 ) и приводит к уменьшению периода поступления активных команд стаффинга (моменты

5 времени , ц , i.(, ,,.,,

Сформированная при помощи тех же частотных градаций, что и в первом случае, частота считывания имеет ид (фиг. 26 ). При сравнении фиг.28,

0 е видно, что при увеличении частоты активных команд стаффинга и сохранении тех же частотных градаций резко . снижается максимальный размах фазовых флуктуации (отрезок д) и составляет

5 + 17%,

Устройство работает следующим образом.

На передаче синхронные тактовые последовательности основного ( )

0 и дополнительного ( ) каналов поступают .от группового оборудования на вход перераспределителя 13 тактов .передачи, который изменяет (увеличивает) частоту основного канала путем выделения h -го такта дополнительно5го Канала и введения в основной канал, а также осу1цествляет исключение этого такта из дополнительного канала.

Преобразованные тактовые последо0вательности основного (Тосн ) Д° полнительного (Тдо„ ) каналов с выхода блока 13 поступают на вход блока 11 временного выравнивания тактов и блок 4 управления соответственно.

5 Блок 11 временного выравнивания тактов из неравномерной последовательности TOCH формирует равномерную тактовую последовательность равной частоты, которая через блок 2 памяти

0 поступает на фазовый дискриминатор 3 и одновременно производит считывание информации из блока 2 памяти. Так как частота канала TQCM выбирается больше частоты вводимого асинхронного сигнала с учетом его неста5бильности, то в моменты времени, определяе1уП:«е фазовым дискриминаторо 3, на блок управления выдается сигнал, по которому последний формируе команду Убавить и передает ее по дополнительному каналу, после че го по основному каналу передается балластная посылка,, не несущая инфо мацив. Информация с выхода блока 2 памя ти, считанная с частотой Tflfu , и с выхода бло1):а у правления, считанная частотой Тдоп/ поступают на первый блок временного преобразования сигн лов, который по сигналам от перераспределителя 13 тактов передачи производит исключение ti го бита из основного канала и передачу его по дополнительному каналу, восстанавли вает таким образом информацию основ ного канала в тактах г а дополн тельног.о - в тактах Тдол На приемной стороне синхронные тактовые последовательности основного Т(,„ и дополнительного Тдоц каналов поступают на перераспредёлитель 15 тактов приема, в которо производится, исключение ti -го такта из дополнительного канала и введение его в основной канал, при этом выдается сигнал на второй блок 14 временного преобразования сигналов, по которому последний исключает Я-и бит информации из дополнительно го канала,, поступаквдей на вход дешифратора 5 команд, и производит вставку бита в информацию Основного канала, поступающую на вход блока 6 памяти. Запись информации в блок 6 памяти и дешифратор 5 команд осуществляется преобразованными тактами основного и дополнительного каналов с выхода перераспределителя 15 тактов приема. Дешифратор 5 команд при обнаруже Убавить НИИ команды запрещает запись информации в блок б памяти, который через фазовый дискриминатор 7 выщает сигнал на блок 9 управлени скоростью считывания, который пропускает соответствующую низкочастотную добавку, сформированную синтезатором 8 сигналов низких частот, на блок 10 формирования частоты считывания. При выборе достаточного превышения частоты Тдсн над частотой. Tj,p в устройстве может потребоваться всего две градации частоты на приеме для получения флуктуации, не превышающих требуемую величину, и следовательно, одно значение низкочастотной добавки, подаваемой на вход блока 10 формирования частоты считывания со энав зависимости от знака расхождения фаз, вырабатываемого фазовым дискриминатором 7. График изменения фазы выходного сигнала показан на фиг. 2е . Перераспределитель 13 тактов может быть выполнен в виде счетчика числа П и схем И, ИЛИ, ЗАПРЕТ. При этом каждый И -и такт запрещается в тактовой последовательности Тдоп и добавляется в последовательность , Блок Д1 -временного выравнивания тактов может быть выполнен по классической схеме устройства фазовой подстройки частоты, включающей в себя управля.емый делитель и фазовый . детектор. Блок 12 временного преобразования Сигналов может, быть выполнен в виде триггера привязки и сх&л И, ИЛИ, коммутирующих информацию основного и дополнительного ка«алов. Одно1|менные блоки в приемной части могут быть выполнены аналогично. Предлагаемое устройство, срхра- няя все преимущества основного изобретения, а именно высокую эффективность использования канала связи за счет исключения второго дополнительного канала связи позволяет снизить величину размаха фазовых флуктуации выходного сигнала в широкОм диапазоне нестабильности частоты абонента с одновременным уменьшением числа частотных градаций, при этом уменьшается объем запоминающего устройства и следовательно, уменьшается время вхождения в синхронизм, снижается задержка информации, не происходит усложнения группового сигнала аппаратуры временного уплотнения. Как показали испытания, величина фазовых флуктуации выходного сигнала не превышает 5% для шести асинхронных переприемов и не зависит от текущей нестабильности частоты абонента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для асинхронного сопряжения каналов связи в системах с временным разделением каналов | 1978 |

|

SU949836A2 |

| Устройство для асинхронного сопряжения каналов связи | 1977 |

|

SU748896A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| Устройство асинхронного сопряжения каналов | 1974 |

|

SU496687A1 |

| УСТРОЙСТВО ДЛЯ АСИНХРОННОГО УПЛОТНЕНИЯКАНАЛОВ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМСИГНАЛОВ | 1973 |

|

SU453726A1 |

| Широкополосное приемопередающее устройство с программной перестройкой рабочей частоты | 2016 |

|

RU2631464C1 |

| Широкополосное приемопередающее устройство | 2016 |

|

RU2628328C1 |

| Устройство для асинхронного уплотнения каналов связи с использованием временного разделения сигналов | 1973 |

|

SU479138A1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Устройство прерывистой радиосвязи | 1989 |

|

SU1748263A1 |

УСТРОЙСТВО ДЛЯ АСИНХРОННОГО СОПРЯЖЕНИЯ КАНАЛОВ СВЯЗИ по авт. св. 748896, о т л и ч а ю щ е е С Я тем, что, с целью уменьшения низкочастотных флуктуации выходного сигнала в широком диапазоне нестабильности частоты абонентов, на передающей стороне введены перераспределитель тактов передачи, блок временного выравнивания тактор и первый блок временного преобразования сигналов, причем выходы перераспределителя тактов передачи подключены соответственно к первому входу первого блока временного преобразования сигна, лов, к второму входу блока управле-. НИН и через блок временного выравнивания тактов - к входу считывания блока памяти, выход которого подключен к второму входу первого блока временного преобразования сигналов, к третьему входу которого подключен второй выход блока управления, а выходы первого блока временного преобразования сигналов являются соответственно входами основного и дополнительного каналов связи, а на приемной стороне введены второй блок временного преобразования сигналов и перераспределитель тактов приема, причём выходы второго блока временного преобразования сигналов подключены соответственно к входу дешифратора команд и к входу записи блока памяти, а выходы перераспределителя тактов приема подключены к соответствующим входам второго блока временного преобразования сигналов, дешифратора команд и блока памяти, входы второго блока временного преобразо.вания сигналов подключены к выходам основного и дополнительного каналов связи, а входы ререраспределителей тактов передачи и приема являются соответственно входами основной и дополнительной последовательностей СП тактовых импульсов. ы со |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для асинхронного сопряжения каналов связи | 1977 |

|

SU748896A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-11-07—Публикация

1981-10-13—Подача