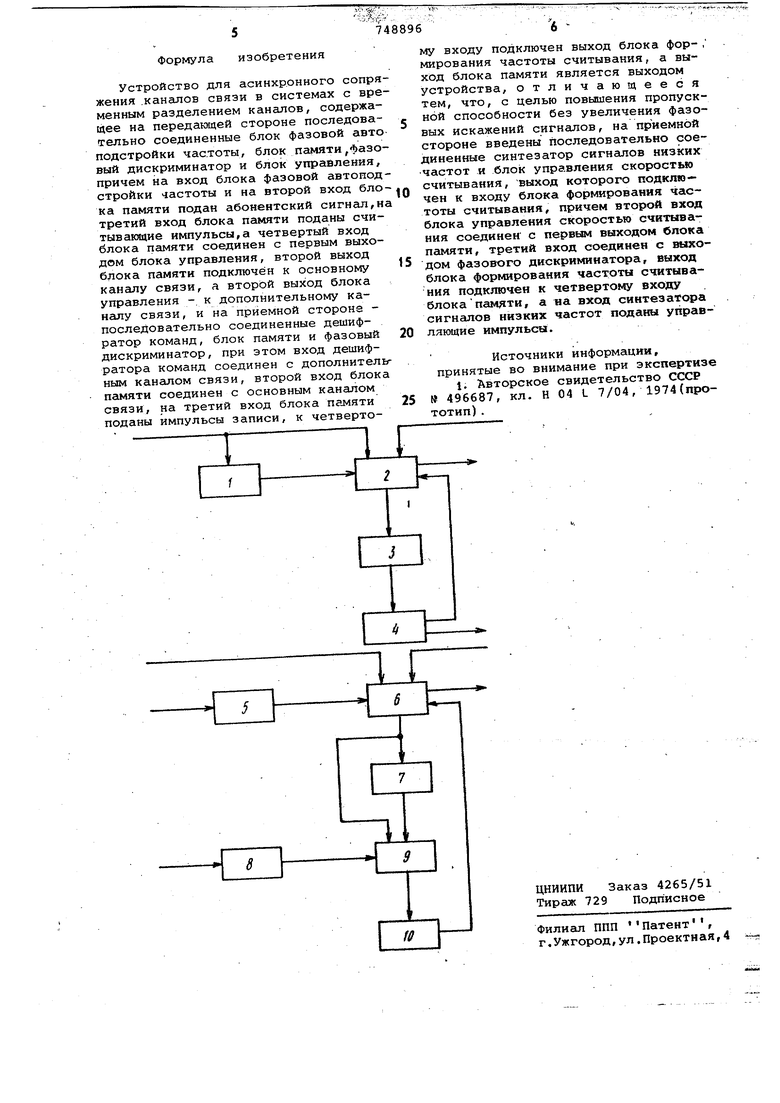

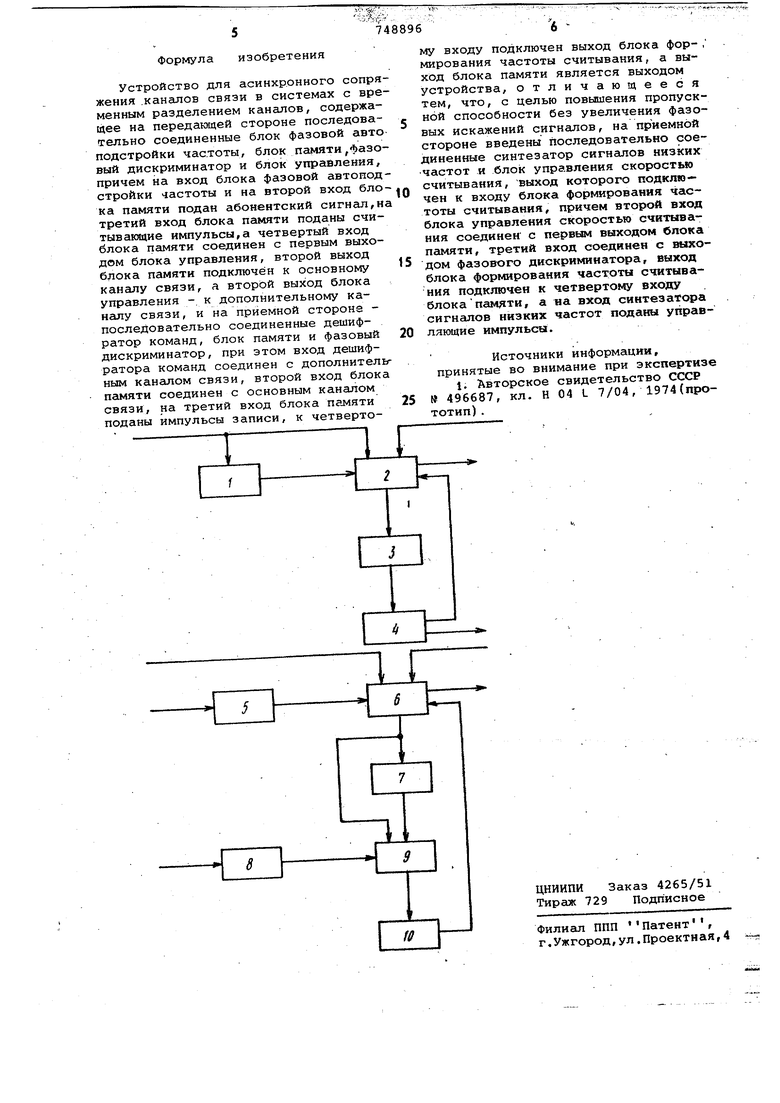

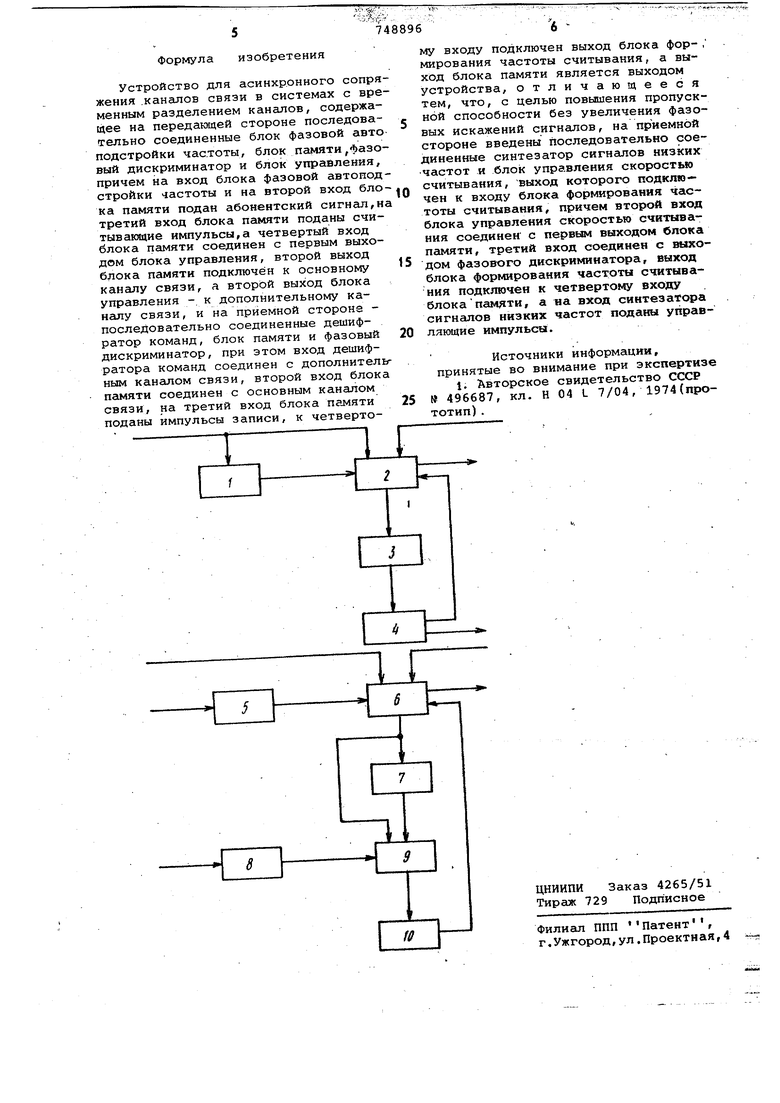

Изобретение относится к э:пектро связй и может быть использовано в многоканальных системах с временным разделением каналов. Известно устройство для асинхронного сопряжения каналов связи в системах с временным разделением каналов , содержащее на передающей стороне последовательно соединенные блок фазовой автоподстройки частоты, блок памяти, фазовый дискриминатор и блок управ.аения,причем н.а вход блока фазовой автоподстройки частоты и на второй вход блока памяти подан абонентский сигнал,на третий вход блока памяти поданы «гчитываюйщие .импульсы, а четвертый вход блока памяти соединен с первнм выходе блока управления,второ выход блока памяти подключен к основному каналу связи, а второй выход бло ка управления - к дополнительному каналу связи, и на приемной стороне последовательно соединенные дешифратор команд, блок памяти и фазовый дис криминатор, при этом вход дешифратора команд соединен с дополнительным каналом связи, второй вход блока памяти соединен с основным каналом связи, на третий вход блока памяти поданы и пульсы записи, к четвертому входу подключен выход блока формирования частоты считывания, а выход блока памяти является выходом устройства . Однако в известном устройстве необходимо наличие второго дополнительного канала связи, по которому передаются сигналы фазовой коррекции, что приводит к снижению пропускной способности устройства. Цель изобретения - повышение про- . пускной способности без увеличения фазовых искажений сигналов. Для этого в устройство для асинхронного сопряжения каналов связи в системах с временным разделением каналов, содержащее на передающей стороне последовательно соединенные блок фазовой автоподстройки частоты, блок памяти, фазовый дискриьтинатор и блок управления, причем на вход блока фазовой автоподстройки частоты и на второй вход блока памяти подан абонентский сигнал, на третий вход блока памяти поданы считывгиощие импульсы, а четвертый вход блока памяти соединен с первым выходом блока управления, второй выход блока подключен к основному каналу связи, а второй выход блока управления - к дополнительному каналу связи, на приемной стороне - последовательно соединенные д шифратор команд, блок памяти и фазовый дискриминатор, при.этом вход дешифратора команд соединен с дополнительным каналом связи, второй вход йлока памяти соединен с основным ка-, алом связи, на третий вход блока riaйяти поданы импульсы записи, к четвер т:ому входу подключен выход блока формирования частоты считывания, а выход блока памяти является выходом устрой ства, на приемной стороне введены пос ледовательно соединенные синтезатор сигналов низких частот и блок управления скоростью считывания, выход которого подключен к входу блока фор мирования частоты считывания, причем второй вход блока управления ско ростью считывания соединен с первым выходом блока памяти, третий вход соединен с выходом фазового дискриминатора, выход блока формирования час тоты считывания подключен к четвертому входу Злока памяти/ а на вход синтезатора сигналов низких частот поданы управляющие импульсы. На чертеже предатавлена структурная схема устройства для асинхронного сопряжения каналов. Устройство содержит на передающей стороне блок 1 фазовой автоподстройки частоты, блок 2 памяти, фазовый дискриминатор 3 и блок 4 управления, а на приемной стороне - дешиф ратор 5 команд, блок б памяти, фазовый дискриминатор 7, синтезатор 8 си налов низких частот, блок 9 управления скоростью считывания и блок 10 формирования частоты считывания. Устройство работает следующим образом. :. Асинхронный абонентский сигнал поступает на блок 1 фазовой автоподстройки частоты, который формирует импульсную последовательность, синхронную с абонентским сигналом, пред назначенную.: для записи в блок 2 памяти. Считывание информации из блока 2 памяти производится импульсами, синхронными с тактовой ча с;еотой кана ла связи, этом информация передается по основному каналу связи. Фа зовый дискриминатор 3 контролирует сдвиг фазы между импульсами записи и считыванийблока 2 памяти и при разности фаз±аж выделяет сигнал, п которому блок 4 управления вырабатыв ет команду стаффицга + (добавить) или -(убавить) в зависимости от зн ка сдвига фаз. Команда стаффинга передается по дополнительному каналу в виде пятнадцатисимвольной кодовой комбинации, при этом команде + соответствует после цовательность из пятнадцатй единиц/ акбманде - и пятнадцати нулей. В фиксированный м мент времени, определяемый свёрхцйкл вой синхронизацией группового оборудования передающей.станции, производится однаиз двух операций: 1.Если по дополнительному каналу передавалась команда +, то по этому каналу передается один информационный бит из эластичной памяти, при этом запас информации в блоке эластич- ной памяти уменьшается на один бит. 2.Если по дополнительному каналу передавалась команда -, то по основному каналу передается балластная посылка, и запас информации в блоке памяти увеличивается на один бит. Та КИМ образом, по дополнительному каналу передаются чередующиеся команды ,+ и - до тех пор, пока фазовый сдвиг между импульсами записи и считывания из блока памяти не превысит 2 Jt . В этом случае двамоды передается одна и, та же команда. Следовательно, структура передаваемых по дополнительному каналу команд стаффинга имеет вид (+-+-+-4-+-+-) , если частота .записи абонента выше частоты считывания канала связи, и (+-+-+-+-+- если частота записи абонента ниже частоты считывания канала связи. Таким образом, в последовательности команд дойолнительного канала заложена информация о частоте асинхронного абонента. На приемной стороне дешифратор 5 команд осуществляет прием команд стаффинга и выдает сигнал управлени.я добавить или убавить в блок б памяти. Информационный сигн, принятый по основному каналу, записывается в блок б памяти. В фиксированный момент времени, определяемой сверхцикловой синхронизацией группового оборудования приёмной станции, осуществляется либо вставка информационной посылки, принятой- по дополнительному каналу (при наличии сигнала добавить, поступающего из дешифратора 5 команд), либо исключение балластной посылки, принятой по основному каналу (при наличии сигнала убавить). Считывание информации из блока 6 памяти производится импульсной последовательностью, сформированной блоком 10 формир ования частоты считывания, который представляет собой yпpaвляe fcIй делитель, подстраивающий дискретным способом выходную последовательность импульсов в зависимости от того, в каком разряде блока б памяти происходит считывание информации. Фазовый дискриминатор 7 сравнивает сдвиг фаз между импульсами записи и считывания блока б памяти и при расхождении фаз Hat 2 вырабатывает сигнал . : о знаке расхождения частот абонента и канала связи, который поступает на блок 9 управления скоростью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для асинхронного сопряжения каналов связи | 1981 |

|

SU1053317A2 |

| Устройство для асинхронного сопряжения каналов связи в системах с временным разделением каналов | 1978 |

|

SU949836A2 |

| Устройство асинхронного сопряжения каналов | 1974 |

|

SU496687A1 |

| Устройство для асинхронного уплотнения каналов связи с использованием временного разделения сигналов | 1973 |

|

SU479138A1 |

| УСТРОЙСТВО ДЛЯ АСИНХРОННОГО УПЛОТНЕНИЯКАНАЛОВ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМСИГНАЛОВ | 1973 |

|

SU453726A1 |

| Приемник сигналов команд согласования скоростей | 1983 |

|

SU1145486A1 |

| УСТРОЙСТВО ВРЕМЕННОГО УПЛОТНЕНИЯ АСИНХРОННЫХ | 1973 |

|

SU385399A1 |

| Устройство для асинхронного сопряжения каналов | 1977 |

|

SU690638A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Многоканальное устройство передачи и приема асинхронных цифровых сигналов | 1988 |

|

SU1555886A1 |

Авторы

Даты

1980-07-15—Публикация

1977-12-15—Подача