(54) УСТРОЙСТВО ДЛЯ АСИНХРОННОГО СОПРЯЖЕНИЯ

КАНАЛОВ СВЯЗИ В СИСТЕМАХ С ВРЕМЕННЫМ

РАЗДЕЛЕНИЕМ КАНАЛОВ

1

Изобретение относится к электросвязи и может быть использовано в аппаратуре асинхронной передачи двоичной информации.

По основному авт. св. № 748896 известно устройство для асинхронного сопряжения каналов связи в системах, с временным разделением каналов содержит на передающей стороне последовательно соединенные блок фазовой автоподстройки частоты, блок памяти, первый фазовый дискриминатор и блок управления, причем на вход блока фазовой автоподстройки частоты и на второй вход блока памяти подан абонентский сигнал, а на третий вход блока памяти поданы считывающие импульсы, а четвертый вход блока памяти соединен с первым выходом блока управления, второй выход блока памяти подключен к основному каналу связи, а второй выход блока управления - к дополнительному каналу связи, а на приемной стороне последовательно соединенные дешифратор команд, блок па1йяти и второй фазовый дискриминатор, причем вход дешифратора команд соединен с дополнительным каналом связи, второй вход блока памяти соединен с основным каналом связи, на третий вход блока памяти поданы импульсы записи, к четвертому входу подключен выход блока формирования частоты считывания, а выход блока памяти является выходом устройства, а также содержит на приемной стороне последовательно соединенные синтезатор низких частот и блок управления скоростью считывания, выход которого подключен к входу блока формирования частоты считывания, причем второй вход блока управления скоростью считывания

10 соединен с первым выходом блока памяти, третий вход - с выходом второго фазового дискриминатора, а выход блока формирования частоты считывания подключен к четвертому входу блока памяти, а на вход синтезатора сигналов низких частот поданы

15 управляющие импульсы 1.

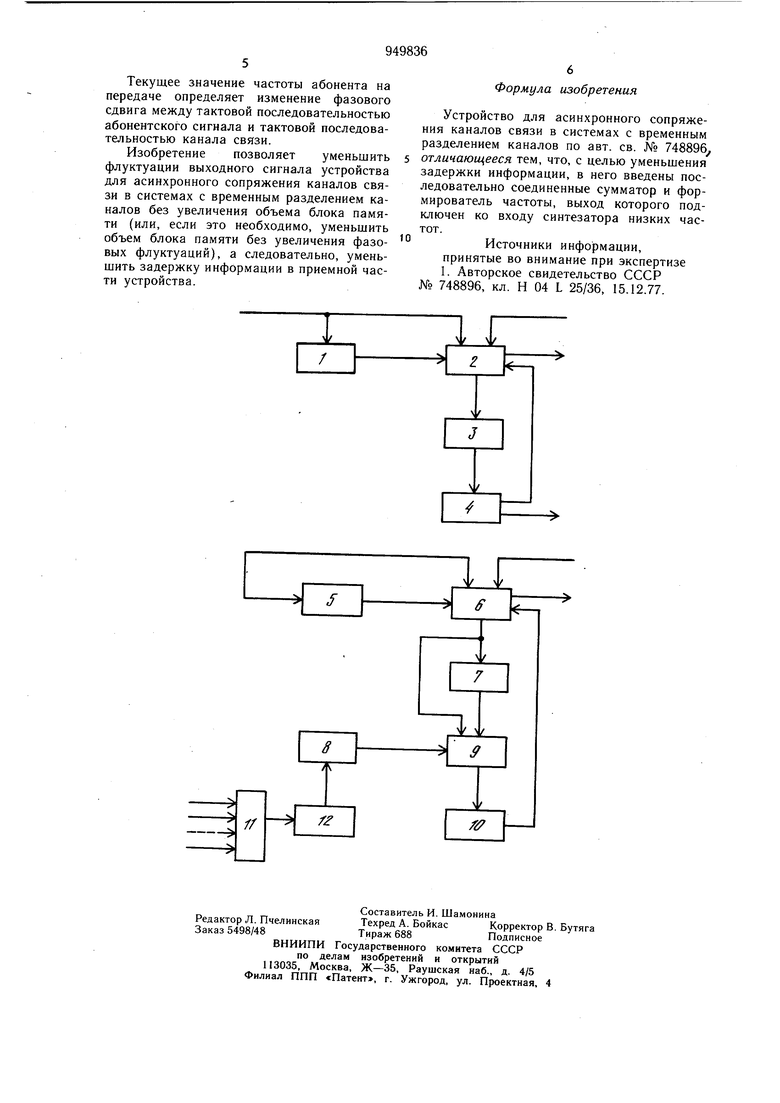

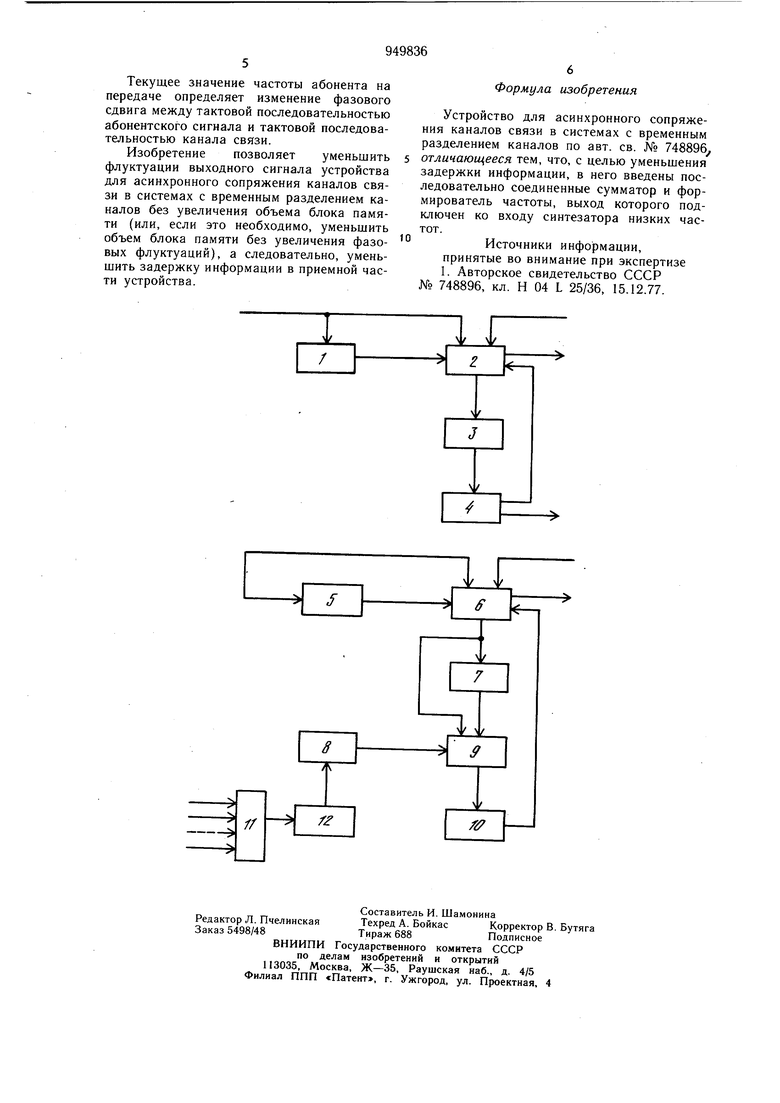

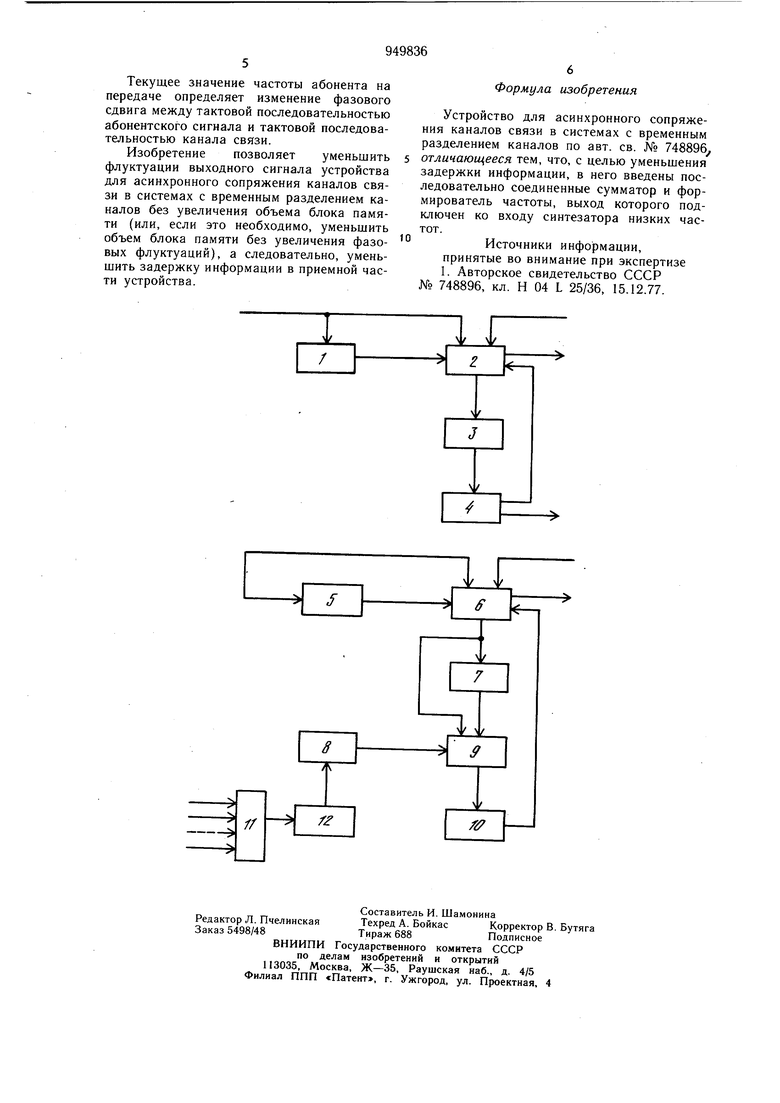

Однако в случаях предъявления высоких требований к максимальной величине низкочастотных фазовых флуктуации, например, 2Q при работе с высокостабильным по частоте . абонентом необходимо увеличение количества разрядов блока памяти. Это приводит к дополнительным задержкам информации между передающим и приемным абонентами. Вносимая дополнительная задержка информации равносильна увеличению длины канала связи, что весьма нежелательно при работе с высокой достоверностью нередаваемой информации, так как резко снижается эффективная скорость передачи абонентов, имеющих устройства защиты от ошибок, а при передаче быстро стареющей информации дополнительные задержки вообще недопустимы. Цель изобретения .- уменьшение задержки информации. Для достижения указанной цели в устройстве для синхронного сопряжения каналов связи в системах с временным разделением каналов введены последовательно соединенные сумматор и формирователь частоты, выход которого подключен ко входу синтезатора низких частот. На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит на передающей стороне блок I фазовой автоподстройки частоты, блок 2 памяти, первый фазовый дискриминатор 3, блок 4 управления, а на приемной стороне - дешифратор 5 команд, блок 6 памяти, второй фазовый дискриминатор 7, синтезатор 8 низких частот, блок 9 управления скоростью считывания, блок 10 форми|)ования частоты считывания, сумматор 11 и формирователь 12 частоты. Устройство работает следуюш.им образом. На вход сумматора 11 поступают от источника импульсов группового оборудования приемной станции п последовательностей импульсов с частотой, равной частоте записи в блок памяти, и с временным сдвигом относительно друг друга и тактов записи (для наглядности и удобства изложения пртщниов работы устройства п принято равное трем). На выходе сумматора 11 формируется тактовая последовательность, равная сумме трех входных последовательностей, приче.м временные позиции выходной последовательности поочередно соответствуют временным позициям первой, второй и третьей входным последовательностям. Последовательность с выхода сумматора 11 поступает на вход формирователя 12 частоты, предетавляющего собой делитель частоты с коэффициентом деления R, при этом число последовательностей п и коэффициент деления R связаны зависимостью R n+l (в данном случае k 4). В результате деления на четыре получается последовательность, временные позиции которой поочередно расположены во временных позициях первой, второй и третьей входных последовательностей сумматора 11. Сформированная с помощью сумматора 11 и формирователя 12 частоты последовательность поступает на вход синтезатора 8 низких частот, представляющего собой делитель частоты с коэффициентом деления ш, при этом если R число четное, то m также число четное и если k число нечетное, то и m число нечетное. Синтезатор 8 низких частот формирует низкочастотные добавки путем деления частоты, сформированной сумматором 11 и формирователем 12 частоты, при этом временные позиции полученных низкочастотных добавок поочередно .расположены во временных позициях трех входных последовательностей сумматора 11 и, следовательно, эти добавки появляются в разные моменты времени внутри интервала тактов записи. Такты записи последовательно записывают информацию в блок 2 памяти и одновременно устанавливают разрешение на выдачу низкочастотной добавки. Низкочастотная добавка поступает на вход блока 10 формирования частоты считывания, представляющего собой управляемый делитель абонентского сигнала и тактовой последовательность на один шаг дискретной подстройки с частотой низкочастотных добавок. Такты считывания считывают информацию из блока 2 памяти и одновременно запрещают выдачу низкочастотной добавки на формирователь 10 частоты считывания. Таким образом, сигнал, разрещающий выдачу низкочастотных добавок, изменяет свою длительность. При максимальной длительности разрещающего сигнала, равной длительности тактового интервала записи, на блок 10 формирования частоты считывания поступают все низкочастотные добавки, соответствующие текущему положению памяти, и по мере уменьшения длительности разрешающего сигнала количество низкочастотных добавок, поступающих на блок 10 формирования частоть считывания, уменьшается пропорционально длительности разрешающего сигнала. Таким образом, в течение работы одного разряда памяти происходит плавное изменение частоты считывания пропорционально фазовому сдвигу между тактами записи и считывания блока 2 памяти. Устройство работает следующим образом. Низкочастотная добавка, соответствующая текущему положению блока 2 памяти, поступает на управляющий вход блока 10 формирования частоты считывания, представляющего собой управляемый делитель, на выходе которого формируется тактовая частота считывания, значение которой определяется величиной низкочастотной добавки. Таким образом, для каждого положения блока 2 памяти формируется соответствующая частота считывания, т. е. каждому разряду памяти соответствует определенная частотная градация считывающей последовательности.

Текущее значение частоты абонента на передаче определяет изменение фазового сдвига между тактовой последовательностью абонентского сигнала и тактовой последовательностью канала связи.

Изобретение позволяет уменьшить флуктуации выходного сигнала устройства для асинхронного сопряжения каналов связи в системах с временным разделением каналов без увеличения объема блока памяти (или, если это необходимо, уменьшить объем блока памяти без увеличения фазовых флуктуации), а следовательно, уменьшить задержку информации в приемной части устройства.

Формула изобретения

Устройство для асинхронного сопряжения каналов связи в системах с временным разделением каналов по авт. св. № 748896, отличающееся тем, что, с целью уменьшения задержки информации, в него введены последовательно соединенные сумматор и формирователь частоты, выход которого подключен ко входу синтезатора низких частот.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 748896, кл. Н 04 L 25/36, 15.12.77.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для асинхронного сопряжения каналов связи | 1981 |

|

SU1053317A2 |

| Устройство для асинхронного сопряжения каналов связи | 1977 |

|

SU748896A1 |

| Устройство для передачи и приема информации с временным уплотнением каналов | 1978 |

|

SU746951A2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство для передачи ипРиЕМА диСКРЕТНОй иНфОРМАциипО пАРАллЕльНыМ КАНАлАМ СВязипЕРЕМЕННОй длиНы | 1978 |

|

SU794753A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство синхронизации станции коммутации каналов | 1987 |

|

SU1536518A1 |

| СПОСОБ И УСТРОЙСТВО ВЫСОКОСКОРОСТНОЙ И НИЗКОСКОРОСТНОЙ СВЯЗИ ЧЕРЕЗ СПУТНИКИ НА НИЗКИХ И СРЕДНИХ ОРБИТАХ | 1997 |

|

RU2133555C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| СПОСОБ ПОИСКА СИГНАЛА И НАЧАЛЬНОЙ СИНХРОНИЗАЦИИ КАНАЛОВ В СИСТЕМЕ СПУТНИКОВОЙ СВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2065253C1 |

Авторы

Даты

1982-08-07—Публикация

1978-02-15—Подача