|:

// - 12 10

ел

а

QO

4j

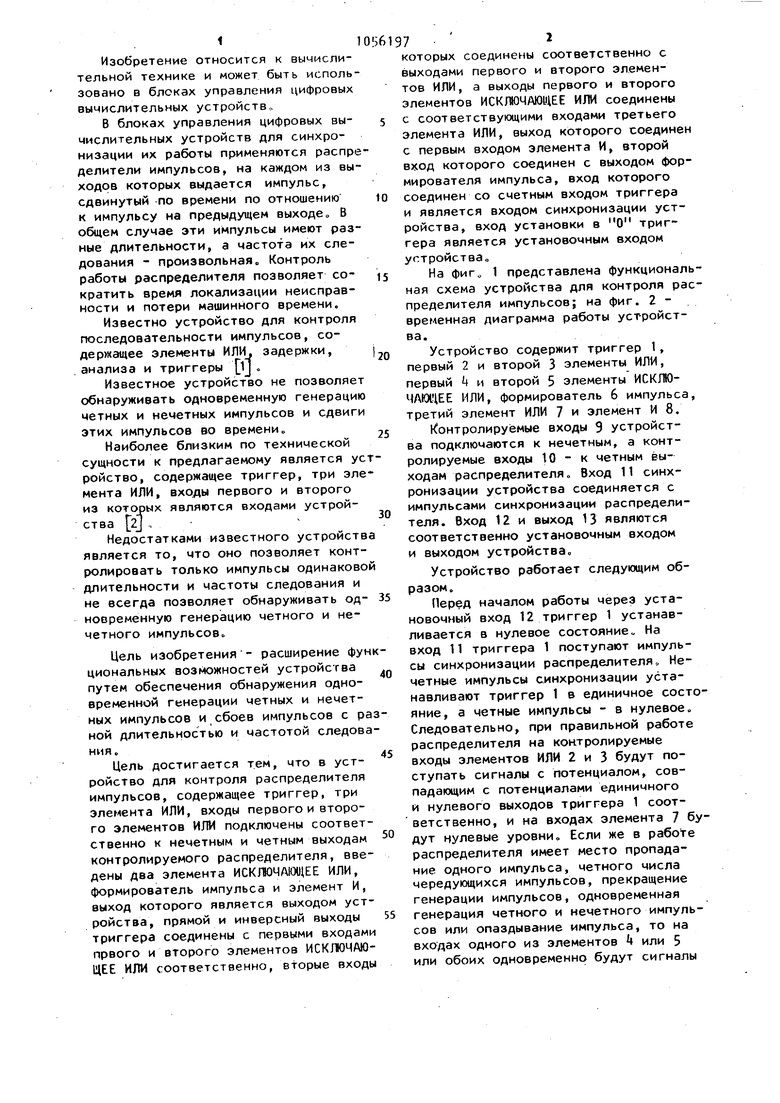

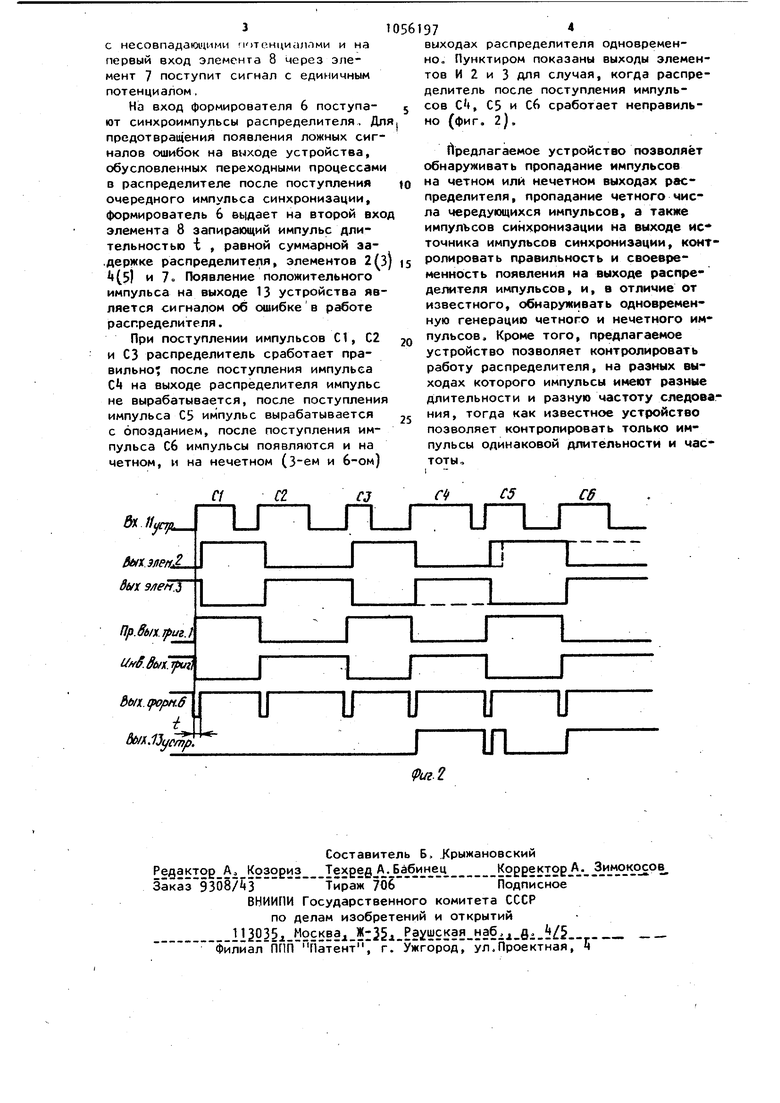

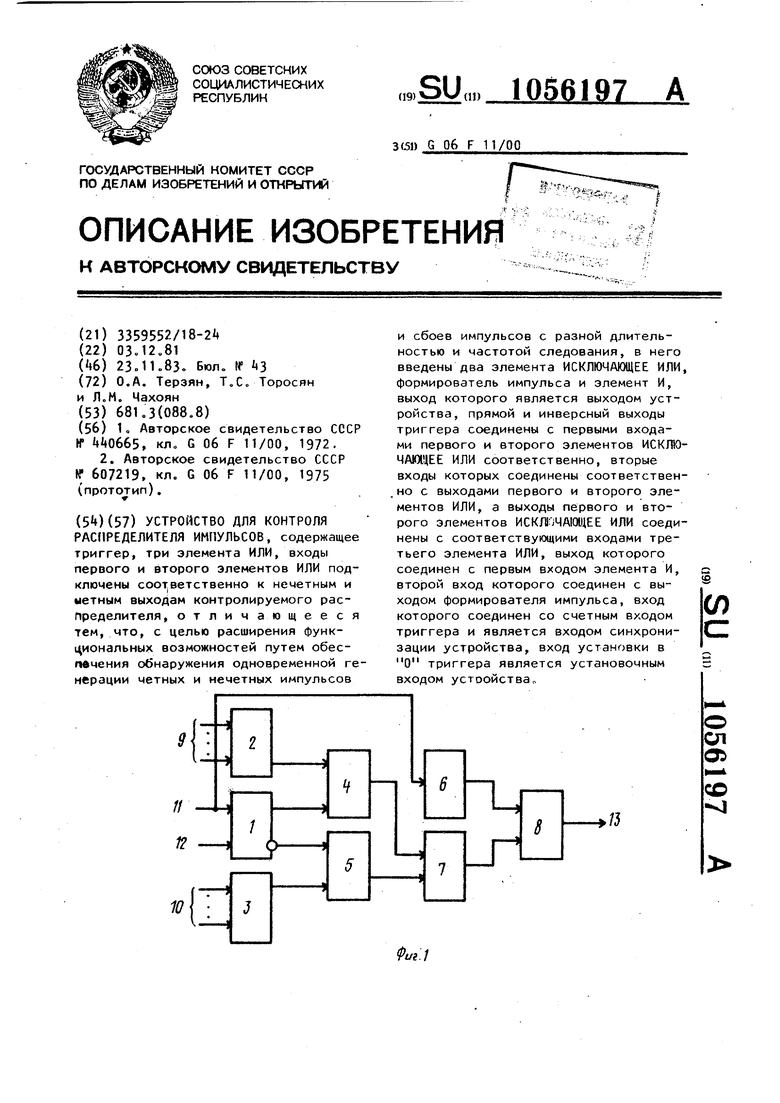

./5 Изобретение относится к вычислительной технике и может быть использовано в блоках управления цифровых вычислительных устройств В блоках управления цифровых вычислительных устройств для синхронизации их работы применяются распре делители импульсов, на каждом из выходов которых выдается импульс, сдвинутый по времени по отношению к импульсу на предыдущем выходе о В общем случае эти импульсы имеют разные длительности, а частота их следования - произвольная,, Контроль работы распределителя позволяет сократить время локализации неисправности и потери машинного времени. Известно устройство для контроля последовательности импульсов, содержащее элементы ИЛИ, задержки, .анализа и триггеры m. Известное устройство не позволяет обнаруживать одновременную генерацию четных и нечетных импульсов и сдвиги этих импульсов во времени Наиболее близким по технической сущности к предлагае зму является ус ройство, содержащее триггер, три эле мента ИЛИ, входы первого и второго из которых являются входами устройства 2J .. Недостатками известного устройств является то, что оно позволяет контролировать только импульсы одинаково длительности и частоты следования и не всегда позволяет обнаруживать одновременную генерацию четного и нечетного импульсов Цель изобретения- расширение фун циональных возможностей устройства путем обеспечения обнаружения одновременной генерации четных и нечетных импульсов и сбоев импульсов с ра ной длительностью и частотой следова ния. Цель достигается тем, что в устройство для контроля распределителя импульсов, содержащее триггер, три элемента ИЛИ, входы первого и второго элементов ИЛИ подключены соответственно к нечетным и четным выходам контролируемого распределителя, введены два элемента ИСКЛОЧЛЩЕЕ ИЛИ, формирователь импульса и элемент И, выход которого является выходом устройства, прямой и инверсный выходы триггера соединены с первыми входами првого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, вtopыe входы которых соединены соответственно с выходами первого и второго элементов ИЛИ, а выходы первого и второго элементов ИСКШ}ЧАЮУ1ЕЕ ИЛИ соединены с соответствуиэщими входами третьего элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом формирователя импульса, вход которого соединен со счетным входом триггера и является входом синхронизации устройства, вход установки в О три1- гера является установочным входом устройства На фиг„ 1 представлена функциональная схема устройства для контроля распределителя импульсов; на фиг. 2 временная диаграмма работы устройства. Устройство содержит триггер 1, первый 2 и второй 3 элементы ИЛИ, первый 4 и второй 5 элементы ИСКШЧЛЮ11ЕЕ ИЛИ, формирователь 6 импульса, третий элемент ИЛИ 7 и элемент И 8. Контролиру1емые входы 9 устройства подключаются к нечетным, а контролируемые входы to - к четным выходам распределителя. Вход 11 синхронизации устройства соединяется с импульсами синхронизации распределителя. Вход 12 и выход 13 являются соответственно установочным входом и выходом устройства Устройство работает следующим образом. Перед началом работы через установочный вход 12 триггер 1 устанавливается в нулевое состояние , На вход 11 триггера 1 поступают импульсы синхронизации распределителя Нечетные импульсы синхронизации устанавливают триггер 1 в единичное состояние, а четные импульсы - в нулевое Следовательно, при правильной работе распределителя на контролируемые входы элементов ИЛИ 2 и 3 будут поступать сигналы с потенциалом, совпадающим с потенциалами единичного и нулевого выходов триггера 1 соответственно, и на входах элемента 7 будут нулевые уровни. Если же в работе распределителя имеет место пропадание одного импульса, четного числа чередующихся импульсов, прекращение генерации импульсов, одновременная генерация четного и нечетного импульсов или опаздывание импульса, то на входах одного из элементов k или 5 или обоих одновременно будут сигналы с несовпадаю1цими пчтенциаллми и на первый вход элемента 8 через элемент 7 поступит сигнал с единичным потенциалом. На вход формирователя 6 поступают синхроимпульсы распределителя. Дл предотвра|дения появления ложных си(- налов ошибок на выходе устройства, обусловленных переходными процессами в распределителе после поступления очередного импульса синхронизации, формирователь 6 вьщает на второй вхо элемента 8 запирающий импульс длительностью t , равной суммарной за.держке распределителя, элементов 2M (5 и 7. Появление положительного импульса на выходе 13 устройства яв ляется сигналом об ошибкев работе распределителя. При поступлении импульсов С1, С2 и СЗ распределитель сработает правильно после поступления импульса С на выходе распределителя импульс не вырабатывается, после поступлени импульса С5 импульс вырабатывается с опозданием, после поступления импульса Сб импульсы появляются и на четном, и на нечетном (З-ем и 6-ом) 97 выходах распределителя одновременно. Пунктиром показаны выходы элементов И 2 и 3 для случая, когда распределитель после поступления импульсов С, С5 и Сб сработает неправильно (фиг. 2). Предлагаемое устройство позволяет обнаруживать пропадание импульсов на четном или нечетном выходах распределителя , пропадание четного числа чередующихся импульсов, а также импульсов синхронизации на выходе ис точника импульсов синхронизации, контролировать правильность и своевременность появления на выходе распределителя импульсов, и, в отличие от известного, обнаруживать одновременную генерацию четного и нечетного импульсов. Кроме того, предлагаемое устройство позволяет контролировать работу распределителя, на разных выходах которого импульсы имеют разные длительности и разную частоту следова ния, тогда как известное устройство позволяет контролировать только импульсы одинаковой длительности и частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления периодических временных интервалов на заданное число интервалов | 1987 |

|

SU1451689A1 |

| Устройство для обнаружения состязаний в синхронизируемых дискретных блоках | 1985 |

|

SU1298750A1 |

| Устройство для контроля блоков синхронизации | 1983 |

|

SU1134940A1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| Устройство для контроля многоканального аппарата магнитной записи и воспроизведения | 1988 |

|

SU1610508A1 |

| Датчик сообщений | 1985 |

|

SU1282348A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для контроля четности двоичного последовательного кода | 1989 |

|

SU1702373A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство для воспроизведения цифровых сигналов | 1981 |

|

SU1067528A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАСПРЕДЕЛИТЕЛЯ ИМПУЛЬСОВ, содержащее триггер, три элемента ИЛИ, входы первого и второго элементов ИЛИ подключены соответственно к нечетным и I ыетным выходам контролируемого распределителя, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения обнаружения одновременной генерации четных и нечетных импульсов и сбоев импульсов с разной длительностью и частотой следования, в него введены два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь импульса и элемент И, выход которого является выходом устройства, прямой и инверсный выходы триггера соединены с первыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, вторые входы которых соединены соответствен.но с выходами первого и второго элементов ИЛИ, а выходы первого и второго элементов ИСКЛОЧАЩЕЕ ИЛИ соединены с соответствующими входами третьего элемента ИЛИ, выход которого соединен с первым входом элемента И, S второй вход которого соединен с вы(Л ходом формирователя импульса, вход которого соединен со счетным входом триггера и является входом синхронизации устройства, вход установки в О триггера является установочным входом устоойства„

Авторы

Даты

1983-11-23—Публикация

1981-12-03—Подача