Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки логических блоков.

Цель изобретения - повышение достоверности обнаружения состязаний,

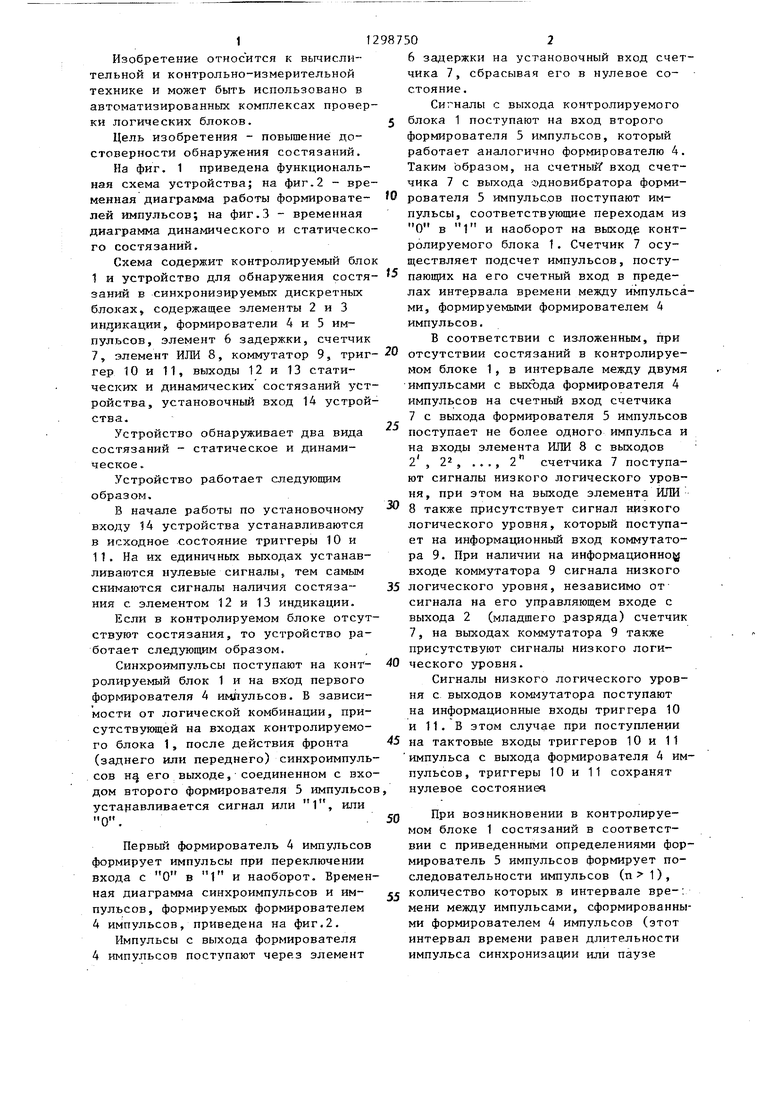

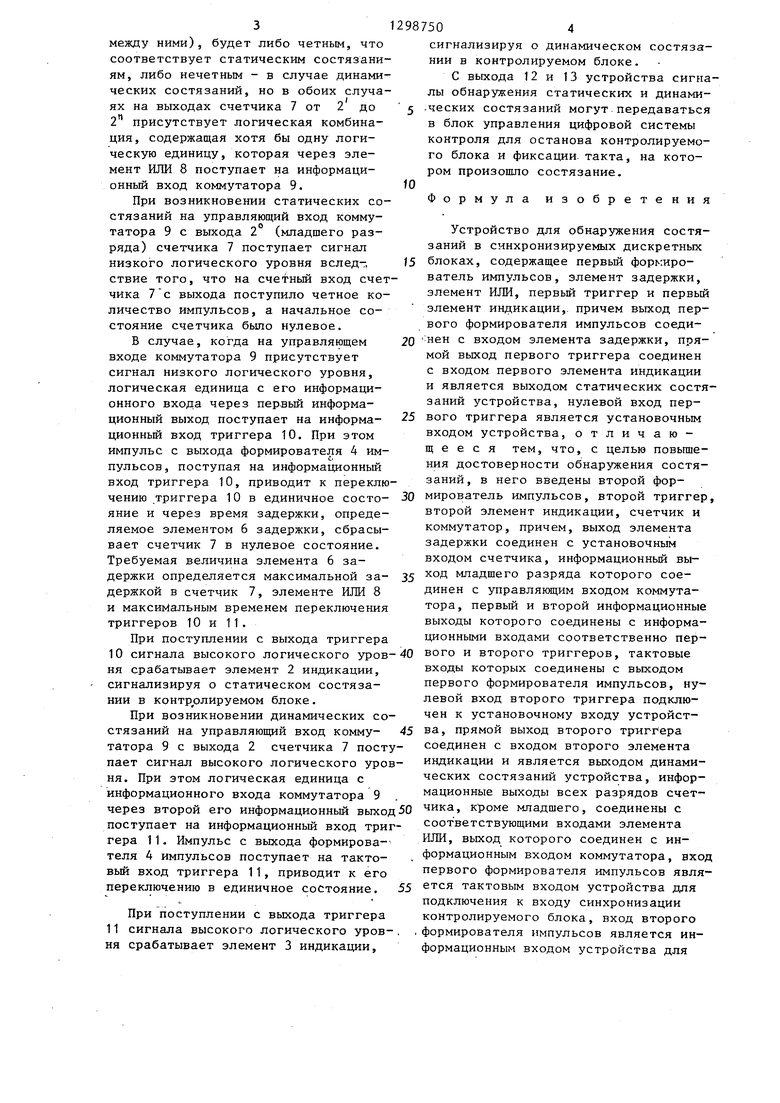

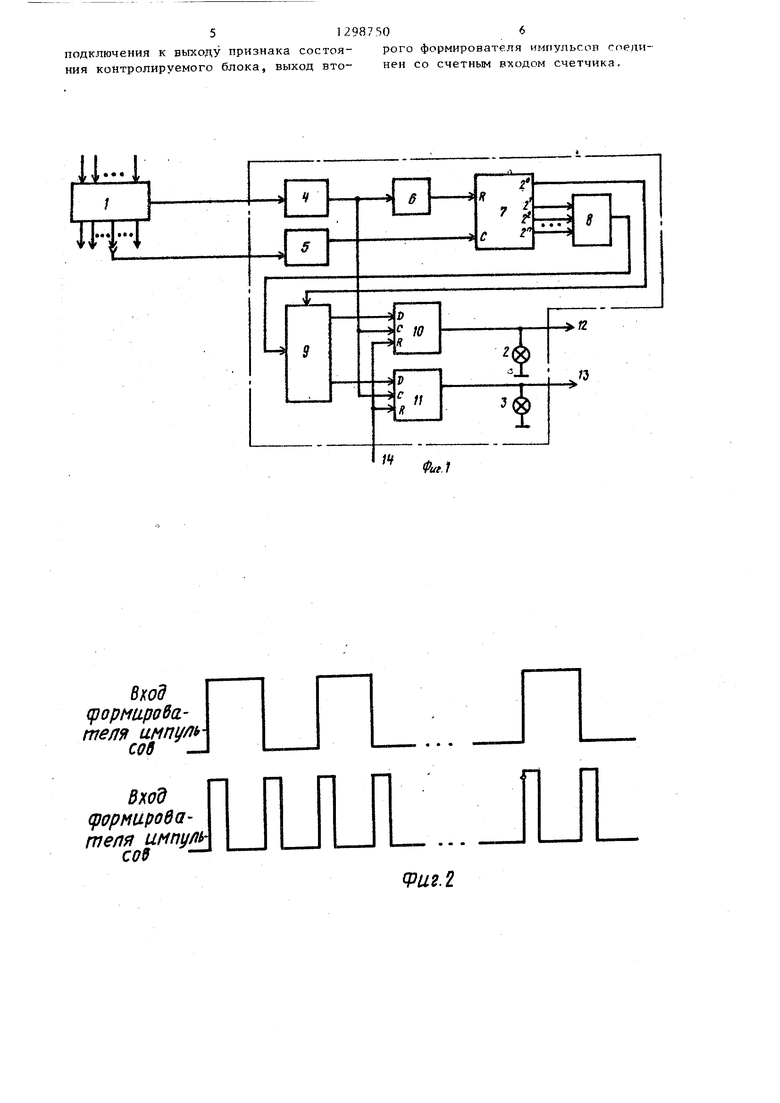

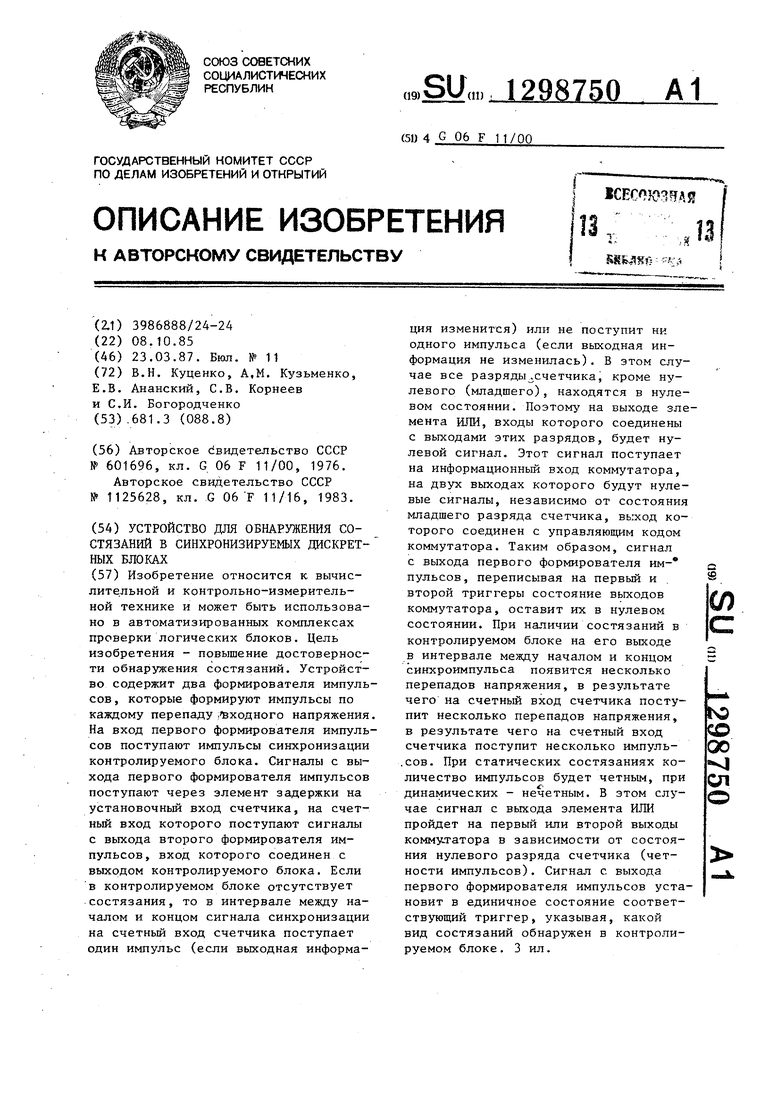

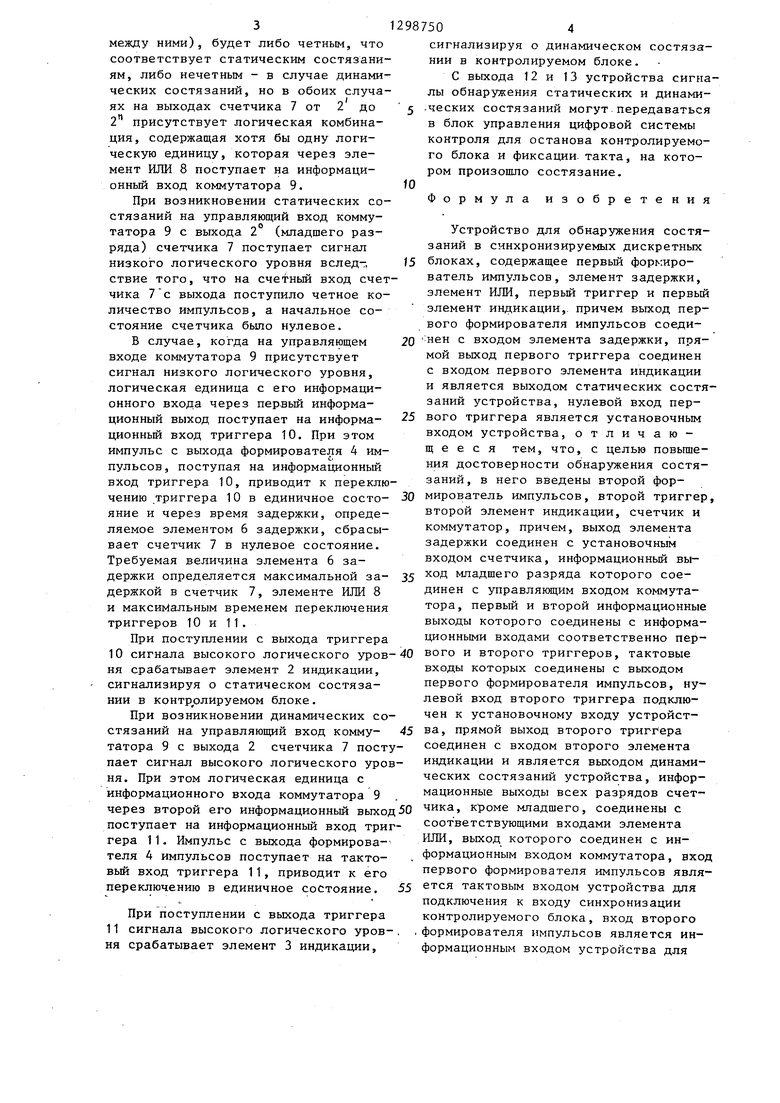

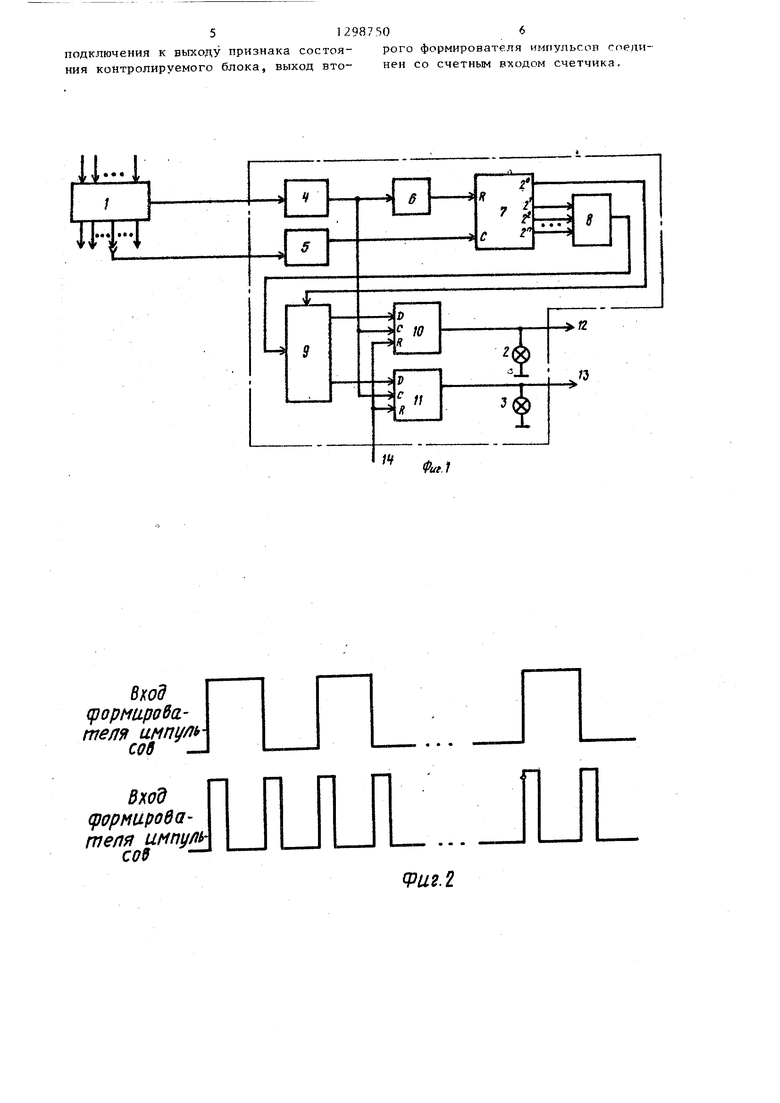

На фиг. 1 приведена функциональная схема устройства; на фиг.2 - временная диаграмма работы формировате- лей импульсов; на фиг.З - временная диаграмма динамического и статического состязаний.

Схема содержит контролируемый блок 1 и устройство для обнаружения состя- заний в синхронизируемых дискретных блоках, содержащее элементы 2 и 3 индикации, формирователи 4 и 5 импульсов, элемент 6 задержки, счетчик 7, элемент ИЛИ 8, коммутатор 9, триг- гер 10 и 11, выходы 12 и 13 статических и динамических состязаний устройства, установочный вход 14 устройства.

Устройство обнаруживает два вида состязаний - статическое и динамическое .

Устройство работает следующим образом,

В начале работы по установочному входу 14 устройства устанавливаются в исходное состояние триггеры 10 и 11. На их единичных выходах устанавливаются нулевые сигналы, тем самым снимаются сигналы наличия состяза- ния с элементом 12 и 13 индикации.

Если в контролируемом блоке отсутствуют состязания, то устройство работает следующим образом.

Синхроимпульсы поступают на конт- ролируемый блок 1 и на первого формирователя 4 шдаульсов. В зависимости от логической комбинации, присутствующей на входах контролируемого блока 1, после действия фронта (заднего или переднего) синхроимпульсов н его выходе, соединенном с входом второго формирователя 5 импульсов устаравливается сигнал или 1, или О.

Первьп формирователь 4 импульсов формирует импульсы при переключении входа с О в 1 и наоборот. Времен

ная диаграмма синхроимпульсов и импульсов, формируемых формирователем 4 импульсов, приведена на фиг.2.

Импульсы с выхода формирователя 4 импульсов поступают через элемент

5

5

О

0

5

0 0

0

5

6задержки на установочный вход счетчика 7, сбрасывая его в нулевое состояние.

Сигналы с выхода контролируемого блока 1 поступают на вход второго формирователя 5 импульсов, который работает аналогично формирователю 4. Таким образом, на счетный вход счетчика 7 с выхода фдновибратора формирователя 5 импульс.ов поступают импульсы, соответствующие переходам из О в 1 и наоборот на вькоде контролируемого блока 1. Счетчик 7 осуществляет подсчет импульсов, поступающих на его счетный вход в пределах интервала времени между импульсами, формируемыми формирователем 4 импульсов.

В соответствии с изложенным, при отсутствии состязаний в контролируемом блоке 1, в интервале между двумя импульсами с выхода формирователя 4 импульсов на счетный вход счетчика

7с выхода формирователя 5 импульсов поступает не более одного импульса и на входы элемента ИЛИ 8 с выходов

2 , 2 , ..., 2 счетчика 7 поступают сигналы низкого логического уровня, при этом на выходе элемента ИЛИ

8также присутствует сигнал низкого логического уровня, который поступает на информационный вход коммутатора 9. При наличии на информационно входе коммутатора 9 сигнала низкого логического уровня, независимо от сигнала на его управляющем входе с выхода 2 (младшего разряда) счетчик 7, на выходах коммутатора 9 также присутствуют сигналы низкого логического уровня.

Сигналы низкого логического уровня с выходов ком1-1утатора поступают на информационные входы триггера 10 и 11. В этом случае при поступлении на тактовые входы триггеров 10 и 11 импульса с выхода формирователя 4 импульсов, триггеры 10 и 11 сохранят нулевое состоянием

При возникновении в контролируемом блоке 1 состязаний в соответствии с приведенными определениями формирователь 5 импульсов формирует последовательности импульсов (п 1), количество которых в интервале вре-; мени между импульсами, сформированными формирователем 4 импульсов (зтот интервал времени равен длительности импульса синхронизации или паузе

между ними), будет либо четным, что соответствует статическим состязаниям, либо нечетным - в случае динамических состязаний, но в обоих случаях на выходах счетчика 7 от 2 до 2 присутствует логическая комбинация, содержащая хотя бы одну логическую единицу, которая через элемент ИЛИ 8 поступает на информаци- онньш вход коммутатора 9.

При возникновении статических состязаний на управляющий вход коммутатора 9 с выхода 2 (младшего разряда) счетчика 7 поступает сигнал низкого логического уровня вслед- ствие того, что на счефный вход счетчика 7с выхода поступило четное количество импульсов, а начальное состояние счетчика бьшо нулевое.

В случае, когда на управляющем входе коммутатора 9 присутствует сигнал низкого логического уровня, логическая единица с его информационного входа через первый информационный выход поступает на информа- ционньм вход триггера 10, При этом импульс с выхода формирователя 4 импульсов, поступая на информационный вход триггера 10, приводит к переключению .триггера 10 в единичное состо- яние и через время задержки, определяемое элементом 6 задержки, сбрасывает счетчик 7 в нулевое состояние. Требуемая величина элемента 6 задержки определяется максимальной за- держкой в счетчик 7, элементе ИЛИ 8 и максимальным временем переключения триггеров 10 и 11.

При поступлении с выхода триггера

10сигнала высокого логического уров ня срабатывает элемент 2 индикации, сигнализируя о статическом состязании в контролируемом блоке.

При возникновении динамических состязаний на управляющий вход комму- татора 9 с выхода 2 счетчика 7 постпает сигнал высокого логического уроня. При этом логическая единица с информационного входа коммутатора 9 через второй его информационный выхо поступает на информационный вход тригера 11. Импульс с выхода формирователя 4 импульсов поступает на такто- вьй вход триггера 11, приводит к его переключению в единичное состояние.

При поступлении с выхода триггера

11сигнала высокого логического уров ня срабатывает элемент 3 индикации.

сигнализируя о динамическом состязании в контролируемом блоке.

С выхода 12 и 13 устройства сигналы обнаружения статических и динами- .ческих состязаний могут передаваться в блок управления цифровой системы контроля для останова контролируемого блока и фиксации такта, на котором произопшо состязание.

Формула изобретения

Устройство для обнаружения состязаний в синхронизируемых дискретных блоках, содержащее первый форь:иро- ватель импульсов, элемент задержки, элемент ИЛИ, первый триггер и первый элемент индикации,, причем выход первого формирователя импульсов соеди- :нен с входом элемента задержки, прямой выход первого триггера соединен с входом первого элемента индикации и является выходом статических состязаний устройства, нулевой вход первого триггера является установочным входом устройства, отличающееся тем, что, с целью повьпие- ния достоверности обнаружения состязаний, в него введены второй формирователь импульсов, второй триггер второй элемент индикации, счетчик и коммутатор, причем, выход элемента задержки соединен с установочным входом счетчика, информационньш выход младшего разряда которого соединен с управляклцим входом коммутатора, первый и второй информационные выходы которого соединены с информационными входами соответственно первого и второго триггеров, тактовые входы которых соединены с выходом первого формирователя импульсов, нулевой вход второго триггера подключен к установочному входу устройства, прямой выход второго трт1ггера соединен с входом второго элемента индикации и является выходом динамических состязаний устройства, информационные выходы всех разрядов счетчика, к роме младшего, соединены с соответствующими входами элемента ИЛИ, выход которого соединен с информационным входом коммутатора, вхо первого формирователя импульсов является тактовым входом устройства для подключения к входу синхронизации контролируемого блока, вход второго формирователя импульсов является информационным входом устройства для

512987306

подключения к выходу признака состоя- рого формирователя импульсоп спеди- ния контролируемого блока, выход вто- иен со счетным входом счетчика.

Вкод

ср ормиро бате/1 импул1 со б -

ЬмЪ qjopMUpoeaтеля uMnyflk- со9

If

Фие.1

VU2.2.

Вход

формирователя импульсов

Вкод (рормиро-

Ьишеля5 инпуль- сов без состязании,

Bj(od (рормирова.П1еля5

при. наличии, состязйний

Статическое состязания

Редактор Е. Папп

Составитель В. Гречнев Техред М.Ходанич Корректор А, Ильин

Заказ 890/51Тираж 673 . Подписное

ВНИИПИ Государственного кo штeтa СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Линамичесние состязание

fPU2.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых последовательностей | 1989 |

|

SU1686448A1 |

| Устройство для сопряжения с датчиками | 1989 |

|

SU1695286A1 |

| Система для контроля и управления | 1985 |

|

SU1273932A1 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для измерения механической скорости бурения | 1979 |

|

SU863843A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки логических блоков. Цель изобретения - повышение достоверности обнаружения состязаний. Устройство содержит два формирователя импульсов , которые формируют импульсы по каждому перепаду , Входного напряжения. На вход первого формирователя импульсов поступают импульсы синхронизации контролируемого блока. Сигналы с выхода первого формирователя импульсов поступают через элемент задержки на установочный вход счетчика, на счетный вход которого поступают сигналы с выхода второго формирователя импульсов, вход которого соединен с выходом контролируемого блока. Если в контролируемом блоке отсутствует состязания, то в интервале между началом и концом сигнала синхронизации на счетный вход счетчика поступает один импульс (если выходная информация изменится) или не поступит ни одного импульса (если выходная информация не изменилась). В этом случае все разряды .счетчика, кроме нулевого (младшего), находятся в нулевом состоянии. Поэтому на выходе элемента ИЛИ, входы которого соединены с выходами этих разрядов, будет нулевой сигнал. Этот сигнал поступает на информационный вход коммутатора, на двух выходах которого будут нулевые сигналы, независимо от состояния младшего разряда счетчика, выход которого соединен с управляющим кодом коммутатора. Таким образом, сигнал с выхода первого формирователя им- пульсов, переписывая на первьш и второй триггеры состояние вьгходов коммутатора, оставит их в нулевом состоянии. При наличии состязаний в контролируемом блоке на его выходе в интервале между началом и концом синхроимпульса появится несколько перепадов напряжения, в результате чего на счетный вход счетчика поступит несколько перепадов напряжения, в результате чего на счетный вход счетчика поступит несколько импуль- .сов. При статических состязаниях количество импульсов будет четным, при динамических - нечетным. В этом случае сигнал с выхода элемента ИЛИ пройдет на первый или второй выходы коммутатора в зависимости от состояния нулевого разряда счетчика (четности импульсов). Сигнал с выхода первого формирователя импульсов установит в единичное состояние соответствующий триггер, указывая, какой вид состязаний обнаружен в контролируемом блоке. 3 ил. Q

| Устройство для предварительной обработки информации | 1976 |

|

SU601696A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения сбоев синхронизируемых дискретных блоков | 1983 |

|

SU1125628A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-08—Подача