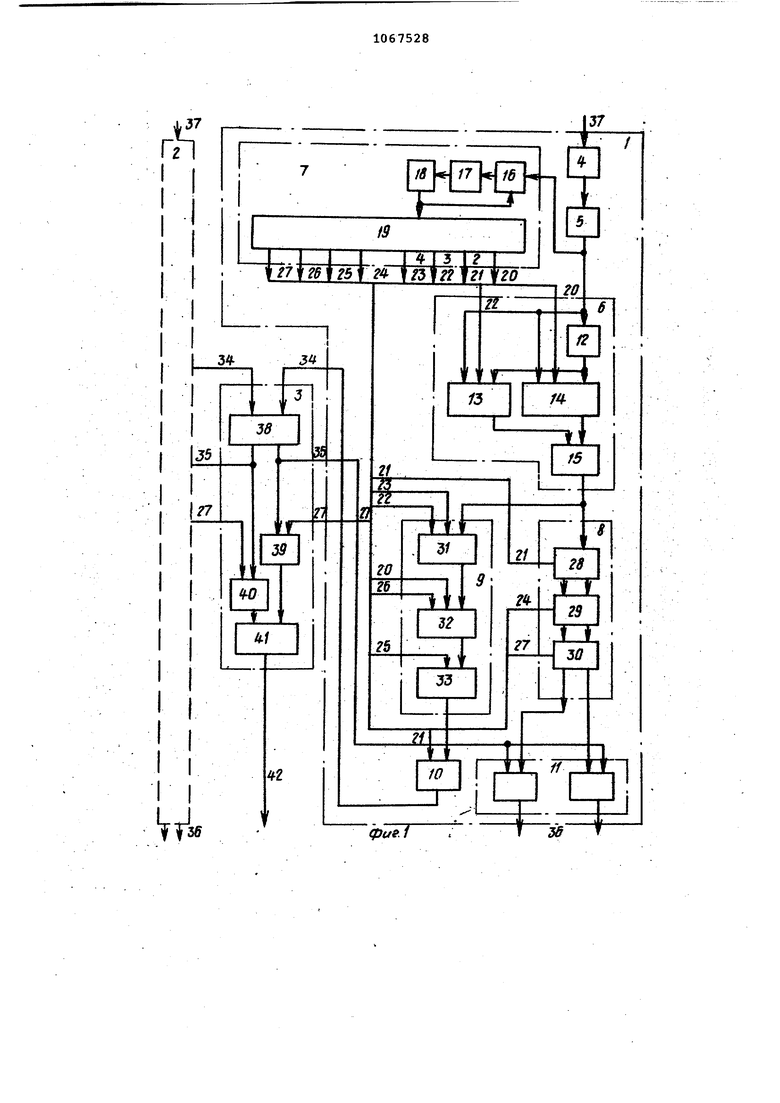

Изобретение относится к вычислительной технике и предназначено для использования в запоминающих устройствах с магнитньм носителем, запись информации в которые производится способом частотной модуляции (4м) по двум каналам. Известно устройство Для воспроиз ведения цифровой информации, содерхсащее в каждом из двух каналов последовательно, соединенные корректор и ограничитель, подключенный одновременно к фазовому детектору и бло синхронизации, выходы которого соед нены с тактовыми входами фазового детектора, линию задержки и перемножитель элемент И )1, Однако оно имеет низкую верность воспроизведения информации, так как пропускает искаженный сигнал, который возникает из-за дефектов носителя и не иг.1еет элементов, пред назначенных для обнаружения и исправления ошибок. Известно также устройство для ре лизац и способа записи и воспроизве дения информации, содержащее последовательно соединенные накопитель, буферные запоминающие блоки, преобразователи параллельных кодов в последовательный, сдвигающие регистры, элементы И н элементы ИЛИ, а та же последовательно соединенные в каждом канале первый триггер, элемент И и второй триггер, выходом по ключенный к другому входу элемента И 2. Устройство позволяет заменять дефектную часть информации на информацию аналогичного содержания в дублирующем канале, однако при контроле на четность требует записи дополнительного разряда, а также не позволяет обнаруживать двойные ошибки в информационной группе. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для воспроизведения цифровых сигналов содержащее коммутатор и в каждом из двух каналов последовательно соединенные корректор и ограничитель, подключенные к фазовому детектору и блоку синхрони:зации, первый и второ элементы И, соединенные с регистром сдвига и триггером контроля, вх ды которых подключены к выходам фаз вого детектора и блока синхронизации З . Однако известное устройство можно использовать в случае возникн вения фазовых сдвигов входных сигна лов в одном из каналов относительно другого, особенно когда фазовый сдв может изменяться во времени на несколько тактовых интервалов. При этом на выходе появляются ошибки цифрового сигнала. Цель изобретения - повышение верности воспроизведения. Поставленная цель достигается тем, что в устройство для воспроизведения цифровых сигналов, содержащее коммутатор, в каждом из двух каналов последовательно соединенные корректор и ограничитель, выходом подключенный к информационному входу фазового детектора и ко входу блока синхронизации, выходы первых и вторых нечетных импульсов которого соединены с тактовыми входами фазового детектора, первый триггер контроля и первый регистр .сдвига, информационные входы которых подключены к выходу фазового детектора, входы синхронизации и сброса первого триггера контроля соединены соответственно с выходами вторых четных и вторых нечетных импульсов блока синхронизации, выход первых четных импульсов которого соединен с такто 8ым входом первого регистра сдвига, первый и второй элементы И, одни входы которых соединены соответственно с управляющим выходом коммутатора ,и с выходом первых четных импульсов блока синхронизации, а информационный вход коммутатора подключен к выходу второго элемента И, введены в каждом канале последовательно соединенные второй и третий регистры и последовательно соединенные второй и третий триггеры контроля, входы вторых регистра и триггера контроля .подключены к выходам первого регистра и первого триггера контроля соответственно, блок синхронизации выполнен с выходами.третьих и четвертых четных и нечетных импульсов, при этом выход первых нечетных импульсов блока синхронизации дополнительно подключен ко входу синхронизации второго триггера контроля, выходы третьих четных и четвертых нечетных импульсов - к входу синхронизации третьего триггера контроля и ко входу сброса второго триггера контроля соответственно,выходы третьих нечетных и четвертых четных, импульсов - к тактовым входам второго и третьего регистров соответственно, а выходы третьего регистра и третьего трипгера контроля соединены соответственно с другими входами первого и второго элементов И. На фиг.1 представлена функциональная схема устройства, на фиг.2 временные диаграммы работы устройства. Устройство для воспроизведения цифровых сигналов сод6р сит ;(фиг. 1) каналы 1 и 2 и коммутатор 3. Каждый из двух каналов содержит последовательно соединенные корректор 4 и ог- раничитель ,5, фазовый детектор 6 и блок 7 синхронизации, регистр 8 сдвига, триггер 9 контроля, элемент И 16 и элемент И 11.

Фазовый детектор б предназначен для выявления изменения фазы входного сигнала, содержит элемент НЕ 12, триггеры 13 и 14 и элемент 15 неравнозначности. Вход элемента НЕ 12 подключен к информационному вход фазового детектора 6 и соединен с К-входами триггеров 13 и 14, а выход с- их У-входами.Выходы триггеров 13 и 14 подключены ко входам элемента 15 неравнозначности.. Входы синхронизации триггеров 13 и 14 подключены соответственно к первому и второму тактовым входам фазового детектора б.

Блок 7 синхронизации содержит последовательно срединенные фазовый деГектор 16, фильтр 17 нижних частот, управляемый генератор 18 и распределитель 19. Выход генератора 18 также соединен с другим входом фазового детектора 16. Вход последнего является входом блока 7, а его выходами являются выходы 20-27 распределителя 19. . .

Регистр 8 сдвига предназначен для выделения цифрового сигнала и его задержки, состоит из трех регистров 28, 29 и 30, соединенных последовательно. При этом регистры имеют тактовые входы, подключенные соответственно к выходам 21, 24 и 27 блока 7 синхронизации. Входом регистра 8 сдвига является вход ступени 28, а выходами являются выходы ступени 30.

Триггер 9 контроля предназначен для выявления отсутствия синхроимпульса и запоминания этого состояния. Он состоит из трех триггеров 31, 32 и 33, соединенных по информационным входам последовательно и ймекнцйх раздельные входы синхронизации. Входы синхронизации триггеров 31, 32 и 33 соответственно подключены к первому, второму и третьему входам синхронизации триггера9 контроля.

Входы сброса триггеров 31 и 32 соответственно соединены с первым И вторым входами сброса триггера 9 контррля. Информационный вход триггера 31 является информационным входом триггера 9 контроля. Выход триггера 33 соединен с выходом триггера 9 контроля..

Сборка элементов И 11 состоит из элементов Н, первые входы которых объединены, а вторые входы подключены соответственно к выходам регистра 8 сдвига.

Выходы блока 7 синхронизации подключены следующим образом.

Выход 20 первых нечетных- импульсов подключен к первому тактовому входу фазового детектора 6 и к входу синхронизации второго триггера 32 контроля. . Выход 21 .первых четных импульсов

соединен с тактовым входом первого регистра 28 сдвига и стробирующим входом второго элемента И 10. Выход

22вторых нечетных импульсов подключен ко второму тактовому входу фазового детектора 6 и входу сброса первого триггера 31 контроля. Выход

23вторых четных импульсов соединен с входом синхронизации последнего. Выход 24 третьих нечетных импульсов подключен к тактовому входу второго регистра 29 сдвига. Выход 25 третьих четных импульсов соединен с входом синхронизации третьего триггера 23 контроля. Выход 26 четвертых нечетных импульсов подключен ко входу сброса второго триггера 32. Выход 27 четвертых четных импульсов соединен с тактовым входом третьего регистра 8 сдвига и тактовым выходом канала .

Выход ограничителя 5 подключен ко входам фазового детектора 6, подключен к информационным входам первых регистра 26 сдвига и триггера 31 контроля. Выход элемента И 10 подключен к управляющему выходу 34 канала. Объединенный вход элемента И 11 соединен со входом 35 блокировки канала. Выходы элемента И 11 являются информацион 1ыми выходами 36 канала. Вход корректора 4 подключен ко входу 37 канала.

KoNB4yTaTop 3 предназначен для блокирования цифрового сигнала на выходе канала и формирования сигнала синхронизации готовности. Коммутатор 3 содержит триггер 38 с разделными входами элементов И 39 и 40 элемента ИЛИ 41. Выходы триггера 38 подключены к первым входам элементов Н 39 и 40 и к управляющим выходам коммутатора 3. Выходы элементов И 39 и 40 соединены со входами элемента ИЛИ 41. Выход последней является выходом 42 синхронизации готовности. Входы триггера 38 подключены к управляющим входам коммутатора 3, а вторые входы элементов П 39 и 40 к его тактовым входам. Тактовый вход коммутатора 3 соединен с тактовым выходом 27 канала. Управляющий в:сод коммутатора 3 подключен к уп- равляющему выходу 34 канала. Управляющий выход коммутатора 3 связан со входом 35 блокировки канала.

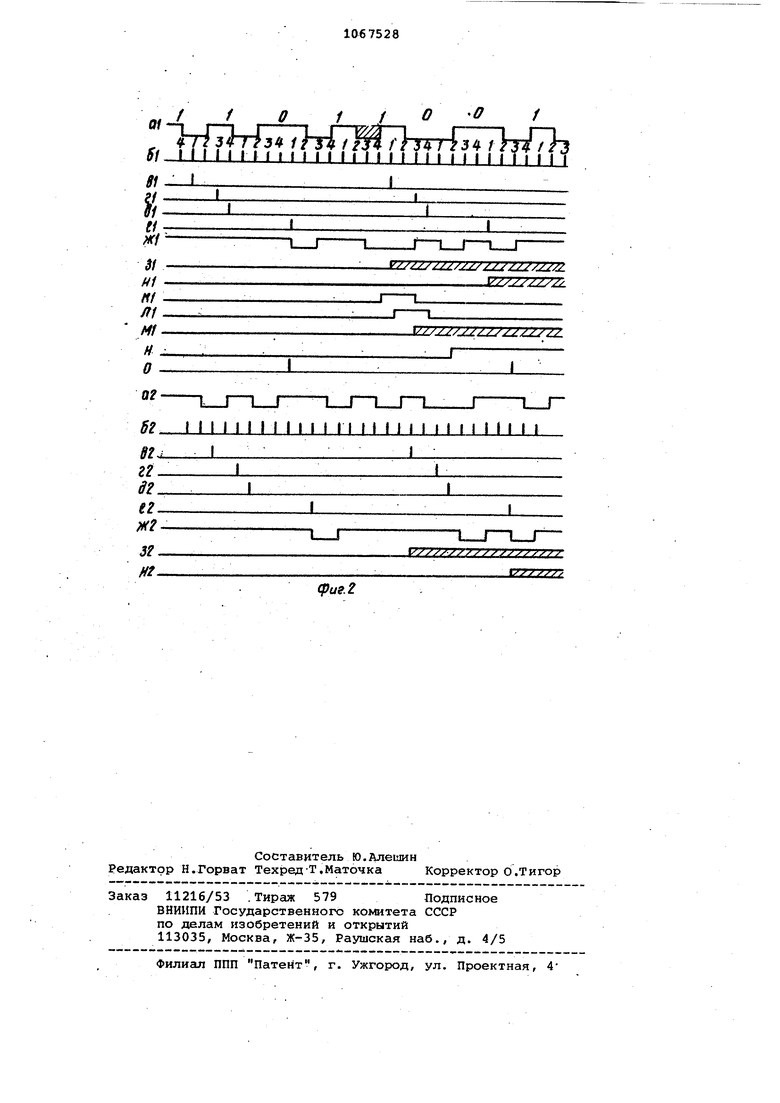

Временные диаграммы, представленные на фиг.2, изображают а1-м1состояния.сигналов в канале 1, а2-и2-состояние сигналов в кангше 2, н-о-состояние сигналов в коммутаторе 3.

При этом (,иг.2 :

al - сигнал на выходе ограничителя 5 (ь1трихом показано искажение сигнала-пропадание .импульса).;

61 - серия нечетных и четных тактов 1-4, выработанная и синхрониэированная в канале 1 блоком 3 синхронизации на выходах 20-23 соответственно;в1, г1/ д1, el - серия тактЫб, работанная блоком 7 синхронизации на эыходах 24-27 соответственно ж1 - сигнал на выходе фазового детектора 6 канала 1; з1 - штрихом - запоминание цифрового сигнала 1101 на втором регистре 29 сдвига канала 1J и1 - штрихом - запоминание цифр вого сигнала на третьем регистре 3 сдвига/ а2-...и2... - аналогичные временные Д1 аграммы для канала 2; к1 - запоминание отсутствия синхроимпульса на первом триггере 31 контроля; л1, м1 - запоминание отсутствия синхроимпульса на втором и третьем триггерах 32 и 33 контроля, н - переключение триггера 38 в коммутаторе 3; о - поступление на выходе 42 сигна а син:хрОнизации готовности. Устройство работает следующим о разом (см.,фиг, 1.2). Воспроизведенный сигнал с магни ного носителя (не показан) поступает На входы 37 каналов 1 и 2. С помощью корректора 4 и ограничит ля 5 входной сигнал формируется в виде прямоугольных импульсов (фиг. al, а2 ), по которым в блоке 7 синх низируется управляемый генератор 1 На тактовых выходах 20-23 блока 7 образуются синхронизированные такт вые импульсы. На выходах 24-27 рас пределитель 19 блока 7 синхронизаци распределяет каждый четвертый такто вый и.мпульс С фиг. 2, в1, 2, 2; д1, el, 2). Первым и вторым нечетными та товыми импульсами, образованными на выходах 20 и 22 (фиг.2 б1, 62 такты 1,3 ) в середине каждого такто вого интервала входного сигнала, стробируются триггеры 13 и 14 запоминания фазы. Схема 15 неравнозначности выдает сигнал изменения фазы (фиг.2ж1, ж2. На выход фазового детектора б. Выход фазового детектора 6 вторично стробируется в начале и в конце тактового интервала. За начало тактового интервала принят момент изменения фазы ЧМ сигнала на границе цифровой позиции (синхроперепад). Результаты стробир вания в начале тактового интервала запоминаются.на первом 28 регистре сдвига 28 fHe показаны). На .примере временной диаграммы (фиг. ) на этом регистре -запоминается цифровой сигнал 1101 за четыре первых четных такта. После этого цифровой сигнал записывается во второй регистр 29 (фиг.2 з1-штрихом), а на первом регистре запоминаются следующие цифровые сигналы. На втором регистре 29 цифровой сигнал задерживается на четыре такта, а после двух тактов передается на третий регистр 30, где запоминается (фиг.2и1-штрихом). На этой ступени цифровой сигнал сохраняется в течение четырех тактов и может быть принят с выхода устройства. Выявление наличия синхроимпульса осуществляется стробированием выходного сигнала фазового детектора б в конце тактового интервала (фиг.1,к1 . Результат стробирования запоминается на первом триггере 31 .контроля, Наличие или отсутствие синхроимпульса за четыре такта стробирования запоминается на втором триггере 32 контроля (фиг.2л1) . Для сохранения сигнала об отсутствии синхроимпульсов в течение CJIeдyющиx тактов и управления коммутатора 3 используется третий триггер 39 контроля (фиг.2м1). Запоминание и задержка цифрового сигнала на втором и третьем регистрах и втором и третьем триггерах контроля позволяют при изменяющемся сдвиге по фазе входного сигнала, на 1-2 тактовых интервала обеспечить своевременное переключение триггера 38 коммутатора 3 (фиг.2н), блокировку поступления искаженного цифрового сигнала на выход устройства элементов И 11 и формирование сигнала синхронизации готовности (фиг.2о). Изобретение позволяет применять устройство для воспроизведения Цифровых сигналов в двухканальных системах с изменяющимся фазовым сдвигом входных сигналов. Проверка, проведенная с помощью лентопротяжного механизма бытового магнитофона Тембр-2М на ленте типа А-4409-6Б и -вычислительной машины Электроника-60, показывает, что несмотря на изменяющийся фазовый сдвиг в пределах 1-2 тактовых интервала, при плотности записи 40бит/мм (рабочая частота 8 кГц и скорость протяжки 19 см/сек) записанная информация воспроизведена безошибочно при имеющихся дефектах ленты на обеих дорожках. Та же информация, воспроизведенная разделыно) по первому или второму каналам, принята с ошибками (несовпадение контрольной суммц|. Применение предлагаемого устройства позволяет Использовать дешевые лентопротяжные механизмы, повысить плотность записи и понизить требования к магнитному носителю.

26

36

(риг1

fi I I И 1 MM М Mt И I И М И И I I I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ воспроизведения цифровых сигналов и устройство для его осуществления | 1980 |

|

SU966728A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для ортогонального преобразования по Уолшу-Адамару | 1988 |

|

SU1571610A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Устройство для воспроизведения цифровой информации | 1984 |

|

SU1167645A1 |

| Устройство для воспроизведения информации с магнитного носителя | 1981 |

|

SU1014017A1 |

| Устройство для передачи и приема дискретных сигналов | 1990 |

|

SU1758894A1 |

| Устройство для быстрого преобразования Уолша в реальном масштабе времени | 1988 |

|

SU1709341A1 |

| Устройство для выполнения быстрого преобразования Уолша-Адамара | 1988 |

|

SU1605254A1 |

| Устройство для воспроизведения информации с магнитного носителя | 1984 |

|

SU1190411A2 |

УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ЦИФРОВЫХ СИГНАЛОВ, содержащее коммутатор, в из двух каналов последовательно соединенные корректор и ограничитель, вы-, ходом подктпоченный к информационному входу фазового детектора и ко входу блока синхронизации, выходы первых и вторых нечетных импульсов которого соединены с тактовыми входами фазового детектора, первый триггер контроля и первый регистр сдвига, информационные входы которых подключены к выходу фазового детектора, входы синхронизации и сброса первого триггера контроля соединены соответственно с выходами вторых четных и вторых нечетных имйульсов блока синхронизации, выход первых четных импульсов которого соединен с тактовым входом первого регистра, сдвига, первый и второй элементы И, одни входы KOTOE JX соединены соответственно с управляющим выходом коммутатотора и с выходом первых четных импульсов блока синхронизации, -а информационный вход коммутатора подключен к выходу второго элемента И, отличающееся тем, что, с целью повышения верности воспроизведения, в него введены в каждом канале последовательно соединенные второй и третий регистры и последовательно соединенные второй и третий триггеры контроля, входы вторых регистра и триггера контроля подключены к выходам первого регистра и первого триггера контроля соответственно, блок синхронизации S выполнен с выходами третьих и четвертых четных и нечетных импульсов, при этом выход первых нечетных импульсов блока синхронизации дополнительно подключен ко входу синхрониза ции второго триггера контроля, выходы третьих четных и четвертых нечетных импульсов - ко входу синхронизации третьего триггера контроля и ко О входу-Сброса второго триггера конт : роля соответственно, выходы третьих нечетных и четвертых четных импульч У1 N0 X) сов - к тактовым входам второго и третьего регистров соответственно, а выходы третьего регистра и тре ьего триггера контроля соединены о соответственно с другими входами пер вого и-второго элементов И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многокканальное устройство для магнитной записи и воспроизведения цифровой информации | 1973 |

|

SU455364A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-01-15—Публикация

1981-12-29—Подача