Изобретение относится к вычисли тельной технике, а именно к анализаторам спектра, работающим на основе обработки временного, сигнала с помощью алгоритма быстрдго преобразования Фурье (БПФ) Известно устройство для вычисления коэффициентов Фурье, содержащее итеративный сдвиговый регистр, основной и дополнительный счетчик адресов оперативного запоминающего устройства (ОЗУ), блок логического .управления и адресный переключатель Недостатком этого устройства является то, что генерирование адресов ОЗУ занимает в этом устройстве как минимум, два такта, не считая времени, необходимого для занесения начального адреса на ЭВК Известен .также анализатор спектра , содержащий первый и второй вход ные регистры, первый, .второй, третий и четвертый перемножители, блок вентилей, первое и второе ОЗУ, постоянное запоминающее устройство, синхронизатор, счетчик числа итераций и счетчик адреса t2 . Недостатком этого аналиэатора яв ляется необходимость сдвига кодов, адресов и ПЗУ на разное .число разрядов в зависимости от нсмера итерации, что приводит к низкому быстродействию аналиэаторд. Наиболее близким по технической сущности к данному устройству является анализатор спектра, содержащий первый и второй входные регистры, первый, второй, третий и четвертый перемножители, блок элементов К, п.ервое и второе ОЗУ, ПЗУ, синхронизатор, первый, второй и третий счетчик, первый и второй компаратор, первый и второй дешифратор, первый и второй мультиплексор, блок вычитания, первый и второй сумматор и группу элементов И Сз.З. Недостатками анализатора являются сложность . схемы устройства и большое количество оборудования. Целью изобретения является упрощение устрой ств:а. Поставленная цель достигается тем, что анализатор спектра, содержащий арифметический блок, первый и второй блоки памяти, блок постоян ной памяти, первую группу элементов И, первый и второй сумматоры, синхронизатор, первый и второй компара торы, первый и второй счетчики, дешифратор причем первый выход синхронизатора подключен к входам элементов И первой группы, выходы которых соединены а адресными входами первого и второго блоков памяти, информационные выходы кото16рых подключены соответственно к входам первого и второго операндов арифметического блока, выходы первого и второго операндов которого соединены с информационными входами соответственно первого и второго блоков памяти, причем информационные входы первого и второго блоков памяти являются соответственно- первьал и вторым информационными входами анализатора, выход первого компаратора соединен с тактовым входом первого счетчика, информационный выход которого соединен с первым входом второго компаратора, выход которого подключен к входу сброс первого счетчика и тактовому входу второго счетчика, информационный выход которого соединен с входом деишфратора, а информационный выход блока постоянной памяти подключен к входу задания коэффициента арифметического блока, содержит вторую группу элементов И и третий счетчик, информационный выход которого подключен к первому входу первого сумматора, первому входу первЬго компаратора, первому входу второго сумматора и вторым входам элементов И второй группы, задаваемого двоичноинверсным адресом с выхода счетчика 14 (;т-е адресом , в котором старшим двоичным разрядом является выход младшего разряда счетчика, а младшим двоичным разрядом выход старшего разряда счетчикд). По окончании операции Бабочка результаты записываются в блоки 8 и 9, импульс с синхронизатора приводит к изменению.адресов операндов операции Бабочка , снова производится операция Бабочка и результаты записываются в блоки 8 и 9 до тех пор, пока не будет обработаны все N отсчетов В той части анализатора, которая обеспечивает адресацию операндов в процессу БПФ происходят следующие процессу Начиная с начального состояния (код на выходе счетчика 13 Е)авен О, код в счетчике 14 (счетчик е) - О, код в с 1етчике 12 (счетчик i ) -О, по каждому импульсу синхронизатора число, находящееся в накапливающем регистре 13, увеличивается на величину (;т,;ев на нулевой итерации увеличивается на два, на первой на четыре и :т, ) , адрес второго операнда формируется на выходе сумматора 20 суммированием кода р выхода счетчика 13 и величины .2, величина 2, так и величина 2 образуются на выходе дешифратрра 17, но для образования числа 2 выходной код дешифратора 17 прямо подается на вход сумматора 20, а на вход сумматора 19 этот же код

поступает со сдвигом па один разряд в сторону старших разрядов, -.ТоВ, вкод нулевого разряда сумматора 19 навсегда устанавливается в ноль, вход первого разряда сумматора 19 соединяется с выходом первого разряда дешифратора 17 и тт.д.. В некоторый момент времени импульс с синхронизатора 11 вызывает изменение числа в счетчике 13 настолько что оно превысит 2 , В этот момент срабатывает компаратор 15 и происходит следующее: появившийся перепад напряжения на выходе компаратора 15 увеличивает на единицу код счетчика 14 (счетчик е) и, в то же самое время разрешает передачу на установо.чные входы счетчика. 13 через трет входы которых подключены к выходу второго сумматора, второй вход которого объединен с згорам входом второго компаратора ..и подклк ч.ен к первому выходу дешифратора, второй выхбд которого соединен с вторым входом первого сумматора, выход которого соединен с информационным входом третьего счетчика, установочный вход которого соединен с выходами элементов и второй группы, первые входы которых соединены -с выходом первого компаратора,второй вход которого является входом задания величины ,N ( К- размер преобразования) , выход первого счетчика соединен с адресньш входом блока постоянной памяти и вторыми входами элементов И второй группы, второй выход синхронизатора соединен с тактовым входом третьего, счетчика, вход Сброс которого подключен к выходу второго компараторд.

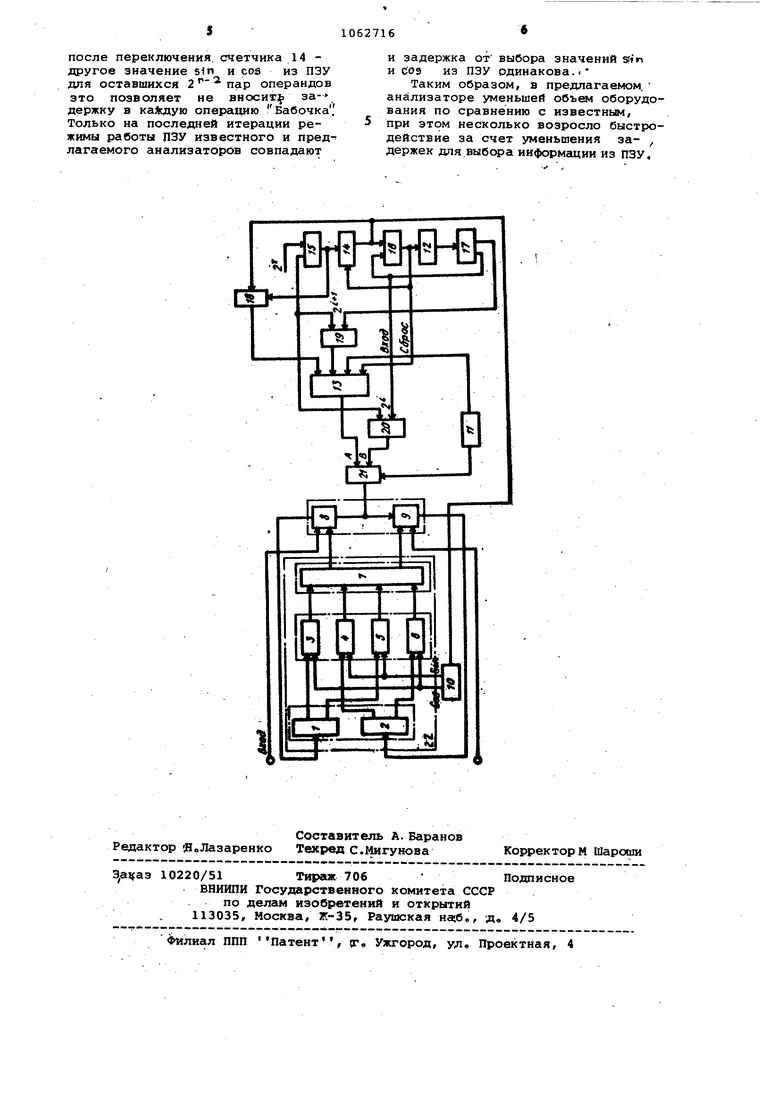

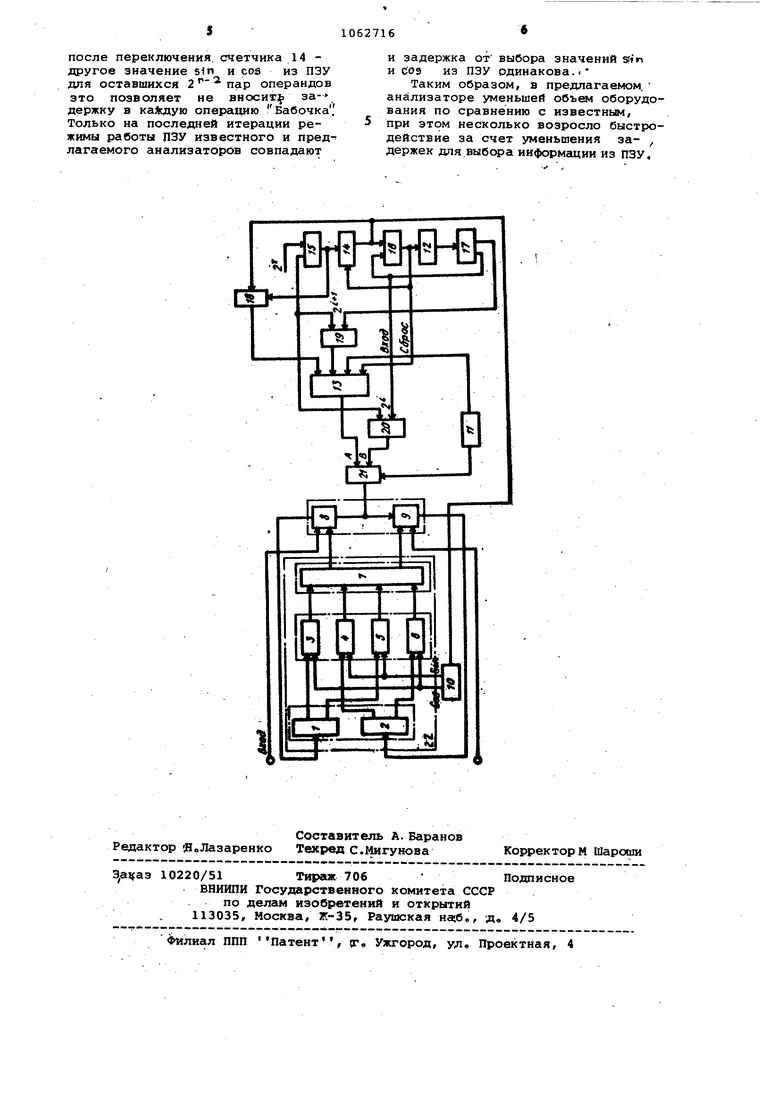

На чертеже приведена функциональная схема устройств в

Анализатор состоит из двух входных регистров 1 и 2, четырех перемножителей 3- - б и группы элементов И арифметического блока 7, двух блоков 8 и 9 памяти(ОЗУ), блока 10 постоянной памяти (ПЗУ), синхронизатора 11, первого счетчика 12, третьего счетчика 13, второг счетчика 14, двух ксялпараторов 15 и 16, дешифратора 17, первой группы

18элементов И, двух сумматоров

19и 20, второй группы 21 элементов И, элементы 1-7 образуют арифметический блок 22...

Анализатор работает .следующим образом.

На входе компаратора 15 фиксируется код, соответствующий величине 2 N , равной числу временных отсчетов в обрабатываемой анализатором выборке. Выборка из N комплексн отсчетов загружается в блоки 8 и 9 По окончании загрузки третий счетчик 13 и счетчики 12 и 14 обнуляютс,я. Далее производится операция Бабочка над отсчетами с номерами, которые указЕтвают выходной код счетчика 13 и сумматора 20, с использованием вектора поворота, элементы И 18 информации с выхода счетчика 14, в счетчике 13 устанавли-, вается код, соответствующий новому (Значению счетчик а 14, и условия для срабатывания компаратора 15 пропадают, выключение компаратора 15 за(

прещает прохождение информации со счетчика 14 на установочные входы счетчика 13 После этого процесс увеличения кода в счетчике 13 по импульсам синхронизатора 11 начинается уже с нового значения, соответствующего новому состоянию счетчика 14, В некоторый момент перепад напряжения с выхода компаратора 15 вызывает такое увеличение кода в счетчике 14, что .он становится равньии величине г тогда на выходе компарат.ора .16 появляется перепад напряжения, который вызывает увеличение на единицу кода в счетчике 12 (счетчик i) и сброс в ноль счетчика 14 и счетчика 13. Последующие импульсы синхронизатора вызывают описанные процессы до тех пор, пока на r-fi выходе дешифратора 17 не появится перепад напряжения, который, служит сигнале для окончания обработки временной реализации из 2 отсчетсрв. По окончании описанного процесса в блоках 8 и 9 находятся отсчеты комплексного мгновенного спектра входного сигнала.

Предлагаемый анализатор и известный генерируют в процессе обработки входного сигнала одинаковые для каждой итерации пары адресов операндов, но в предлагаемом анализаторе адресапар изменяются не моиотонно, как в сх&ле известного, что и дало возможность исключит из схемы два мультиплексора, детаифратор и блок вычитания. Кроме того, предлагаемый анализатор дает и эффект . увеличения быстродействия, что связано со способе формирования адреса ПЗУ, Так на нулевой итерации известный и предлагаемый анализаторы работают одинаково, но уже на первой итерации в известном для каждой новой пара операндов выбирается новое значение sin и соз из ПЭУ, Но ПЗУ обладает конечным быстродействием и каждая операция Бабочка таким образом удлиняется во времеци, В предлагаемом анализаторе на первой итерации для первых операндов выбрано одно значение sin и cos из ПЗУ, а затем

после переключения, счетчика 14 другое значение sin и cos из ПЗУ для оставшихся 2 пар операндов это позволяет не вносит задержку в каждую операцию Бабочка. Только на последней итерации режимы работы ПЗУ известного и предлагаемого анализаторов совпадают

и задержка от выбора значений sin и йоэ из ПЗУ одинакова..

Таким образом, в предлагаемом. анализаторе уменьшей объем оборудования по сравнению с известным, при этом несколько возросло быстродействие за счет уменьшения за- , держек для выбсфа ииформации из ПЗУ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Анализатор спектра | 1979 |

|

SU815664A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для вычисления скользящего спектра | 1983 |

|

SU1095188A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Процессор для быстрого преобразования Фурье | 1989 |

|

SU1633426A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1290350A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

АНАЛИЗАТОР СПЕКТРА, содержащий арифметический блок, первый и второй блоки памяти,, блок постояннрй памяти, первую группу элементов И, первый и второй сумматоры, синхронизатор, первый ,и второй компараторы, первый и второй счетчики, дешифратор,- причем первый выход .синхронизатора подключен к первым входам элементов И первой группы, выходы которых соединены с адресными входами первого и второго блоков памяти, информационные выходы которых подключены соответственно к входам первого и второго операндов арифметического блока, выходу первого и второго операндов которого соединены с информационнь га входами соответственно первого и второго блоков памяти, причем информационные входы первого и второго блоков памяти являются соответственно первым и вторым информационными входами анализатора, выход первого компаратора соединен с тактовым входом первого счетчика, информационный выход которого соединен с первьм входом второго компаратора, выход которого подключен к входу Сброс первого счетчика и тактовому входу второго счетчика, информационный выход кото,рого соединен с входом дешифратора, а информационный выход блока постоянной Псшяти подключен к входу задания коэффициента арифмети, ческогр блока,.отличаювди йс я тем, что, с целью упрощения анализатора, он содержит вторую группу эл@4ентов И и третий счетчик, инфо нлационный выход которого подключен к первому входу первого компаратора, первому входу первого сумматора, первс у входу второго сумматора и вторв входам элементов И первой группы, третьи входе кото(Л рых подключены к выходу второго сукматора, второй вход которого объединен о вторым входом второго компаратора и подключен к. первому выходу дешифратора, второй выход которого соединен с,вторые входом первого сумматора, выход которого соединен с информащюнным входом третьего счетчика, установочный СП) вход которого соединен с выходами tsD эл «ентов И второй группы, первые входы которых соединены с выходом sj первого компаратора, второй вход которого является входом задания сь величины . N(N - размер преобразования) , выход первого счетчика соединен с адресным входом блока постоянной памяти и вторыми входа- ми элементов И второй группы, вто- . рой выход синхронизатора соединен с тактовым входом третьего счетчика, вход Сброс которого подключен к выходу второго компаратора,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-09-24—Подача