1 .1

Изобретение относится к вычислительной технике и может быть использовано при реализации алгоритмов спектрального анализа на специализированных ЭВМ.

Целью изобретения является увеличение быстродействия и точности.

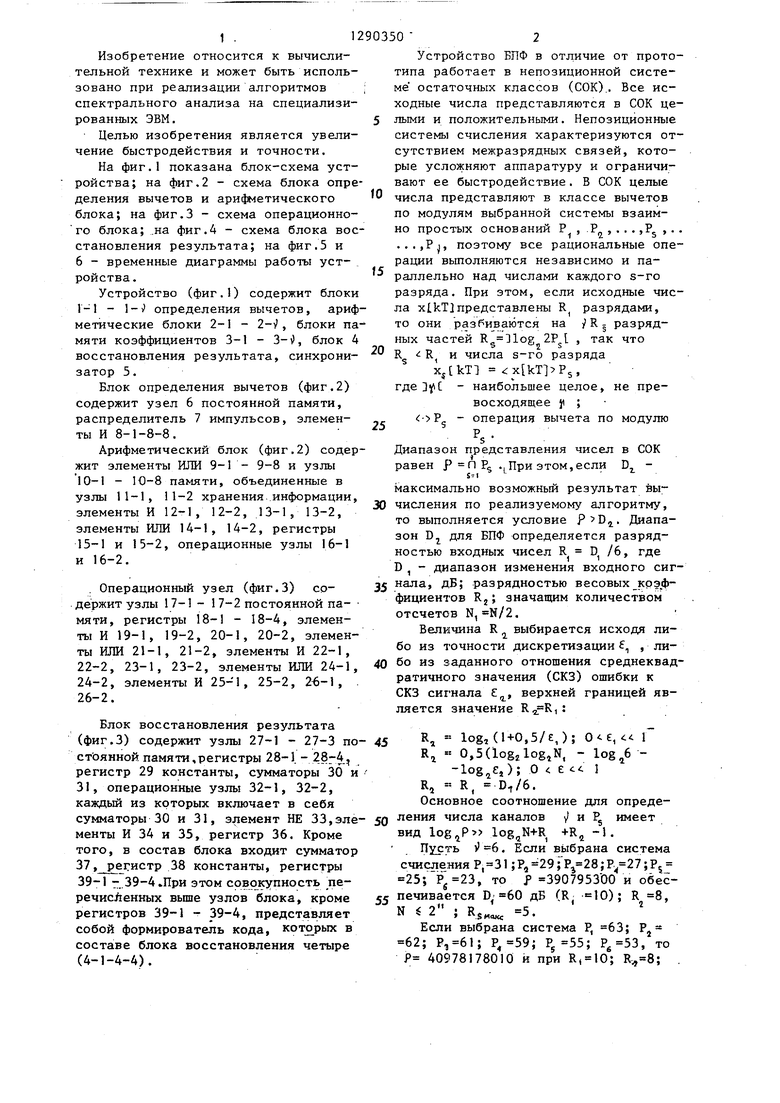

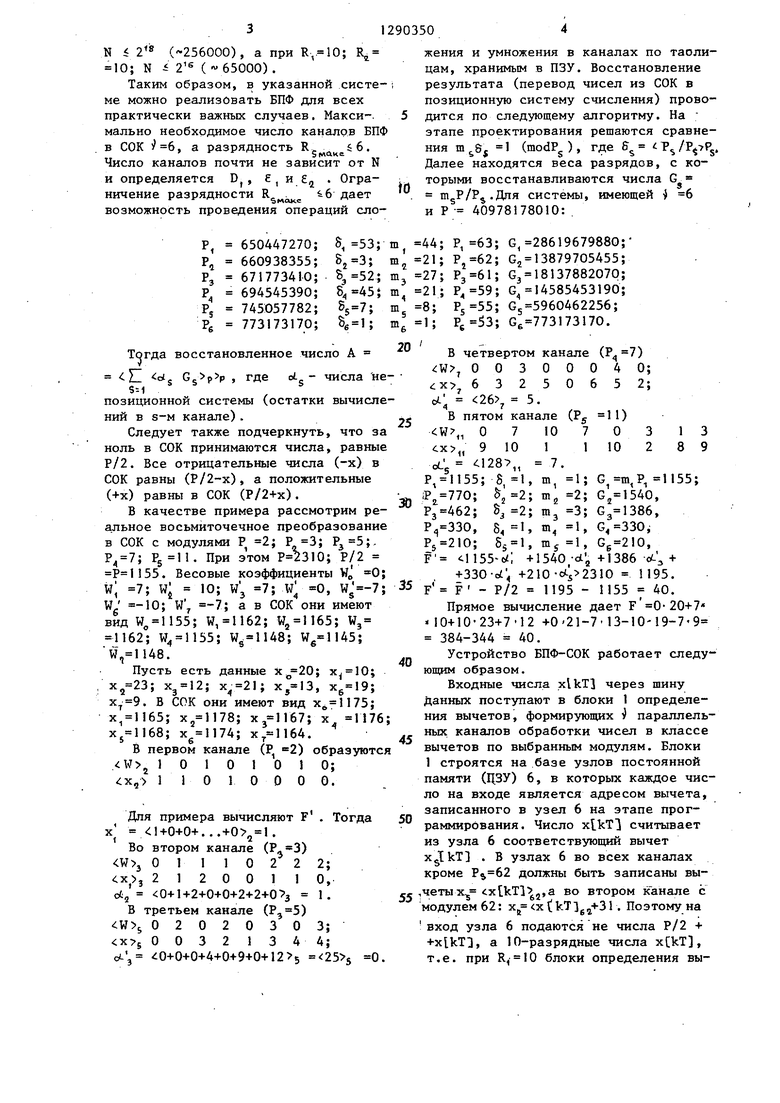

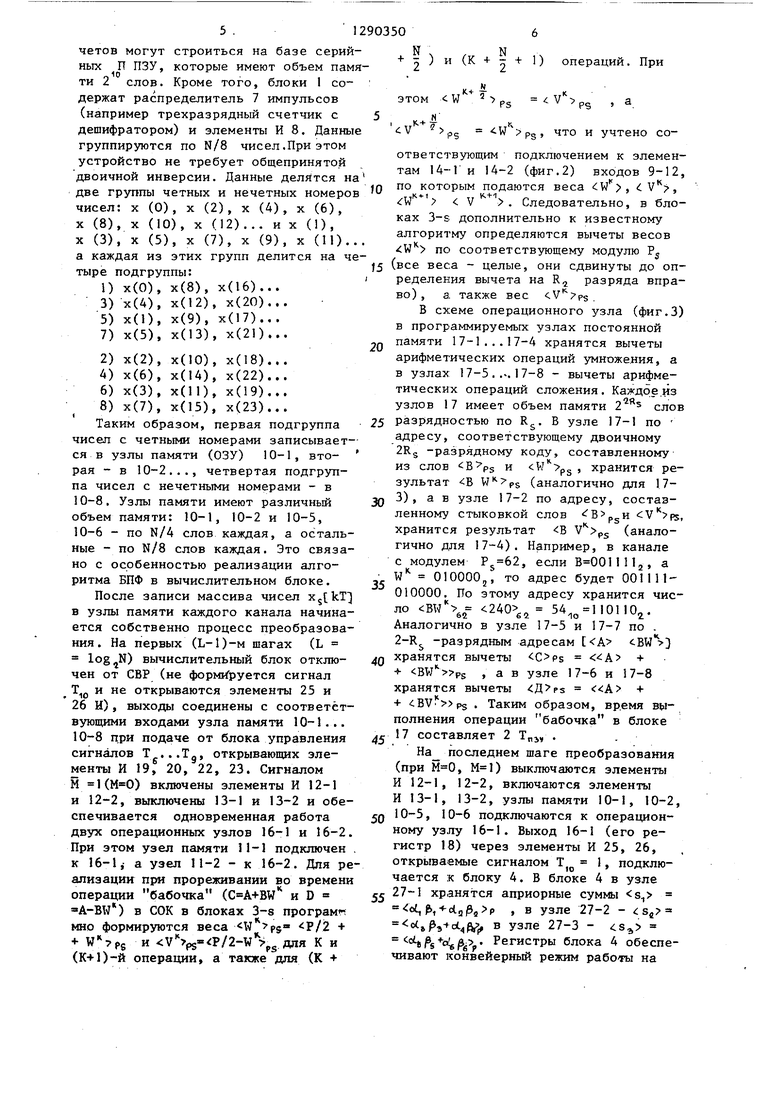

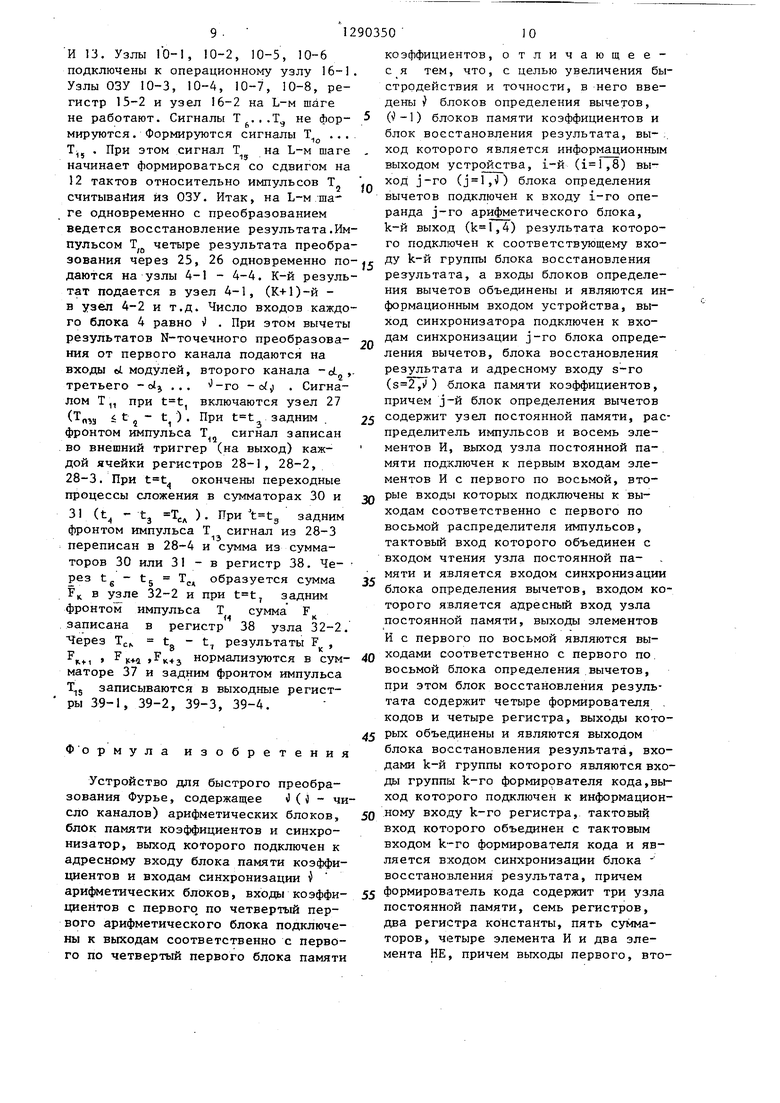

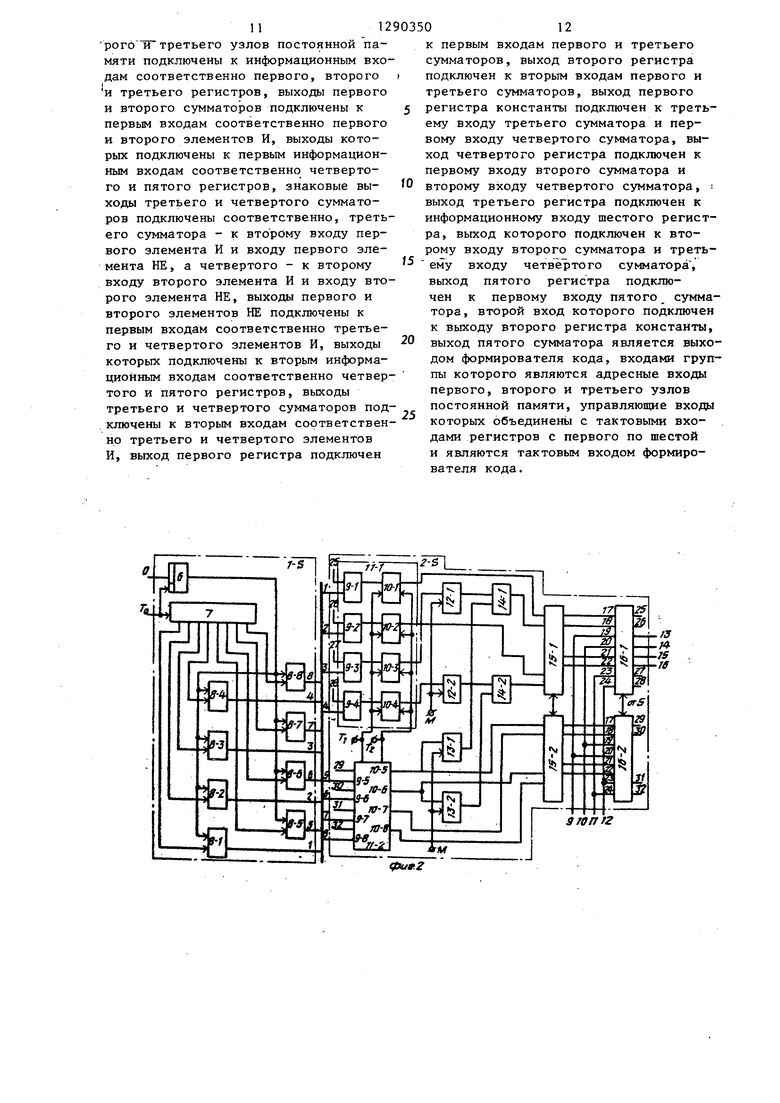

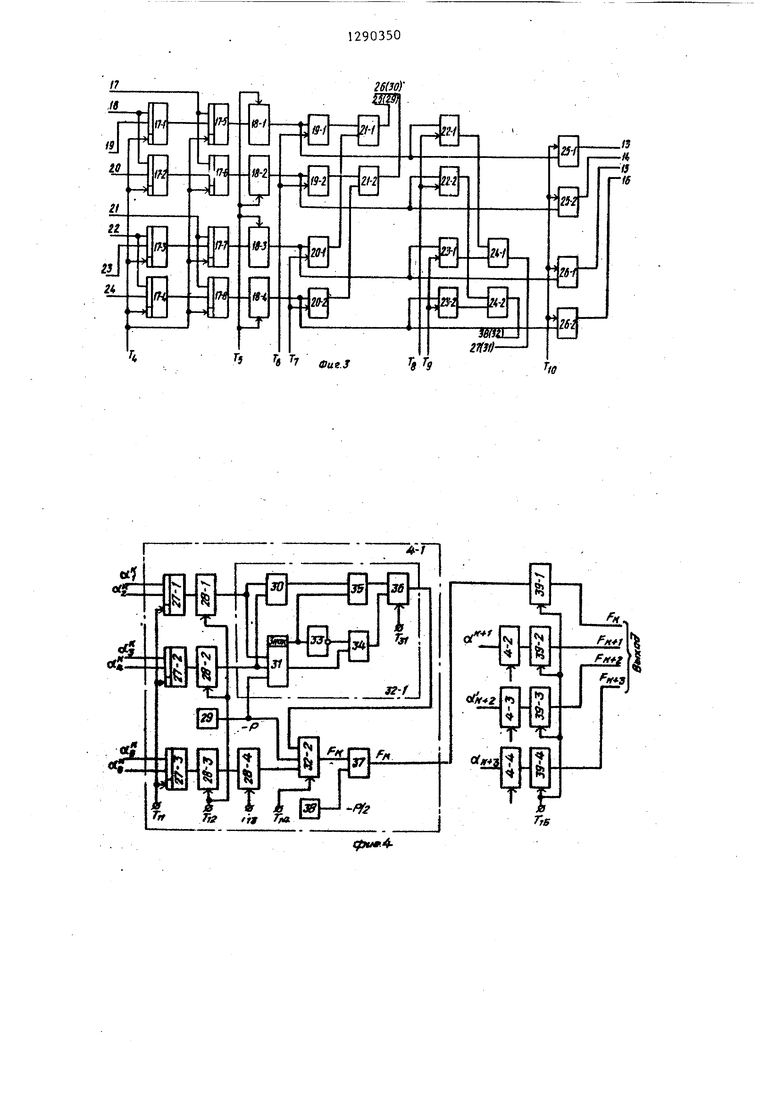

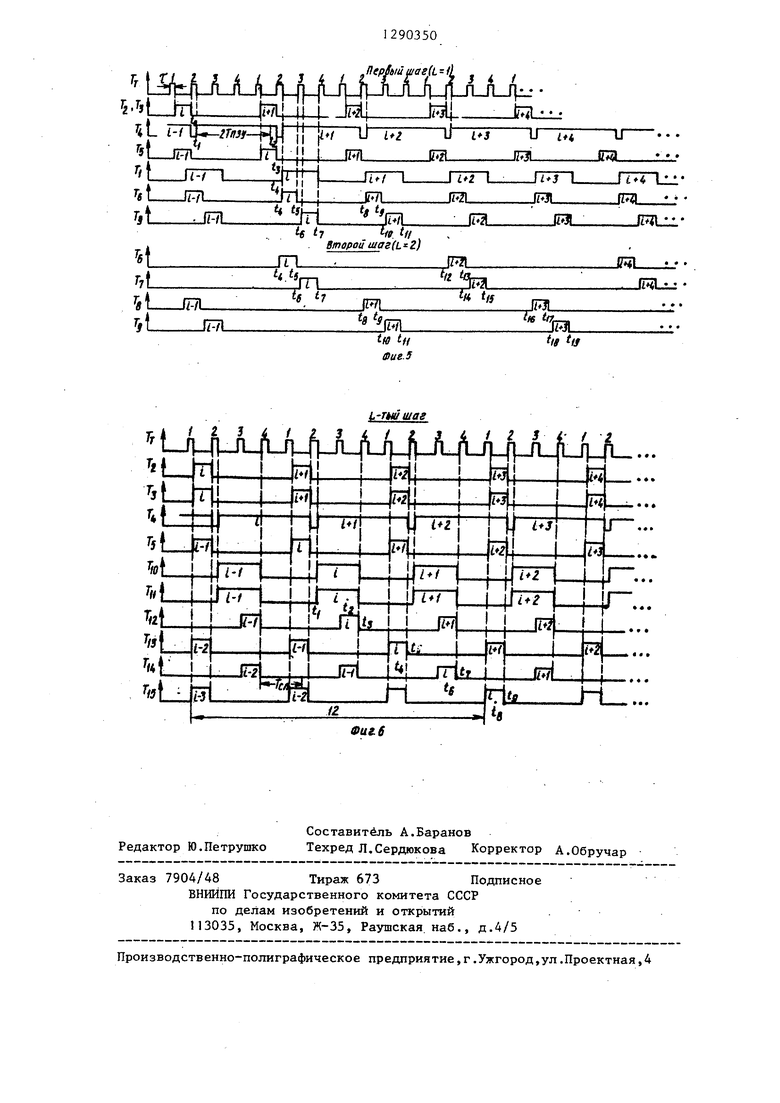

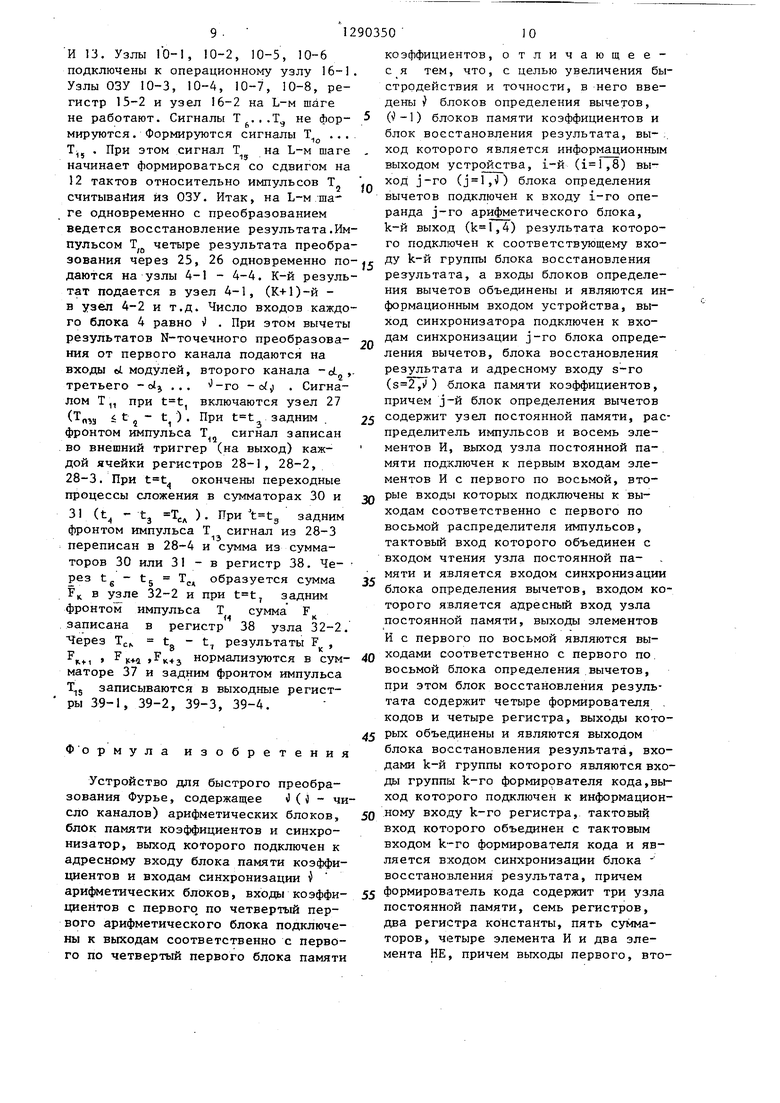

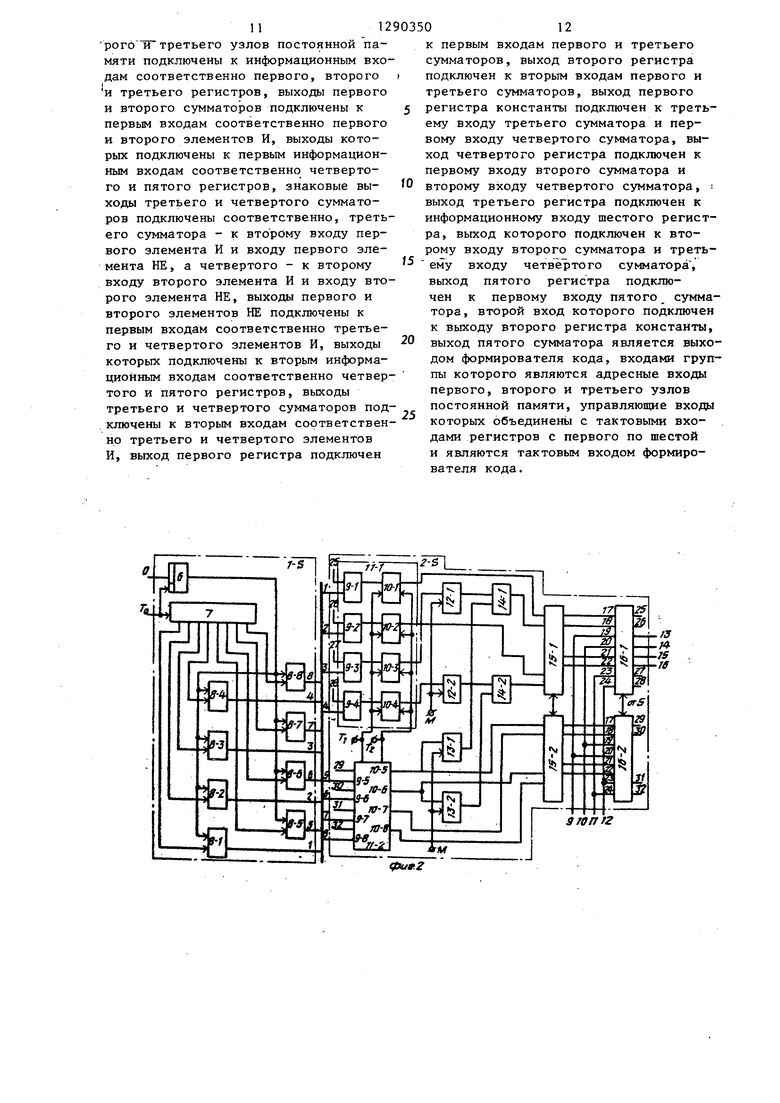

На фиг.1 показана блок-схема устройства; на фиг.2 - схема блока опре деления вычетов и арифметического блока; на фиг.З - схема операционного блока; .на фиг.4 - схема блока восстановления результата; на фиг.З и 6 - временные диаграммы работы устройства.

Устройство (фиг.1) содержит блоки 1-1 - -) определения вычетов, арифметические блоки 2- - 2-), блоки памяти коэффициентов 3-1 - 3-i), блок 4 восстановления результата, синхронизатор 5.

Блок определения вычетов (фиг.2) содержит узел 6 постоянной памяти, распределитель 7 импульсов, элементы И 8-1-8-8.

Арифметический блок (фиг,2) содержит элементы ИЛИ 9-1 - 9-8 и узлы 10-1 - 10-8 памяти, объединенные в узлы 11-1, 11-2 хранения, информации элементы И 12-1, 12-2, 13-1, 13-2, элементы ИЛИ 14-1, 14-2, регистры 15-1 и 15-2, операционные узлы 16-1 и 16-2.

. Операционный узел (фиг.З) содержит узлы 17-1 - 1 7-2 постоянной па- мяти, регистры 18-1 - 18-4, элементы И 19-1, 19-2, 20-1, 20-2, элементы ИЛИ 21-1, 21-2, элементы И 22-1, 22-2, 23-1, 23-2, элементы ИЛИ 24-1, 24-2, элементы И 25-4, 25-2, , 26-2.

Блок восстановления результата (фиг.З) содержит узлы 27-1 - 27-3 по- стоянной памяти,регистры 28-1. - 28-4, регистр 29 константы, сумматоры 30 и 31, операционные узлы 32-1, 32-2, каждый из которых включает в себя сумматоры 30 и 31, элемент НЕ 33,эле- менты И 34 и 35, регистр 36. Кроме того, в состав блока входит сумматор 37, регистр 38 константы, регистры 39-1 - 39-4 .При этом совокупность пе- речисЛенных выше узлов блока, кроме регистров 39-1 - 39-4, представляет собой формирователь кода, в составе блока восстановления четыре (4-1-4-4).

Устройство БПФ в отличие от прототипа работает в непозиционной системе остаточных классов (СОК).. Все исходные числа представляются в СОК целыми и положительными. Непозиционные системы счисления характеризуются отсутствием межразрядных связей, которые усложняют аппаратуру и ограничивают ее быстродействие. В СОК целые числа представляют в классе вычетов по модулям выбранной системы взаимно простых оснований Р , .Р ,. . . ,Р ,. . ...,Р, поэтому все рациональные операции выполняются независимо и параллельно над числами каждого s-ro разряда. При этом, если исходные чис0

разрядами, jR разряд5

ла xLkT представлены R

то они разбиваются на

ных частей , так что

R R и числа s-ro разряда

, - наибольшее целое, не превосходящее ц ; - операция вычета по модулю

PS- Диапазон представления чисел в СОК

равен Р П Р .При этом,если D. 40

45 50 55

максимально возможный результат вы- 30 числения по реализуемому алгоритму, то выполняется условие P D. Диапазон DJ для БПФ определяется разрядностью входных чисел R D /6, где D , - диапазон изменения входного сиг j нала, дБ; разрядностью весовых коgj})- фициентов RJ; значащим количеством отсчетов N,N/2.

Величина R выбирается исходя либо из точности дискретизации f, , либо из заданного отношения среднеквадратичного значения (СКЗ) ошибки к СКВ сигнала , верхней границей является значение ,:

R, log,(l+0,5/e,); О ,: Г RJ « O.Sdogjlog N, - log,6 -log Ct); 0 e c I R, - R, Di/6. Основное соотношение для определения числа каналов V и Р имеет вид log,P log,jN-t-R -i-Rj -1.

. Если выбрана система счисле ния Р,31 ;P,29; P 28;P 27;Pj 25; , то f 390795300 и обеспечивается D; 60 дБ (R, N « 2 ; R

8иакс

-5.

10); ,

Если выбрана система Р, 63; Р- 62; Р,61; Р 55; , то Р 40978178010 и при R,10; R,8;

.312

N i 2 (256000), a при К,-10; R 10; N i 2 (- 65000).

Таким образом, в указанной систе- ме можно реализовать БПФ для всех практически важных случаев. Макси-. мально необходимое число каналов БПФ в СОК , а разрядность R Число каналов почти не зависит от N

е, и.е.

. Огра- 6 дает возможность проведения операций слои определяется D ничение разрядности R

6 макс

Р, 650447270; S, 53; т, 44; Р, 63; G, 28619679880;

Ы, 0+1+2+0+0+2+2+0 з 1.

В третьем канале (P,5) 02020303; 00321344; 0+0+0+4+0+9+0+12 5

жения и умножения в каналах по таоли- цам, хранимым в ПЗУ. Восстановление результата (перевод чисел из СОК в позиционную систему счисления) проводится по следующему алгоритму. На ; этапе проектирования решаются сравнения , 1 (modPg), где & . Далее находятся веса разрядов, с коto

торыми восстанавливаются числа G. ШдР/Р.Дпя системы, имеющей 6 и Р 40978178010:

55

,четых ,a во втором к анале с модулем 62: Xj х ( kT 3g,+31 . Поэтому на

вход узла 6 подаются не числа Р/2 + +xlkT;, а 10-разрядные числа xCkT, т.е. при R,IO блоки определения вычетов могут строиться на базе серий- ньт IT ПЗУ, которые имеют объем памяти 2 слов. Кроме того, блоки 1 со- держат распределитель 7 импульсов (например трехразрядный счетчик с дешифратором) и элементы И 8. Данные группируются по N/8 чисел .При этом устройство не требует общепринятой двоичной инверсии. Данные делится на две группы четных и нечетных номеров чисел: х (О), х (2), к (А), х (6), X (8), X (10), X (12)... и X (1), X (3), X (5), X (7), X (9), X (11)...

I ) и (К . f .

1)

операций. При

этом ; W

К.+ яPS

тт

V

PS

N

cV

ч-ж

ps

, что и учтено соШ

ответствующим подключением к элементам 14-1 и 14-2 (фиг.2) входов 9-12, по которым подаются веса w, 1 V, V . Следовательно, в блоках 3-S дополнительно к известному

алгоритму определяются вычеты весов

-cW по соответствующему модулю Р, а каждая из этих групп делится на че- /- а

.1 (.все веса - целые, они сдвинуты до оптыре подгруппы:

I) х(0), х(8), х(16)...

3)х(4), х(12), х(20)...

5)х(1), х(9), х(17)...

7)х(5), х(13), х(2)...

2) х(2), х(10), х(18)...

4)х(6), х(14), х(22)...

6)х(3), х(11), х(19)...

8)х(7), х(15), х(23)... Таким образом, первая подгруппа

чисел с четными номерами записывает-- ся в узлы памяти (ОЗУ) 10-1, вто- рая - в 10-2..., четвертая подгруппа чисел с нечетными номерами - в 10-8. Узлы памяти имеют различный объем памяти: 10-1, 10-2 и 10-5, 10-6 - по N/4 слов каждая, а остальные - по N/8 слов каждая. Это связано с особенностью реализации алгоритма БПФ в вычислительном блоке.

После записи массива чисел в узлы памяти каждого канала начинается собственно процесс преобразования. На первых (Ь-1)-м шагах (L log N) вычислительный блок отключен от СВР (не формируется сигнал и не открываются элементы 25 и 26 Н), выходы соединены с соответствующими входами узла памяти 10-J... 10-8 цри подаче от блока управления сигналов Т ...Тд, открывающих элементы И 19, 20, 22, 23. Сигналом М 1() включены элементы И 2-1 и 12-2, выключены 13-1 и 13-2 и обеспечивается одновременная работа двух операционных узлов 16-1 и 16-2. При этом узел памяти 11-1 подключен . к 16-1,- а узел 11-2 - к 16-2. Для реализации при прореживании во времени операции бабочка (C A+BW и D «A-BW) в СОК в блоках 3-8 программ МНС формируются веса W ps l2 + WSps и vSps P/2-W%s для К и (К+1)-й операции, а также для (К +

20

ределения вычета на R разряда вправо) , а также вес

В схеме операционного узла (фиг.З) в программируемых узлах постоянной памяти 17-1...17-4 хранятся вычеты арифметических операций умножения, а в узлах 17-5... 17-8 - вычеты арифметических операций сложения. Каждое из узлов 17 имеет объем памяти 2 слов 25 разрядностью по R. В узле 17-1 по адресу, соответствующему двоичному 2Rg -разрядному коду, составленному из слов и , хранится результат В (аналогично для 17- 3), а в узле 17-2 по адресу, состав30

ленному стыковкой слов ps, хранится результат В (аналогично ДД1Я 17-4). Например, в канале

35

с модулем , если В 001П1 W 010000

2

ТО адрес будет 00111140

45

010000. По этому адресу хранится число BWS 240 54 110110. Аналогично в узле 17-5 и 17-7 по . 2-R -разрядным адресам А cBW V} хранятся вычеты :А + + , а в узле 17-6 и 17-8 хранятся вычеты «А + + . Таким образом, время выполнения операции бабочка в блоке 17 составляет 2 Т, .

На последнем щаге преобразования (при , ) выключаются элементы И 12-1, 12-2, включаются элементы И 13-1, 13-2, узлы памяти 10-1, 10-2, 10-5, 10-6 подключаются к операционному узлу 16-1. Выход 16-1 (его регистр 18) через элементы И 25, 26, открьгааемые сигналом Т 1, подключается к блоку 4. В блоке 4 в узле ее 27-1 хранятся априорные суммы s оЦЭ,-«-с(. В узле 27-2 - Sj s- ot ftr , в узле 27-3 - s,,- Регистры блока 4 обеспечивают конвейерный режим работы на

50

50

I ) и (К . f .

6

1)

операций. При

; W

К.+ яPS

тт

V

PS

, что и учтено со

ответствующим подключением к элементам 14-1 и 14-2 (фиг.2) входов 9-12, по которым подаются веса w, 1 V, V . Следовательно, в блоках 3-S дополнительно к известному

0

ределения вычета на R разряда вправо) , а также вес

В схеме операционного узла (фиг.З) в программируемых узлах постоянной памяти 17-1...17-4 хранятся вычеты арифметических операций умножения, а в узлах 17-5... 17-8 - вычеты арифметических операций сложения. Каждое из узлов 17 имеет объем памяти 2 слов 5 разрядностью по R. В узле 17-1 по адресу, соответствующему двоичному 2Rg -разрядному коду, составленному из слов и , хранится результат В (аналогично для 17- 3), а в узле 17-2 по адресу, состав0

ленному стыковкой слов ps, хранится результат В (аналогично ДД1Я 17-4). Например, в канале

5

с модулем , если В 001П1 W 010000

2

ТО адрес будет 0011110

5

010000. По этому адресу хранится число BWS 240 54 110110. Аналогично в узле 17-5 и 17-7 по . 2-R -разрядным адресам А cBW V} хранятся вычеты :А + + , а в узле 17-6 и 17-8 хранятся вычеты «А + + . Таким образом, время выполнения операции бабочка в блоке 17 составляет 2 Т, .

На последнем щаге преобразования (при , ) выключаются элементы И 12-1, 12-2, включаются элементы И 13-1, 13-2, узлы памяти 10-1, 10-2, 10-5, 10-6 подключаются к операционному узлу 16-1. Выход 16-1 (его регистр 18) через элементы И 25, 26, открьгааемые сигналом Т 1, подключается к блоку 4. В блоке 4 в узле е 27-1 хранятся априорные суммы s оЦЭ,-«-с(. В узле 27-2 - Sj s- ot ftr , в узле 27-3 - s,,- Регистры блока 4 обеспечивают конвейерный режим работы на

0

L-м шаге. Вычеты s. в узлах 27-1 и 27-2 подаются в логическую схему, состоящую из сумматоров 30 и 31 и двух элементов И 34, 35. Если Sj + + Sj I (Р хранится в регистре 29), то в знаковом разряде сумматора 31 - единица, открыт элемент И 35 и сумма :s + S, р считывается в регистр 38. Если же S + s выходят за пре- . делы Р, то в знаковом разряде сумматора 31 - ноль, открыт элемент 35 и число s, + s Р s, + считывается в регистр 38. Аналогично ра ботает узел 32-2. Специфическое представление О через Р/2 требует при восстановлении нормализации чисел. Из числа F на выходе узла 32-2 вычитается Р/2 (-Р/2 хранится в регистре 36) в сумматоре 37. Здесь же результат нормируется сдвигом запятой

2 запускается сигнал Т выборки крисi талла ПЗУ-. Длительность Т такова,

Я

что при t t преобразование в ПЗУ закончено и результат преобразования записывается в регистр 18 импульсами

во время от tj до t.

При t ре10

15

20

зультаты преобразования по восьми точкам записаны в регистр 18. При включается сигнал разрешения записи в ОЗУ. На первом шаге при включаются по очереди элементы И 19 и 23 импульсами Tg и Тд в обоих операционных узлах 16-1 и 16-2. При этом сигналы от 19-1 через 21-1 записываются в узлы 10-1 (10-5), от 19-2 через 21-2 - в узел 10-2 (10-6), от 23-1 через 24-1 - в узел 10-3 (10-7), от 23-2 через 24-2 - в узел 10-4(10- 8). Т и Т- включаются последовательна R разряда влево. Четыре одинако- вых модуля СВР использованы для одновременной обработки 4-х чисел oCg ,

к-и

к+2 7

НО при t. ,t.,t-,t,, и т.д. на всех такЯЬотО f. « , . .

тах первого шага. При L 2 подача импульсов Т,...Tg не меняется. Изменяется лишь логика подачи сигналов

с выхода каждого ка-25 з втором шаге при L 2

при включается Tg, результат преобразования считывается из 18-1, 18-2 в 10-1,10-2 (10-5, 10-6). При включается Т, результат пре- у. образования считывается из 18-3,18-4 через 20-1, 20-2 снова в 10-1, 10-2 (10-5, 10-6). При включается Т , результат преобразования считывается 1из 18-1, 18-2 через 22-li 22-2 в узI it л .

cis , s ,ci.s

нала. Результаты преобразований F,

к-ь, регистров 39 ;считываются на выход устройства БПФ- СОК.

Рассмотрим временные диаграммы работы устройства. Всего шагов преобразования N. На первых шагах преобразования от 1 до L - 1 в синхронизаторе сигнал (), а на - сигнал (). Сигнал обеспечивает одновременное считьшание восьми сигналов из всех узлов памяти (ОЗУ) сигналом Т. Формируемые одновременно сигналы Tj являются сигналами записи в регистр 15 Т и Tj запускаются от заднего фронта Т. Период импульсов синхронизации Т выбран так, что Т - ЗТ- 0.,, Т,„ 0,5 Т„„ 0,5 Т,,.., где Т. Т, Т,, . Т - длительность импульсов синхронизации;

Т - время записи в регистр передачи данных;

- время срабатывания ключей; Т.,.. - время обращения к ОЗУ;

время считывания из ОЗУ; время записи в ОЗУ; TOJ - время сложения; Т„., - время считьтания из ПЗУ.

При сигналы из ОЗУ записаны в регистр 15 и, следовательно, подключены к информационным входам узлов 17. При t t, от Т -импульса

35

40

014

ап

лы 10-3, 10-4 (10-7, 10-8). При , включается Т, результат преобразования считывается, из 18-3, 18-4 снова в узлы 10-3, 10-4 (10-7, 10-8). - Таким образом, на втором шаге формируется последовательность импульсов .. .TgT TgTgTgT TgTg. . . На третьем шаге эта управляющая последовательность имЪет вид . .. Т J, Т,Т . , Т Т ..., на четвертом шаге... Т,Т,Т,Т,Т,Т,Т,Т,Т,ТдТ,ТдТ8ТзТ,ТзТ,Т,

,,т,,,т,т,ТдХ,:..

и т.д. Наконец, на (L-1) шаге вклю- чаются лишь Т и Т . и число включений каждого из них равно N/8. Тогда после (L-l)-ro шага результаты преобразований будут записаны только в узлы 10-1, 10-2 и 10-5, 10-6. Поэтов му объем памяти этих узлов составляет N/4 слов в каждой секции. Объем памяти каждой из остальных узлов равен N/8. объем ОЗУ в каждом канапе составляет 1,5N,

На L-M шаге сигнал . Выключены элементы И 12, включены элементы

50

55

2 запускается сигнал Т выборки кристалла ПЗУ-. Длительность Т такова,

Я

что при t t преобразование в ПЗУ закончено и результат преобразования записывается в регистр 18 импульсами

во время от tj до t.

При t ре

зультаты преобразования по восьми точкам записаны в регистр 18. При включается сигнал разрешения записи в ОЗУ. На первом шаге при включаются по очереди элементы И 19 и 23 импульсами Tg и Тд в обоих операционных узлах 16-1 и 16-2. При этом сигналы от 19-1 через 21-1 записываются в узлы 10-1 (10-5), от 19-2 через 21-2 - в узел 10-2 (10-6), от 23-1 через 24-1 - в узел 10-3 (10-7), от 23-2 через 24-2 - в узел 10-4(10- 8). Т и Т- включаются последовательНО при t. ,t.,t-,t,, и т.д. на всех так5

0

лы 10-3, 10-4 (10-7, 10-8). При , включается Т, результат преобразования считывается, из 18-3, 18-4 снова в узлы 10-3, 10-4 (10-7, 10-8). - Таким образом, на втором шаге формируется последовательность импульсов .. .TgT TgTgTgT TgTg. . . На третьем шаге эта управляющая последовательность имЪет вид . .. Т J, Т,Т . , Т Т ..., на четвертом шаге... Т,Т,Т,Т,Т,Т,Т,Т,Т,ТдТ,ТдТ8ТзТ,ТзТ,Т,

,,т,,,т,т,ТдХ,:..

и т.д. Наконец, на (L-1) шаге вклю- чаются лишь Т и Т . и число включений каждого из них равно N/8. Тогда после (L-l)-ro шага результаты преобразований будут записаны только в узлы 10-1, 10-2 и 10-5, 10-6. Поэтов му объем памяти этих узлов составляет N/4 слов в каждой секции. Объем памяти каждой из остальных узлов равен N/8. объем ОЗУ в каждом канапе составляет 1,5N,

На L-M шаге сигнал . Выключены элементы И 12, включены элементы

0

5

И 13. Узлы 10-1, 10-2, 10-5, 10-6 подключены к операционному узлу 16-1. Узлы ОЗУ 10-3, 10-4, 10-7, 10-8, регистр 15-2 и узел 16-2 на L-M шаге не работают. Сигналы 1... не фор- 5 мируются. Формируются сигналы Т ... T;ij . При этом сигнал Т на L-M шаге , начинает формироваться со сдвигом на 12 тактов относительно импульсов Т , считывания из ОЗУ. Итак, на L-M шаге одновременно с преобразованием ведется восстановление результата.Импульсом Т четыре результата преобракоэффициентов, отличающее с я тем, что, с целью увеличения стродействия и точности, в него вв дены блоков определения вычетов, (-1) блоков памяти коэффициентов и блок восстановления результата, выход которого является информационны выходом устройства, i-й (,8) вы ход j-ro (,J) блока определения вычетов подключен к входу i-ro опе ранда j-ro арифметического блока, k-й выход (,4) результата котор го подключен к соответствующему вх

зования через 25, 26 одновременно по-j ДУ k-й группы блока восстановления

даются на узлы 4-1 - 4-4. К-й результат подается в узел 4-1, (К+1)-й - в узел 4-2 и т.д. Число входов каждо го блока 4 равно J . При этом вычеты результатов N-точечного преобразования от первого канала подаются на входы «А модулей, второго канала «А , третьего - otj ... J-ro -d . Сигналом Т,, при , включаются узел 27 t 4 t, ) ПР задним . фронтом импульса Т сигнал записан во внешний триггер (на выход) каждой ячейки регистров 28-1, 28-2, 28-3. При окончены переходные процессы сложения в сумматорах 30 и

31 (t - tj T ). При задним фронтом импульса Т сигнал из 28-3 переписан в 28-4 и сумма из сумматоров 30 или 31 - в регистр 38. Че20

30

результата, а входы блоков определ ния вычетов объединены и являются формационным входом устройства, вы ход синхронизатора подключен к вхо дам синхронизации j-ro блока опред ления вычетов, блока восстановлени результата и адресному входу s-ro (,1) блока памяти коэффициентов причем j-й блок определения вычето

25 содержит узел постоянной памяти, р пределитель импульсов и восемь эле

ментов И, выход узла постоянной па мяти подключен к первым входам эле ментов И с первого по восьмой, вто рые входы которых подключены к выходам соответственно с первого по восьмой распределителя импульсов, тактовый вход которого объединен с входом чтения узла постоянной памяти и является входом синхронизац блока определения вычетов, входом торого является адресный вход узла постоянной памяти, выходы элементо И с первого по восьмой являются вы ходами соответственно с первого по восьмой блока определения вычетов, при этом блок восстановления резул тата содержит четыре формирователя кодов и четыре регистра, выходы ко

рез

Ч ел

образуется сумма

F в узле 32-2 и при , задним фронтом импульса Т сумма F записана в регистр 38 узла 32-2. Через TC tg - t, результаты F , FH,., F K-w к+з нормализуются в сумматоре 37 и задним фронтом импульса 1,5 записываются в выходные регистры 39-1, 39-2, 39-3, 39-4.

Формула изобретения

Устройство для быстрого преобразования Фурье, содержащее J(J - число каналов) арифметических блоков, блок памяти коэффициентов и синхронизатор, выход которого подключен к адресному входу блока памяти коэффициентов и входам синхронизации

блока восстановления результата, входами k-й группы которого являются входы группы k-ro формирователя кода,выход которого подключен к информационному входу k-ro регистра, тактовый вход которого объединен с тактовым входом k-ro формирователя кода и является входом синхронизации блока восстановления результата, причем

50

арифметических блоков, входы коэффи- 55 Формирователь кода содержит три узла

циентов с первого, по четвертый первого арифметического блока подключены к выходам соответственно с первого по четвертый первого блока памяти

коэффициентов, отличающее- с я тем, что, с целью увеличения быстродействия и точности, в него введены блоков определения вычетов, (-1) блоков памяти коэффициентов и блок восстановления результата, вы :, ход которого является информационным выходом устройства, i-й (,8) выход j-ro (,J) блока определения вычетов подключен к входу i-ro операнда j-ro арифметического блока, k-й выход (,4) результата которого подключен к соответствующему вхоДУ k-й группы блока восстановления

результата, а входы блоков определения вычетов объединены и являются информационным входом устройства, выход синхронизатора подключен к входам синхронизации j-ro блока определения вычетов, блока восстановления результата и адресному входу s-ro (,1) блока памяти коэффициентов, причем j-й блок определения вычетов

содержит узел постоянной памяти, распределитель импульсов и восемь элементов И, выход узла постоянной памяти подключен к первым входам элементов И с первого по восьмой, вторые входы которых подключены к выходам соответственно с первого по восьмой распределителя импульсов, тактовый вход которого объединен с входом чтения узла постоянной памяти и является входом синхронизации блока определения вычетов, входом которого является адресный вход узла постоянной памяти, выходы элементов И с первого по восьмой являются выходами соответственно с первого по. восьмой блока определения вычетов, при этом блок восстановления результата содержит четыре формирователя . кодов и четыре регистра, выходы которых объединены и являются выходом

блока восстановления результата, входами k-й группы которого являются входы группы k-ro формирователя кода,выход которого подключен к информационному входу k-ro регистра, тактовый вход которого объединен с тактовым входом k-ro формирователя кода и является входом синхронизации блока восстановления результата, причем

постоянной памяти, семь регистров, два регистра константы, пять сумматоров, четыре элемента И и два элемента НЕ, причем выходы первого, вто рого ТГ третьего узлов постоянной памяти подключены к информационным входам соответственно первого, второго

I

и третьего регистров, выходы первого и второго сумматоров подключены к первым входам соответственно первого и второго элементов И, выходы которых подключены к первым информационным входам соответственно четвертого и пятого регистров, знаковые выходы третьего и четвертого сумматоров подключены соответственно, третьего сумматора - к второму входу первого элемента И и входу первого элемента НЕ, а четвертого - к второму входу второго элемента И и входу второго элемента НЕ, выходы первого и второго элементов НЕ подключены к первым входам соответственно третьего и четвертого элементов И, выходы которых подключены к вторым информационным входам соответственно четвертого и пятого регистров, выходы третьего и четвертого сумматоров подключены к вторым входам соответственно третьего и четвертого элементов И, выход первого регистра подключен

5

0

5

к первым входам первого и третьего сумматоров, выход второго регистра подключен к вторым входам первого и третьего сумматоров, выход первого регистра константы подключен к третьему входу третьего сумматора и первому входу четвертого сумматора, выход четвертого регистра подключен к первому входу второго сумматора и второму входу четвертого сумматора, выход третьего регистра подключен к информационному входу шестого регистра, выход которого подключен к второму входу второго сумматора и третьему входу четвертого сумматора , выход пятого регистра подключен к первому входу пятого сумматора, второй вход которого подключен к выходу второго регистра константы, выход пятого сумматора является выходом формирователя кода, входами группы которого являются адресные входы первого, второго и третьего узлов постоянной памяти, управляющие входы которьпс объединень с тактовыми входами регистров с первого по шестой и являются тактовым входом формирователя кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Систолический процессор для вычисления полиномиальных функций | 1988 |

|

SU1608689A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1732353A1 |

Изобретение относится к вычислительной технике и может быть использовано при реализации алгоритмов спектрального анализа на специализированных ЭВМ. Целью изобретения явля-. ется увеличение быстродействия и точности. Поставленная цель достигается за счет того, что устройство содержит J арифметических блоков 2 - 2 , ) блоков 1 - 1 определения вычетов и ) блоков 3, 3 р памяти коэффициентов

-л ./4 .№ 16

arertfz

0ueJ

26(30)

/3

ftg Гп Ъл

ПБ

tfMMf.4.nepSbiuatas(L (

-Ml

TTI 7:7

fi

III

LhlTT iJ P7

III r wig; c;3i

-;-:-I 5t I r)I,

JHL

fHl

JTTL

-tt- II

ЛТГ

-h1{ ICT71

« «Jp: 5, in

::iri Z3 /L j

iff . r// ,

Второй iacfe(L 2) 1 RL

jn

JiVt5 7

JI

.iwL.

A / Фиг.5

7«

7« «Шл

V //

j U

«L «i

/si

/г

Составитель А.Баранов Редактор Ю.Петрушке Техред Л,Сердюкова Корректор А.Обручар

Заказ 7904/48 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская, наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

L-TMJ шаг

t/i

| Устройство для реализации алгоритма быстрого преобразования фурье | 1973 |

|

SU480079A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство быстрого преобразования фурье | 1977 |

|

SU660057A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-04-17—Подача