(54) ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый логарифмический преобразователь | 1980 |

|

SU934499A1 |

| Логарифмический преобразователь | 1982 |

|

SU1064283A1 |

| Аналоговый логарифмический преобразователь | 1979 |

|

SU790002A1 |

| ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2252452C1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Логарифмический преобразователь | 1986 |

|

SU1411784A1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ | 1999 |

|

RU2175147C2 |

| Вычислительное устройство | 1981 |

|

SU978159A1 |

I

Изобретение относится к преобразователям электрических сигналов по логарифмическому закону и может быть использовано в аналоговых вычислительных машинах.

Известен логарифмический преобразователь, содержащий операционные усилители, логарифмирующие транзисторы, сумматор 1.

Однако это устройство характеризуется значительной погрещностью преобразования.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является логарифмический преобразователь, содержащий первый и второй операционные усилители, к инвертирующим входам и выходам которых подключены соответственно коллектор и эмиттер соответствующих логарифмирующих транзисторов, базы которых соединены с щиной нулевого потенциала, инвертирующий вход первого операционного усилителя через первый масщтабный резистор присоединен ко входу логарифмического преобразователя, к инвертирующему входу второго операционного усилителя подключен первый вывод второго масщтабного резистора, выходы

первого и второго операционных усилителей соединены с соответствующими входами суммирующе-вычитающего блока, сумматор, выход которого является выходом логарифмического преобразователя 2.

Недостаток этого устройства - погрешность передаточной характеристики, приводящая к снижению точности работы.

Цель изобретения - повышение точности преобразования.

Поставленная цель достигается тем, что в преобразователь введены ключевой элемент и источник опорного напряжения, приче.м выход источника опорного напряжения подключен к третьему входу суммирующевычитаюшего блока, выход которого через ключевой элемент соединен с первым входом сумматора, второй вход которого присоединен к выходу первого операционного усилителя, управляющий в.код ключевого элемента соединен со входом логарифмического преобразователя и со вторым выводом второго масштабного резистора.

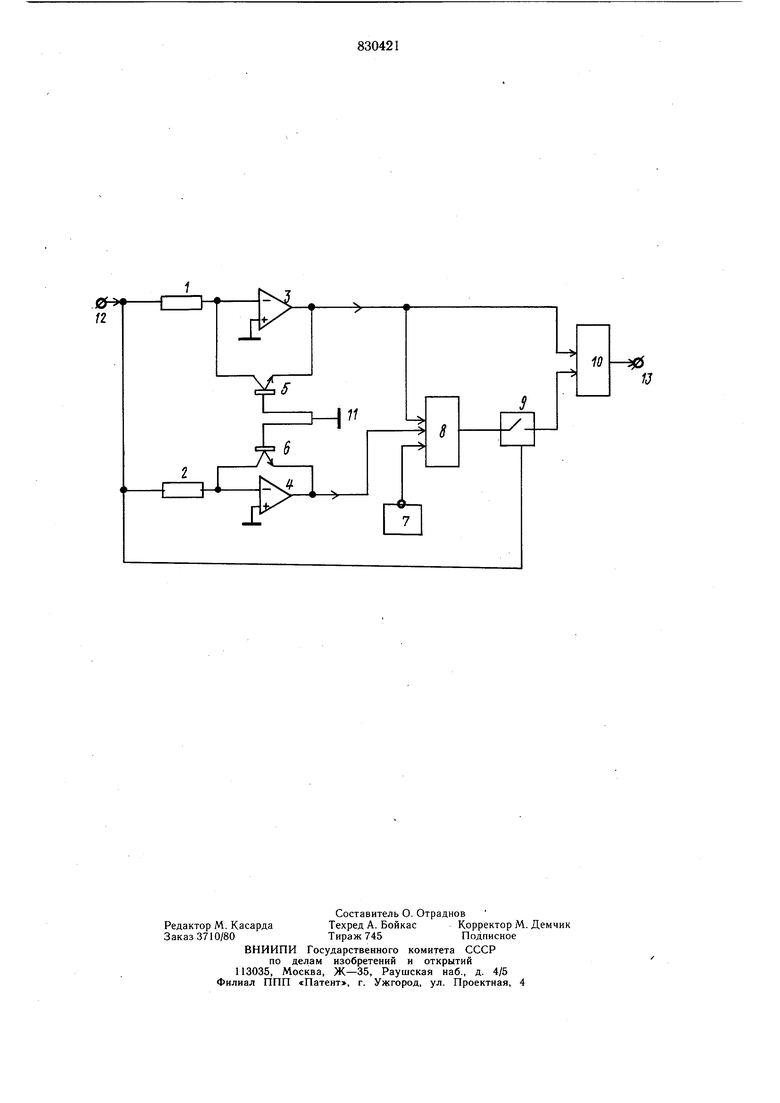

На чертеже изображена функциональная схема преобразователя.

Преобразователь содержит первый и второй масштабные резисторы 1 и 2, первый и второй операционные усилители 3 и 4, первый и второй логарифмирующие транзисторы 5 и 6, источник 7 онорного напряжения, суммирующе-вычитающий блок 8, ключевой элемент 9, сумматор 10, шину 11 нулевого потенциала, вход 12 и выход 13 логарифмического преобразователя. Логарифмический преобразователь работает следующим образом. Изменение напряжения на входе12 логарифмического преобразователя приводит к изменению тока коллектора первого логарифмирующего транзистора 5. Выходное напряжение первого операционного усилителя 3 изменяется пропорционально логарифму тока коллектора первого логарифмирующего транзистора 5. С ростом тока коллектора начинает сказываться погрещность от падения напряжения на объе.мном сопротивлении базы первого логарифмируюuiei-Q транзистора 5, которая приводит к увеличению выходного напряжения первого операционного усилителя 3 на величину этого падения напряжения. Сопротивление второго масштабного резистора 2 выбирается больше сопротивления первого масщтабHoio резистора 1, чтобы в конце рабочего диапазона, при максимальном токе коллектора второго логарифмирующего транзистора 6, Е5лияние падения напряжения / на объемном сопротивлении второго логарифг.гарующего транзистора 6 на выходное напряжение второго операционного усилителя 4 было малым. Необходимо, чтобы первый и второй логарифмирующие транзисторы 5 и 6 имели практически идентичные параметры. Тогда выходное напряжение суммирующе-вычитающего блока 8 содержит только напряжение погрешности первого логарифмирующего транзистора 5. При сравнительно малых величинах нанряжения на входе 12 логарифмического преобразователя, когда влиянием напряжения погрешности первого логарифмирующего транзистора 5 на выходное напряжение первого операционного усилителя 3 можно пренебречь, ключевой элемент 9 разомкнут и сумматор 10 передает выходное напряжение первого операционного усилителя 3 на выход 13 логарифмического преобразователя без изменений. С увеличением напряжения на входе 12 логарифмического преобразователя увеличивается и напряжение погрешности. Одновременно эта составляющая присутствует и на выходе суммирующе-вычитающего блока 8. С некоторого уровня напряжения на входе 12 логарифмического преобразователя замыкается ключевой элемент 9. С помощью сумматора 10 производится вычитание из общего сигнала напряжения погрешности первого логарифмирующего транзистора 5. В результате на выходе 13 логарифмического преобразователя формируется напряжение пропорциональное логарифму тока коллектора первого логарифмирующего транзистора 5 без составляющей напряжения погрещности. Таким образом, в предлагаемом логарифмическом преобразователе производится компенсация падения напряжения на объемном сопротивлении базы первого логарифмирующего транзистора 5 в выходном напряжении первого операционного усилителя 3 путем сравнения этого напряжения (с помощью второго операционного усилителя 4 и второго логарифмирующего транзистора 6) с его «идеальным значением, последующего выделения напряжения погрещности при помощи суммирующе-вычитающего блока 8 и суммирования выходного напряжения первого операционного усилителя 3, содержащего напряжение погрешности, с его выделенным инвертированным значением с помощью сумматора 10 в определенный момент, связанный с замыканием ключевого элемента 9. Предлагаемое изобретение позволяет уменьшить погрешность передаточной характеристики преобразователя. Формула изобретения Логарифмический преобразователь, содержащий первый и второй операционные усилители, к инвертирующим входам и выходам которых подключены соответственно коллектор и эмиттер соответствующих логарифмирующих транзисторов, базы которых соединены с щиной нулевого потенциала, инвертирующий вход первого операционного усилителя через первый масщтабный резистор присоединен ко входу логарифмического преобразователя, к инвертирующему входу второго операционного усилителя подключен первый вывод второго масштабного резистора, выходы первого и второго операционных усилителей соединены с соответствующими входами суммирующе-вычитающего блока, сумматор, выход которого является-выходом логарифмического преобразователя, отличающийся тем, что, с целью повышения точности преобразования, в него введены ключевой элемент и источник опорного напряжения, причем выход источника опорного напряжения подключен к третьему входу суммирующе-вычитающего блока, выход которого через ключевой элемент соединен с первым входом сумматора, второй вход которого подсоединен к выходу первого операционного усилителя, управляющий вход ключевого элемента соединен со входом логарифмического преобразователя и со вторым выводом второго масштабного резистора. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № 1333287, кл. G 4 G, опублик. 1973. 2.Авторское свидетельство СССР по заявке № 2795493/18-24, кл. G 06 G 7/24, 10.07.79 (прототип).

Авторы

Даты

1981-05-15—Публикация

1979-08-28—Подача