о з:) ч ел

со

ND

Изобретение относится к автоматике и вычиолительной технике, .а именно постоянным запоминающим устройствам трансформаторного типа.

По основному авт. св. № 796911 известно устройство, содержащее дешифраторы и две группы транзисторов Транзисторы первой группы образуют матрицу, в которой базы транзисторов каждого столбца соединены между собой и с соответствующим выходом первого дешифратора, эмиттеры транзисторов каждой строки соединены между собой и с коллектором соответствующего транзистора .второй группы, коллекторы транзисторов первой группы соединены с кодовыми проводами, а кодовые провода через диоды, включенные в прямом направлении по отношению к току опроса, соединены с ису точником питания, база каждого транзистора второй группы соединена с соответствующим выходом второго де.шифратора, а эмиттеры соединены между собой и через токазадающий резистор с шиной нулевого потенциала l.

Недостатком известного устройств ва является то, что на каждый кодовый провод требуется один транзистор первой группы. Поэтому при увеличении информационной емкости ЗУ, например, в 2 раза, во столько же раз возрастает количество транзисторов . первой, группы и увеличивается число транзисторов второй группы, а это ведет к значительным .затратам по оборудованию.

Цель изобретения - увеличение информационной емкости при, сохранении быстродействия адресной системы постоянного запоминающего устройства.с линейной выборкой.

Поставленная цель достигается тем что.в адресную систему постоянного запоминающего устройства с линейной выборкой введены дополнительные кодовые провода и диоды, ключи и третий дешифратор, причем коллектор каждого транзистора первой группы через основной и дополнительный кодовые провода последовательно соединен с основным и дополнительным диодами, включенными в прямом направлении по отношению к току опроса, и подсоединены к одним выводам соответствующих ключей, другие выводы которых соединены с источником питания, управляющие входы ключей соединены с соответствующими выходами третьего дешифратора.

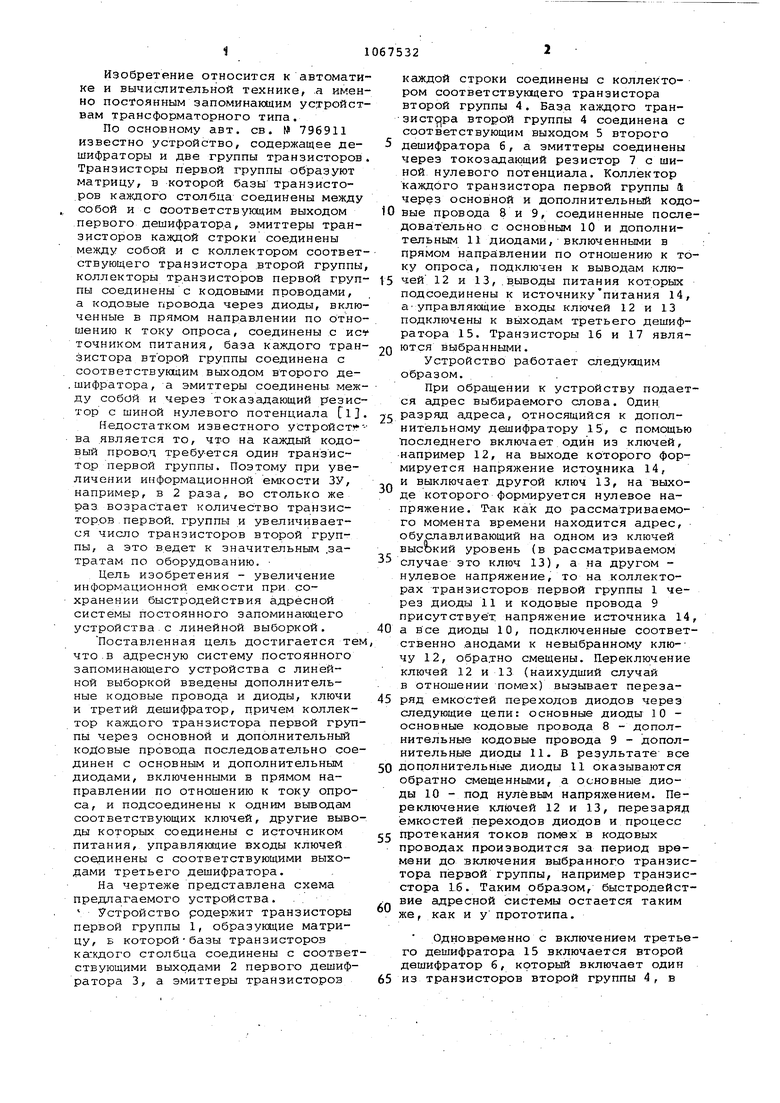

На чертеже представлена схема предлагаемого устройства.

Устройство родержит транзисторы первой группы 1, образующие матрицу, Б которойбазы транзисторов ка:кдого столбца соединены с соответствующими выходами 2 первого дешифратора 3, а эмиттеры транзисторов

каждой строки соединены с коллектором соответствующего транзистора второй группы 4. База каждого транзист |ра второй группы 4 соединена с соответствующим выходом 5 второго дешифратора 6, а эмиттеры соединены через токозадающий резистор 7 с шиной нулевого потенциала. Коллектор каждого транзистора первой группы 4 через основной и дополнительный кодовые провода 8 и 9, соединенные последовательно с основным 10 и дополнительным 11 диодами,включенными в прямом напра1влении по отношению к току опроса, подключен к выводам ключей 12 и 13,.выводы питания которых подсоединены к источникупитания 14, ауправляющие входы ключей 12 и 13 подключены к выходам третьего дешифратора 15. Транзисторы 16 и 17 являются выбранными.

Устройство работает следующим образом..

При обращении к устройству подается адрес выбираемого слова. Один разряд а.цреса, относящийся к дополнительному дешифратору 15, с помощью Последнего включает один из ключей, например 12, на выходе которого формируется напряжение источника 14, и выключает другой ключ 13, на -выходе которого формируется нулевое напряжение. Так как до рассматриваемого момента времени находится адрес, обуславливающий на одном из ключей высокий уровень (в рассматриваемом случае это ключ 13), а на другом нулевое напряжение, то на коллекторах транзисторов первой группы 1 через диоды 11 и кодовые провода 9 присутствует напряжение источника 14 а все диоды 10, подключенные соответственно .анодами к невыбранному клю-чу 12, обра.тно смещены. Переключение ключей 12 и 13 (наихудший случай в отношении помех) вызывает перезаряд емкостей переходов диодов через следующие цепи: основные диоды 10 основные кодовые провода 8 - дополнительные кодовые провода 9 - дополнительные диоды 11. В результате все дополнительные диоды 11 оказываются обратно смещенными, а основные диоды 10 - под нулевым напряжением. Переключение ключей 12 и 13, перезаряд ёмкостей переходов диодов и процесс протекания токов помех в кодовых проводах производится за период времени до включения выбранного транзистора первой группы, например транзисстора 16. Таким образом, быстродействие адресной системы остается таким же, как и у прототипа.

Одновременно с включением третьего дешифратора 15 включается второй дешифратор 6, который включает один из транзисторов второй группы 4, в данном случае транзистор 17, после чего начинается работа первого дешифратора 3, включающего по базам определенные транзисторы первой груп пы 1. Описанная последовательность включения дешифраторов б и 3 обеспечивает отсутствие ложного срабатывания выбранных по базе (но не выбранных по эмиттеру) транзисторов первой группы и надежное включение только одного транзистора первой группы ( в данном случае транзистора 16). В результате включения транзистора 16 посоединенные к нему основной. 8 и дополнительный 9 кодовые Г провода через транзисторы 16 и 17 оказываются подключенными к токозада щему резистору .7. В результате через выбранный в рассматриваемом случае основной кодовый провод 9, подключенный к транзистору 16 начинает протекать рабочий ток. Вместе с этим через дополнительный кодовый провод соединенный с транзистором 16, проте кает ток помехи, определяемый измене нием во времени напряжения на коллек торе выбранного транзистора 16. Одиа о ко величина этого тока существенно н сказывается на соотношении сигналпомеха, по отношению к прототипу. В предлагаемой адресной системе П принципиально возможно увеличение числа дополнительных проводов, подсое диненных к коллекторам транзисторов группы 1, до трех, семи и т. д. Однако, при 5ТОМ ухудшается соотношение сигнал-помеха, особенно по фронту рабочего тока в кодовом проводе, и тем самым ухудшается быстродействие устройства в целом. Таким образом, предлагаемое техническое решение позволяет в 2 раза увеличить информационную емкость устройства при незначительных дополнительных затратах: добавляются лишь диоды 11 и два ключа 12 и 13. Дешифратор 15 практически может отсутствовать, а ключи 12 и 13 подключаются соответственно к прямому и инверсному выходам триггера старшего разряда сщреса. Кроме того, предлагаемое устройство при сохранении информационной емкости по сравнению с прототипом позволяет вдвое сократить число транзисторов группы 1 и группы 4 , а также число выходов второго дешифратора 6, В обоих случаях при сохранении быстродействия имеет место заметное увеличение плотности хранения информации: в первом случае в 1,5-1,7 раза, во втором - в 1,31,4 раза. За счет сокращения аппаратурных затрат предлагаемое техническое решение позволяет увеличить надежность устройства в целсял. I

ь-4

-й-W-1 1-и«--W- ь-W-

«-

-w--ч-

-К}-fCl-

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресная система постоянногозАпОМиНАющЕгО уСТРОйСТВА СлиНЕйНОй ВыбОРКОй | 1978 |

|

SU796911A2 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1310901A2 |

| Устройство для ввода информации | 1982 |

|

SU1205136A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ | 2004 |

|

RU2282246C2 |

| Устройство для индикации | 1982 |

|

SU1072093A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Устройство для индикации | 1983 |

|

SU1124377A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU744730A1 |

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

АДРЕСНАЯ СИСТЕМА ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА С ЛИНЕЙНОЙ ИЛБОРКОЙ по осйовному авт. св. 796911, отличающаяся тем, что, с целью увеличения информационной емкости устройства при сохранении его быстродейстл ВИЯ, в него введены дополнительные кодовые провода и диоды, ключи и третий дешифратор, причем коллектор каждого транзистора первой группы через основной и дополнительный кодовые провода последовательно соединен с основным и дополнительным диодами, включенными в прямом направлении по отношению к току опроса, и подключен к одним выводам соответствующих ключей, другие выводы которых соединены с источником питания, управляющие входы ключей соединены с соответствующими выходами третьего дешифратора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Адресная система постоянногозАпОМиНАющЕгО уСТРОйСТВА СлиНЕйНОй ВыбОРКОй | 1978 |

|

SU796911A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-01-15—Публикация

1982-07-28—Подача