1

Изобретение относится к области вычислительной техники, в частности к микроэлектронным запоминающим устройствам, и может быть использовано g в устройствах обработки двоичной информации в качестве постоянной памяти подпрограмм, табличных данных, генераторов символов, функций и преобразователей кодов.jQ

Известны постоянные запоминающие устройства (ПЗУ),в которых в качестве запоминающих элементов используются диоды. Такие ПЗУ содержат диодномат- 5 ричный накопитель с горизонтальными и вертикальными шинами, элементы совпадения, нагрузочные резисторы, элементы управления и инверторы.

Недостатки таких ПЗУ заключаются 20 в наличии большого числа peзиcтopoв что ограничивает информационную ем кость ; в значительной зависимости характеристик ПЗУ от разброса параметров компонентов; в наличии большого 25 количества элементов, что приводит к ухудшению весо-габаритных характеристик; в сложной технологии изготовления, а также в большом количестве выводов из диодно-матричного на- .зо

копителя, что является ограничением увеличения информационной емкости и увеличивает количество паянных соединений, следовательно, понижает его надежность.

Известны ПЗУ, содержащие диодноматричный накопитель, выходные диодные сборки, резисторы, защитные диоды, диоды для варьирования разрядности, диоды для форсированного установления исходного состояния, адресные и разрядные шины,

Heдocтaткa IИ таких ПЗУ являются наличие большого числа резисторов, что ограничивает информационную емкость; большая рассеиваемая мощность; сложная технология изготовления, зна чительная зависимость характеристик устройства от разброса параметров компонентов, большое количество выводов из диодно-матричного накопителя,что, в свою очередь, увеличивает количество паяных соединений при сборке ПЗУ, понижает его надежность, а также ограничивает увеличение информационной емкости.

Известны также ПЗУ,в которых информация заносится в технологическо

процессе с помощью диодов, включаемых в пересечение горизонтальных и вертикальных шин (диодно-матричный накопитель) ,

Такие ПЗУ содержат адресный дешифратор первой группы, диодно-матричный накопитель, состоящий из m секций (числовых блоков), адресные входные) и разрядные (выходные) шины шифратор, группы инверторов вентилей Адресныешины накопителя, соединяющие аноды диодов, соединены с соответствующими выходами адресного дешифратора первой группы,разрядные шины накопителя, соединяющие катоды диодов соединены с первыми входами соответствующих инверторов, вторые входы инверторов каждой секции подключены к соответствующей шине управления, выходы одноименных инверторов подключены к соответствующим входам шифратора.

Недостатками таких ПЗУ являются наличие большого количества выводов из диодно-матричного накопителя (для информационной емкости 256 бит количество выводов равно 32, а при информационной емкости 1024 бит количество выводов равно 64), что, в свою очередь, увеличивает количест.во паяных соединений при сборке ПЗУ, пони:хает его надежность, а также ограничивает увеличение информацион-, ной емкости, наличие большого количетва инверторов, что усложняет технолгию изготовления устройства и ухудшает его весо-габаритные характеристики, большая рассеиваимая мощность/ , наличие значительных перепадов потребляемого тока во время считывания информации, что приводит к возникновению в шинах питания помех, снижающих помехоустойчивость, и, следовательно, надежность функционирования устройства/ значительная зависимость характеристик ПЗУ от разброса парамеров компонентов, что снижает устойчивость работы при изменении рабочих режимов и температуры окружающей среды.

Цель -изобретения - повьошение надех ности и увеличение информационной емкости постоянного запоминающего устройства.

Поставленная цель достигается тем что ПЗУ содержит дополнительный адресный дешифратор, формирователи выборки строки и слова на транзисторах с ийркекционным р-п переходом, считывающиё формирователи на транзисторах с инжекционнымр-п переходом, узел согласования на диодах Шоттки, при этом выходы адресного дешифратора соединены с соответствующими базами транзисторов с инжекционным р-п переходом формирователей выборки строки, коллекторы которых соединены с соответствующими адресными шинами, к которым также подключены катоды диодов Шоттки накопителя, аноды которых подключены к разрядным шинам на-копителя, которые соединены с соответствующими базами транзисторов с инжекционным р-п переходом считывающих формирователей и анодами диодов Шоттки узла согласования, причем катоды одноименных диодов Шоттки узла согласования подключены к коллекторам соответствующих транзисторов С инжекционным р-ппереходом формирователей выборки слова, базы которых соединены с соответствующими выходами дополнительного адресного дешифратора, при этом коллекторы соответствующих транзисторов с инжекционным р-п переходом считывающих формирователей объединены и являются выходами устройства, эмиттеры всех транзисторов с инжекционным р-п переходом подключны к шине нулевого потенциала, а инжекторы - к общей выходной шине,

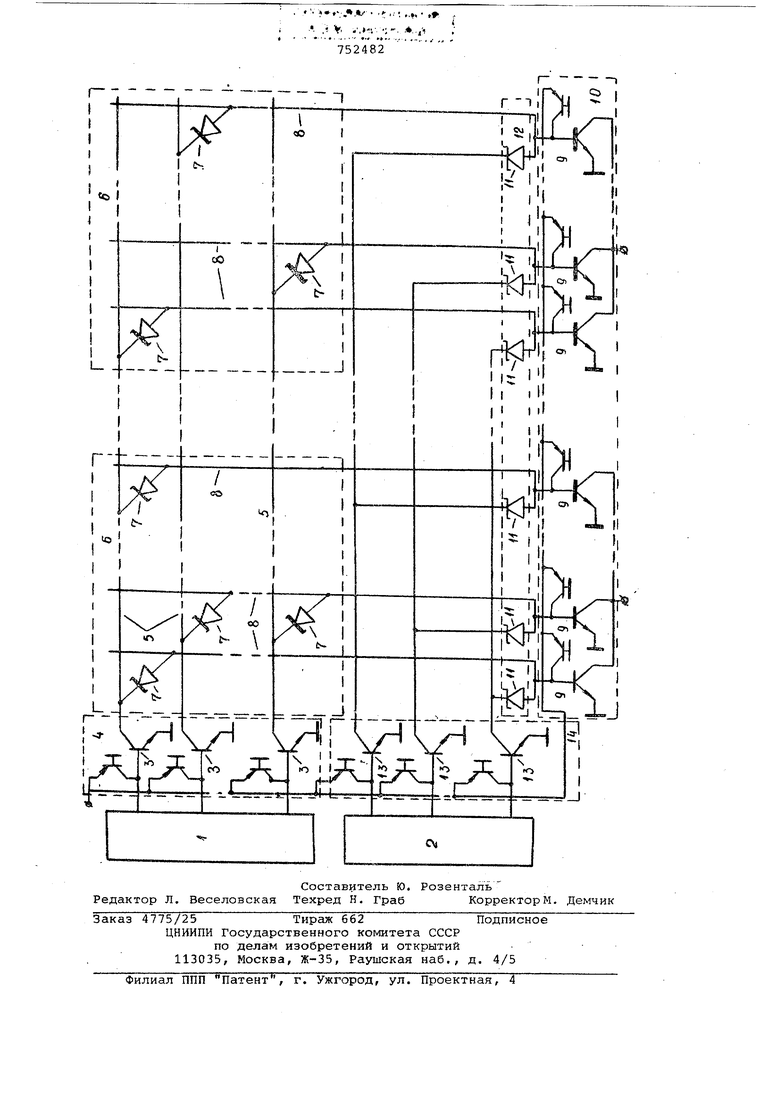

На чертеже приведена электрическая схема постоянного запоминающего устройства.

ПЗУ содержит адресные дешифраторы 1, 2, выходы адресного дешифратора первой группы 1 соединены с соответствующими базами транзисторов с инжекционным р-п переходом 3 формирователей 4 для выборки одной строки, коллекторы транзисторов с инжекционным р-п переходом 3 соединены с соответствующими адресными шинами 5 матричного накопителя б, состоящего из m секций, к адресным шинам 5 подключены катоды диодов Шоттки 7 матричного накопителя 6, аноды диодов 7 соединены с соответствующими разрядными шинами 8 накопителя б, разрядные шины 8 накопителя б подключены к соответствующим базам транзисторов с иняекционным р-п переходом 9 считывающи формирователей 10, к которым подключены анодды диодов Шоттки 11 злемента12 согласования, катоды одноименных диодов Шоттки 11 элементов 12 согласования объединены и подключены к .коллекторам соответствующих транзисторов с инжекционным р-п переходом 13 формирователей 14 для выборки слова, базы транзисторов с инжекционным р-п переходом 13 подключены к соответствующим выходам дополнительного адресного дешифратора 2, коллекторы транзисторов с инжекционным р-п переходом 9 считывающих формирователей 10 одноименных секций объединены и явля ются выходом устройства, при этом эмиттеры всех транзисторов с инжекционным р-п переходом подключены к шине нулевого потенциала, а инжекторы - к общей выходной шине,

Информационная емкость ПЗУ опреде ляется следующим выражением

5 где п - количество адресных шин в на-копителе. m - разрядность двоичного слова определяемая числом секций в накопителе, k - количество разрядных шин в одной секции. ПЗУ работает следующим образом. Для выбора необходимого слова на базу транзистора с инжёкцибнным р-п переходом 3, к коллектору которого подключена соответствующая адресная ишна 5, с выхода адресного дешифрато ра 1 подается высокий уровень напряжения (на остальные базы транзисторо с инжекционным р-п переходом 3 подае ся низкий уровень напряжения), при этом на этой шине устанавливается низкий уровен напряжения. В этом слу чае выбирается необходимая адресная шина. Выбор соответствующих разрядных шин производится путем подачи низкого уровня напряжения с дополнительного адресного дешифратора 2 на базу соответствующего транзистора с инжекционным р-п переходом 13 (на остальные базы транзисторов с инжекционным р-п переходом 13 подается высокий уровень напряжения). В результате в каждой из m секций на пересечении выбранных адресных и раз рядных шин выбираются необходимые запоминающие элементы. Если в пересечении адресной и разрядной шин имеет ся диод, то со.ответствующий транзистор с инжекционным р-п переходом 9 считывающих формирователей 10 запирается и на соответствующем вькоде ПЗУ устанавливается высокий уровень напряжения, а если диод отсутствует то на выходе ПЗУ будет низкий уровен напряжения. Таким образом, на выхода ПЗУ считывается m разрядное слово. Таким образом, в предлагаемом устрюйстве уменьшается количество внешних выводов, что позволяет увели чить информационную емкость, упрощается технология его изготовления и / улучшается весо-габаритная характеристика, повышается надежность функционирования устройства; из-за малог тока потребления по инжекторам устройство рассеивает сравнительно малую мощность; поскольку при обращени к ПЗУ потребляемый ток практически ос тается постоянным, то помехи, генери руемые на шинах питания, получаются очень малыми, чтЬ важно с точки зрения надежности функционирования устройства; из-за малой зависимости характеристик ПЗУ от разбросов параметров компонентов, .оно может функционировать в большом диапазоне рабочей температуры ( 4 Т б 125с) ; устройство обладает малой энергией переключения. Формула изобретения Постоянное запоминающее устройство, содержащее адресный дешифратор, матричный накопитель, выполненный из запоминающих модулей на диодах Шоттки, и адресные и разрядные шины, отличающееся тем, что, с целью повышения надежности и информационной емкости устройства, оно содержит дополнительный адресный дешифратор, формирователи выборки строки и слова на транзисторах с инжекционным р-п переходом, считывающие формирователи на транзисторах с инжекционным р-п переходом , узел согласования на диодах Шоттки, при этом выходы адресного дешифратора соединены с соответствующими базами транзисторов с инжекционным р-п переходом формирователей выборки строки, коллекторы которых соединены с соответствующими адресными шинами, к которым подключены катоды диодов Шоттки накопителя, аноды которых подключены к разрядным шинам накопителя, которые соединены с соответствующими базами транзисторов с инжекционным р-п переходом считывающих формирователей и анодами диодов Шоттки узда согласования, причем катоды одноименных диодов Шоттки узла согласования подключены к коллекторам соответствующих транзисторов с инжекционным р-п переходом формирователей выборки слова, базы которых соединены с соответствующими выходами дополнительного адресного дешифратора, при этом коллекторы соответствующих транзисторов с инжекционным р-п переходом считывающих формирователей объединены и являются выходами устройства, эмиттеры всех транзисторов с инжекционным р-п переходом подключены к шине нулевого потенциала, инжекторы к общей выходной шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Полупроводниковое постоянное запоминающее устройство | 1978 |

|

SU763968A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU763969A1 |

| Накопитель для полупроводникового запоминающего устройства | 1980 |

|

SU955202A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| Способ записи и считывания информации в запоминающих устройствах с инжекционным питанием и устройство для его осуществления | 1975 |

|

SU646371A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-07—Подача