HaoepexekHe относится к радиотехнике.

По основному авт. св. № 926784 известен детектор частотно-манипулированньах сид:налов, содержащий последовательно соединенные формирователь импульсов ц первый триггер, а также генератор тактовых сигналов, выход которого подключен к первым входам первого и второго счетчиков,выходы которых соединены с входами элемента ИЛИ, второй и третий триггеры и два элемента , выходы которых подключены соответственно к первым входам второго и третьего триггеров, первыевыходы которых соединены соответственно с первыми входами первого и второго элементов И-НЕ, вторые входы которых соединены с выходом генератора тактовых сигналов, причем ВЫХОДЫ-лервого триггера подключены к третьим входам элементов И-НЕ и вторым входам второго и третьего триггеров, вторые выходы которых соединены соответственно с вторыми входами первого и второго счетчиков, третьи входы которых соединены соответственно с выходами первого и второго элементов И-НЕ 1.

Однако в известном устройстве недостаточная помехозащий(енность.

Цель изобретения - повышение помехозащищенности.

Поставленная цель -достигается тем что в детектор частотно-манипулированных сигналов, содержащий последовательно соединенные формирователь импульсов и первый триггер, а также генератор тактовых сигналов, выход которого подключен к первым входам первого и второго счетчиков,выходы которых соединены с входами элемента ИЛИ, второй и третий триггеры и два элемента И-НЕ/ выходы которых подключены соответственно к первым входам второго и третьего триггеров, первые выходы которых соединены соответственно с первыми входами первого и второго элементов И-НЕ, вторые входы которых соединены с выходомгенератора тактовых сигналов, причем выходы первого триггера подключены к третьим входам элементов И-НЕ и вторым входам второго и третьего триггеров, вторые выходы которых соединены соответственно с BTOpbiivw входами первого и второго счетчиков, третьи входы которых соеинены соответственно с выходами первого и второго элементов И-НЕ, введены инвертор, два элемента И, ополнительный элемент и суммирую- . ий счетчик, при этом выход элемена ИЛИ соединен с первым входом перого элемента И и через инвертор с ервым входом второго элемента И, торые входы элементов И соединены первым и вторым выходами суммируюего счетчика соответственно, выходы

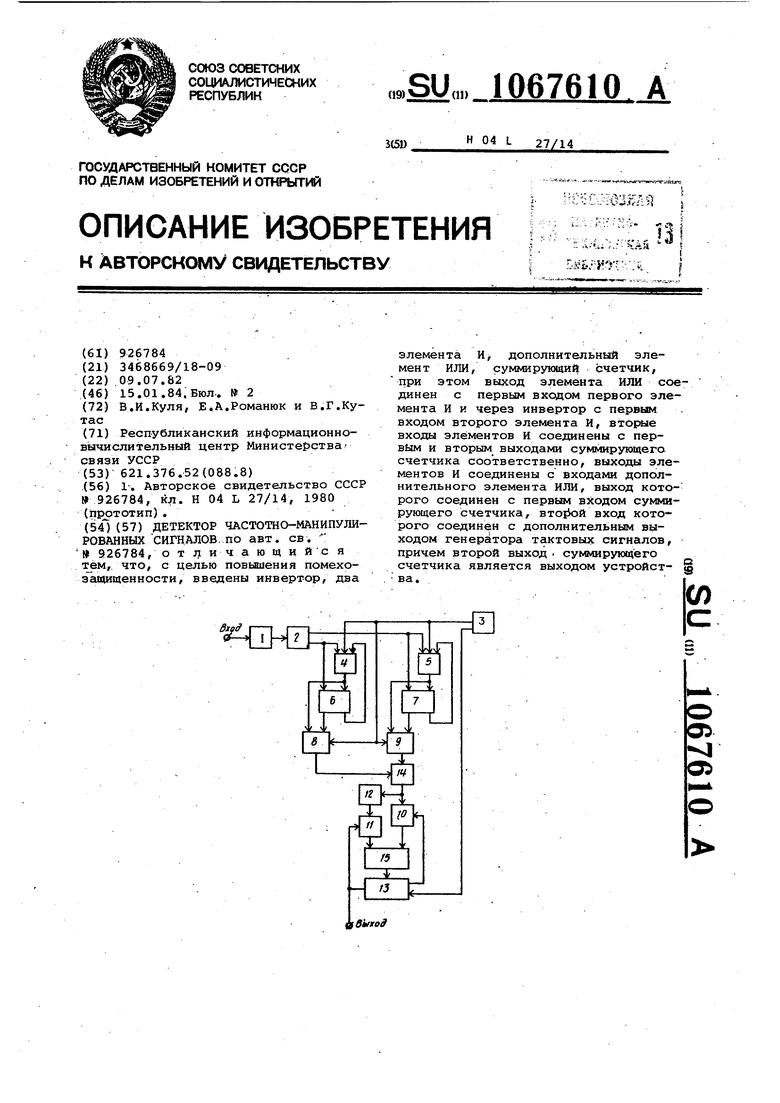

элементов И соединены с входами дополнительного элемента ИЛИ, выход которого соединен с первым входом суммирующего счетчика, второй вход которого соединен с дополнительным 5 выходом генератора.тактовых сигналов, причем второй выход суммирующего счетчика является выходом устройства. На чертеже изображена структурная электрическая схема предлагаемого

Q детектора.

Детектор частртно- манипулированных сигналов содержит формирователь 1 импульсов, триггер 2, генератор ч 3 тактовых сигналов, элементы И-НЕ

4 и 5, триггеры 6 и 7, счетчики 8 и 9, элементы И 10 и 11, инвертор 12, суммирующий счетчик 13, элемент ИЛИ 14, дополнительный элемент ИЛИ 15,

Детектор частотно-манипулированных сигналов работает следующим об0 разом.

Частотно-манипулированный сигнал с входа детектора через формирователь 1 импульсов, выполненный, например в виде триггера Шмитта,

5 поступает на счетный вход триггера 2, служащего для выделения периодов входного сигнала и поочередно . коммутирующего -первый и второй различители чйстоты входного сигнала,

0 -Оба различителя частоты идентичны, и каждый из них содержит элемент И-НЕ 4 и 5, триггер 6 и 7 и счетчик8 и 9, .

На информационные входы различи5 телей поочередно подаются потенциалы с прямого и инверсного выходов триггера 2, На тактирующие входы различителей постоянно поступают тактирующие импульсы частоты f с выхода генератора 3 тактовых сигналов,

Различители частоты реагируют

на изменение частоты входного сигнала, поступающего на вход детектора, путем подачи на входы элемента ИЛИ 14 сигналов логической или ло5 гического О , Они поочередно выдают сигналы на соответствующие входы элемента ИЛИ.14 в течение каждого периода входного сигнала, благодаря чему на выходе элемента ИЛИ 14

0 поддерживается уровень логической или логического О, в зависимости от частоты входного сигнала,

Различители частоты поочередно

5 находятся в .одной из двух фаз: переходной и установившейся.

Переключение фаз в различителях осуществляет триггер 2, управляемый по счетному входу входным сигналом, 0 преобразованным формирователем 1

импульсов в последовательность прямоугольных импульсов одной из двух участот F или Г ,

В то время, как один различитель 5 частоты, например, находится в переходной фазе, другой различйтель частоты находится в установившейся фазе. При этом в другом различитёле частоты на третий вход элемента И-НЕ 4 и второй вход триггера 6 пос тупает потенциал логического О по информационному входу различител частоты с прямого выхода триггера 2 Триггер 6 реагирует по своим вх дам на потенциалы логического Поэтому в течение установившейся фа зы на прямом выходе триггера 6 поддерживается потенциал логического О, который воздействует на первый (запрещающий) вход счетчика 8. Потенциал на ВЫХоде последнего разряда счетчика 8сохраняется неизмен но низким и передается на выход раз личителя. В момент изменения состояния на информационном входе различителя частоты от логического к логи ческой триггер 6 еще остается в прежнем состоянии, при котором с его инверсного выхода на первый вхо элемента И-НЕ 4 поступает потенциал логической . И поскольку на второй вход элемента И-НЕ 4 постоянно подается последовательность тактирующих сигналов частоты- f с выхода генератора 3, то на выходе элемента И-НЕ 4 появляется.только один инвертированный импульс, который, воздействуя на второй (установочный) вход счетчика 8, устанавливает все его разряды в состояние ло гического О, а также переводит триггер 6 по первому входу в противЪположное состояние, чем заблокиру ет прохождение последних тактирующи сигналов через элемент И-НЕ 4. С этого момента начинается переходная фаза одного различителя частоты, а другой различйтель частоты, находится в установившейся фазе. При этом тактовые сигналы частоты f поступающие в одном различитёле час тоты на третий (счетный) вход счетчика 8, подсчитываются в нем Переходная фаза продолжается до очередной смены значений сигнала на информационном входе этого различителя частоты, т.е. до появления сиг Состояние. нала логического последнего разряда счетчика 8 в кон це переходной фазы (логический О или логическая ) зависит от дл тельности периода входного сигнала, соответствующего длительности переходной . Е,сли частота входного сигнала п - число двоичных счетчика 8, то на выходе различителя частоты в конце переходной фазы установится потенциал логической 1 а в противном случае - логического Оба различителя частот поочеред-г но выдают решения на соответствукицие входы элемента ИЛИ 14 о каждом периое сигнала, поступающего на вход, благодаря чему на выходе детектора поддерживается уровень логической 1 или логического в зависимости от частоты входного сигнала. Для освобождения полученного детектированного двоичного сигнала от кратковременных импульсных помех (одиночных и сгруппированных в пакет) используется суммирующий счетчик 13. На счетный вход суммирующего счетчика 13 с дополнительного выхода генератора 3 подается последовательность тактирующих сигналов с периодом следования ,- , где f- длительность элементарной посьшки (бита) двоичного сигнала; tp- длительность помех за время длительности элементарной посылки; m - количество двоичных разрядов суммирующего счетчика 13. Если уровень сигнала на выходе элемента ИЛИ 14 соответствует логической , счетчик работает в Е5ежиме сложения тактирующих сигналов. Как только разрядная сетка суммирующего счетчика 13 будет заполнена наполовину, т.е. на втором выходе суммирующего счетчика 13 (прямом выходе старшего разряда счетчика) установится уровень логической , на выход детектора будет передано значение логической II, которое поддерживается неизменным, пока уровень двоичного сигнала на выходе элемента ИЛИ 14 соответствует логической . Уровень-логического О, установившийся при этом на первом выходе суммирующего счетчика 13 (инверсном выходе старшего разряда счетчика), подключенном к первому входу элемента И 10 через дополнительный элемент ИЛИ 15, блокирует дальнейшее сложение тактирующих сигналов суммирующим счетчиком 8. Если уровень двоичного сигнала на выходе элемента ИЛИ 14 меняется ОТ значения логической к значению логического О, суммирующий счетчик снова возобновляет сложение тактирующих сигналов, так как Сигнал, поступающий через инвертор 12, элемент И -11 и дополнительный элемент ИЛИ 15, разрешает сложение. Логический О на выходе детектора появляется как только суммирующий счетчик 13 оказывается сброшенным в начальное нулевое состояние из-за переполнения разрядной сетки. При этом сразу же заблокируетея дальнейшее сложение тактирующих сигнсшов запрещающим потенциалом с прямого выхода старшего разряда сумS10676кирующего счетчика 13, воздействующим через элемент И- II и дополиительный элеМеит ИЛИ 15 на запрещающий вход суммирующего счетчика 13, На выход детектора не пропуска-5 ются одиночные помехи длительностью Менее ( , а также пачки кратковременных импульсных помех, .суммарная длительность которых на. 10 любом интервале г не превышает той же величины. Предлагаемый детектор характеризуется простотой конструктивного выполнения, высокой нгщежностью и помехозащищенностью. Он может быть использован в аппаратуре передачи данных, а также в устройствах воспроизведения двоичных сигналов, записанных на магнитном носителе.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2444123C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Входное устройство для электронных часов | 1990 |

|

SU1774471A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| Детектор частотно-манипулированных сигналов | 1980 |

|

SU926784A1 |

| Цифровой термометр | 1987 |

|

SU1571427A1 |

| Триггерное устройство | 1981 |

|

SU970647A1 |

ДЕТЕКТОР ЧАСТОТНО-МАНИПУЛИ РОВАННЫХ СИГНАЛОВ, по ав. св. 926784, о т л и ч а ю щ и и с я тем, что, с целью повышения помехозащищенности, введены инвертор, два элемента И дополнительный элемент ИЛИ, суммирующий счетчик, при этом выход элемента ИЛИ соединен с первым входом первого элемента И и через инвертор с первым входом второго элемента И, вторые входа элементов И соединены с первЫм и вторым выходами суммирующего счетчика соответственно, выходы элементов И соединены с входами дополнительного элемента ИЛИ, выход которого соединен с первым входом суммирующего счетчика, вто14ой вход которого соединен с дополнительным выходом генератора тактовых сигналов, причем второй выход . суммирующего счетчика является выходом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Детектор частотно-манипулированных сигналов | 1980 |

|

SU926784A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-01-15—Публикация

1982-07-09—Подача