(54) УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ ПРОГРАММ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

| Устройство для управления прерыванием программ | 1981 |

|

SU962950A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство прерывания программ | 1983 |

|

SU1119015A1 |

| Устройство для управления прерыванием программ | 1976 |

|

SU696459A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1979 |

|

SU783782A2 |

| Устройство для обслуживания запросов | 1977 |

|

SU737953A1 |

Устройство принадлежит к вычислительной технике и может быть использовано в системах прерывания цифровых вычислительных мавшн. Известно устройство для обработки запросов с контролем очередности содержащее блок памяти, записывающий и считывающий кольцевые счетчики, формирователь импульсов, соединенный с шифратором, первые схег-и И, первые входы которых соединена с шиф ратором, вторые входы связаныс ваходами эа писывгиощего счетчика , схемы ИЛИ, соединенные со входами дешифратора, вторые cxetvftj И, первые входы которых соединены с выходалш ячеек памяти, вторые входи - с выхо дами считывающего счетчика, а выход соединены с соответствующими входами схем ИЛИ. Входы блок аконтроля наличия ин;формадии соединены с выходами ячеек памяти, а выходы соединены с первйм входами схем запрета и третьих схем И и - со входами блока синхронизаци первый и второй выходы которого соединены со входами соответствующих счетчиков, вторые входы третьих схе И соединены с выходами записывающег счетчика и - со вторыми входами схе запрета, а выходы третьих схем И через схему ИЛИ соеяиненн со счетным входом 3аписывалядего счетчика 1 . Недостатком этого устройства является ej-o низкая надежность.. Наиболее близким к предлагаемому по технической сущности является устройство для прерывания программ, содержащее регистр приоритета, регистр маски, схему анализа присчритета и шифратор, причем входы шифратора через схему анализа приоритета соединены с выходами регистра при фятета и регистра маски, . выходы UBiil a- тора и управляювдай выход схемы анализа приоритета соединены с соответствуюй№Ц«1 выходами устройства 2. Недостаток устройства состоит в низкой надежности его работы. Цель изобретения - повьвиение надежности работы устройства. Поставленная цель достигается тем, что в устройство, содержшцее М-разрядные регистр приоритета и регистр маски, выходы которых соединены с соответствующими входами узла присчрятета, управляющий выход котсч ого является выходом наличия прерывания, а информационный выход соединен со входом шифратора, выход которого является выходом кода прерыванигя устрой ,введены анализа состояния регистров, дешифратор нечётносfK к&да -ксхё а сравнения, причем Твйходи регистра прерываний подключены к соответствующим входам первой группы входов узла анализа состоя.ния регистров, вторая группа входов которого соединена с соответствующиNM выходами регистра масок, а соединен с первым входом схемы сравнения, второй вход которой подключен через дешифратор нечетности кода к выходу шифратора, выход cxeiijiH сравне иия является контрольным выходом устройства. Кроме того, .узел анализа состояния регистров содержит элементы И, И-НЕ и ИЛИ, причем выходы элементов И соёдинёнЫ с соответствующи-ми входами элемента ИЛИ, выход которого является выходом узла, первый и второй входы i-ro элемента И подключены Соответственно к входам первой и второй l-pynn входов узла, имеющим номер 2 i-1, аходда i-ro элемента И-НЕ подключены Соответственно к 2 1-ым входам первой и второй группы входов узла, выход i-ro элемента И-НЕ соединён с соответствующими входами всех элементов И, имеющими номера, большие i+1 (,2,...,М/2, если М - четное; , 2, ..., (М+1)/2 ,

ерли М - нечетное).

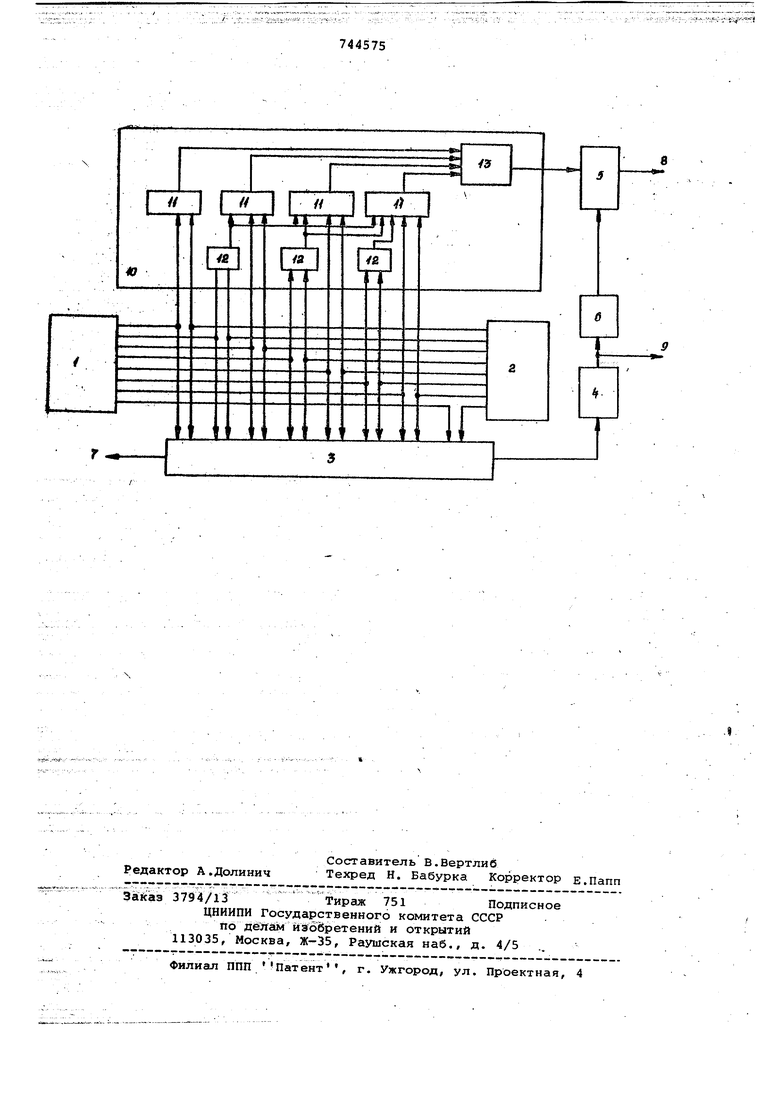

На чертеже показана блок-схема устройства.

Устройство содержит регистр 1 приоритета, регистр 2 маски, узел 3 приоритета, шифратор 4, схему 5 сравнения, дешифратор б нечетности кода, выход 7 нйлйчия прерывания, контрольный выход 8 устройства, выход 9 кода преры вания и узел 10 анализа состояния регистров, включающий элемент 11 И, элементы 12 И-НЕ и элемент 13 ИЛИ. Блок-схема узла 10 предйтав лена для примера, когда разрядность регистров 1 и 2. равна 8.

Устройство работает следующим образом..

Наличие отдельных запросов на прерывание фиксируется в соответствующих разрядах регистра 1. в регистре 2 командами от програмМы-диспетче эа у станавливается код защиты от преры вания, причем единичное значение разряда в регистре 2 соответствует разрешению прерывания при поступлении в одноименный разряд регистра 1 запроса (цепи установки кодов в регистре 2 и сигналов запросов в регистESt-l«., .,. ) .. . .,.. зел 3 приоритета обеспечивает выделение сигнала прерывателя с более высоким приоритетом, который, определяется слева направо из числа по. ступивших н а схему сигналов п1рёры вания, разрешенных кодом регистра 2. Факт отсутствия незамаскироёанных

Прерываний отмечается сигналом на выходе 7.; В случае необходимости

swa jjijsvsss- „,

осуществит) прерывание на выходе 7 появляется сигнал, а узел 3 формирует унитарный код номера прерывания, который преобразуется шифратором 4 в двоичный код, выдаваемый на выход 9 .

Контроль функционирования производится параллельно с работой устройства. При этом в устройстве двоичные коды номеров прерываний, формируемые шифратором 4, распределены так, что четному по номеру прерывания соответствует четный двоичный код. .

В таблице дано распределение кодов по номерс м прерываний, причем 5 число прерываний равно восьми.

001 000

Номера прерываний 1,3,5,7 - нечетные 010

он

2,4,6,8 - четные .

100 101

111

110

Узел 10 оп)ределяет по кодам регистра 1 и регистра 2 четность номе,ра обрабатываемого прерывания. Сигнал на выходе узла 10 равен единице, если номер нечетный, и нулю, если номер четный. Дешифратор б определяет четность выходного кода шифратора 4 (сигнал на выходе дешифратора 6 равен 1, если код нечетный, и нулю если код четный). Выходные сигналы узла 10 и дешифратора б сравниваются на схеме 5 сравнения. Появление на выходе 8 сигнала несравнения свидетельствует о сбое или отказе устройства, поскольку коды номеров прерываний имеют значения, приведенные в таблице и при правильном функциониро вании устройства выходные СИГНЁШЫ узла 10 и дешифратора 6 совпадают. В случае неправильной работы устройства (например если узел 3 формирует неверный унитарный код номера прерывания или если шифратор 4 неверно преобразует этот код в двоичный) выходные сигналы уэла 10 и дешифратора б не совпадают и на выходе 8 схема 5 формирует сигнал несравнения, который в. виде сигнала ошибки поступает в контрольную шину устройства. Факт отсутствия незамаскированных прерываний отмечается единичным сигналом на управляющем выходе 7 узла 3. Узел 10 злементами 11 И и элемен тами 12 ИЛИ-НЕ блокирует прохождени запрещенных состоянием регистра 2 запросов. Кроме того, запрос более высокого, приоритета (в данном случа ймёюдий более низкий четный номер) блокирует возможность формирования единицы всех нечетных запросов более низкого приоритета при помощи сигнала с выхода соответствующего элемента 12 И-НЕ, Например, при наличии сигналов на четвертых разрядах регистров 1 и 2 (на чертеже номера, разрядов регистров увеличиваются слева-направо) элемента 12 И-НЕ, со единенных входами с выходами этих разрядов снимает разрешающий сигнал формирования единицы со всех элемен тов 11 и,- соответствующих более высоким номерам разрядов регистров 1 и 2. При этом единица на выходе узла 10 может быть сформирована лишь при появлении немаскированных запросов, имеющих номер 1 и 3. Таким образом, устройство обеспе чивает повышение надежности работы устройства при блокировании выполне ния прерывания в случаях неправильной работы его элементов.. Формула изобретёния 1. Устройство для прерывания программ , содержащее М-разрЯдные регистр приоритета и регистр маски, выходы которых соединены ic сАответс вующими входами узла приоритета, управляющий выход которого является выходом наличия прерывания, а инфор ционный выход соединен со входом ши ратора, выход которого является выходом кода прерывания устройства/о личающееся тем, что, с целью повышения надежности устройства, в него введены узел анализа состояния регистров, дешифратор нечетности кода и схема сравнения, причем выходы регистра прерываний подключены к соответствующим входам первой группы входов узла анализа состояния регистров, вторая группа входов которого соединена с соответствующими выходами регистрамасок, а выход соединен с первым входом схемы сравнения, второй вход которой подключен через дешифратор нечетности кода к выходу шифратора, выход схемы сравнения является контрольным выходом устройства. 2. Устройство по п.1,0 т л и чающееся тем, что узел анализа состояния регистров содержит элементы И, и ИЛИ, причем выходы элементов И соединены с соответствующими выходами элемента ИЛИ, :йыход которого является выходом узла, первый и второй входы i-ro элемента И подключены соответственно к входам первой и второй групп входов узла, имеющим номер 2 1-1, входы 1-го элемента И-НЕ подключены соответственно к 2 i-ым входам первой и второй группы входов узла, выход 1-го элемента И-НЕ соединен с соответствующими входами всех элементов И, имеющими номера, больше i+l (,2,...,М/2, если М - четное; ,2,,..,(М+1)/2, если М - нечетное). Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №3500.05, кл. G Об F 15/46, 1970. 2.Майоров С.Д., Новиков Г.И. Принципы организации цифровых машин. Л., Машиностроение, 1974, с. 354-358, (прототип).

Авторы

Даты

1980-06-30—Публикация

1978-03-27—Подача