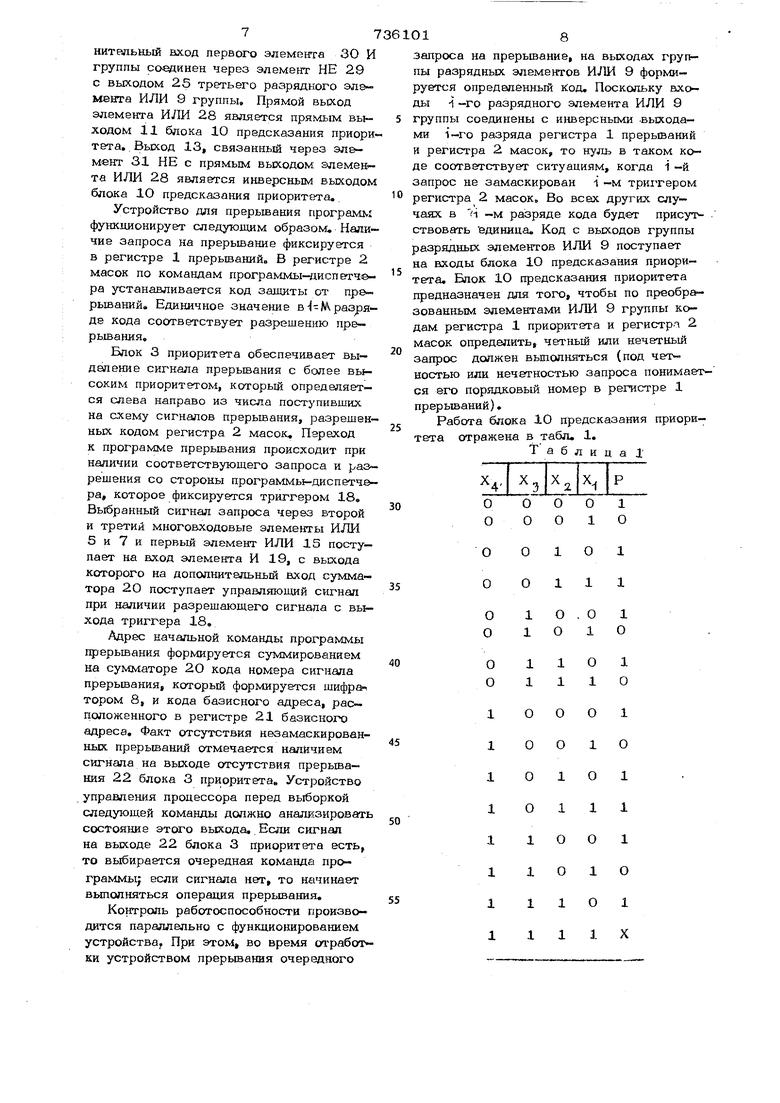

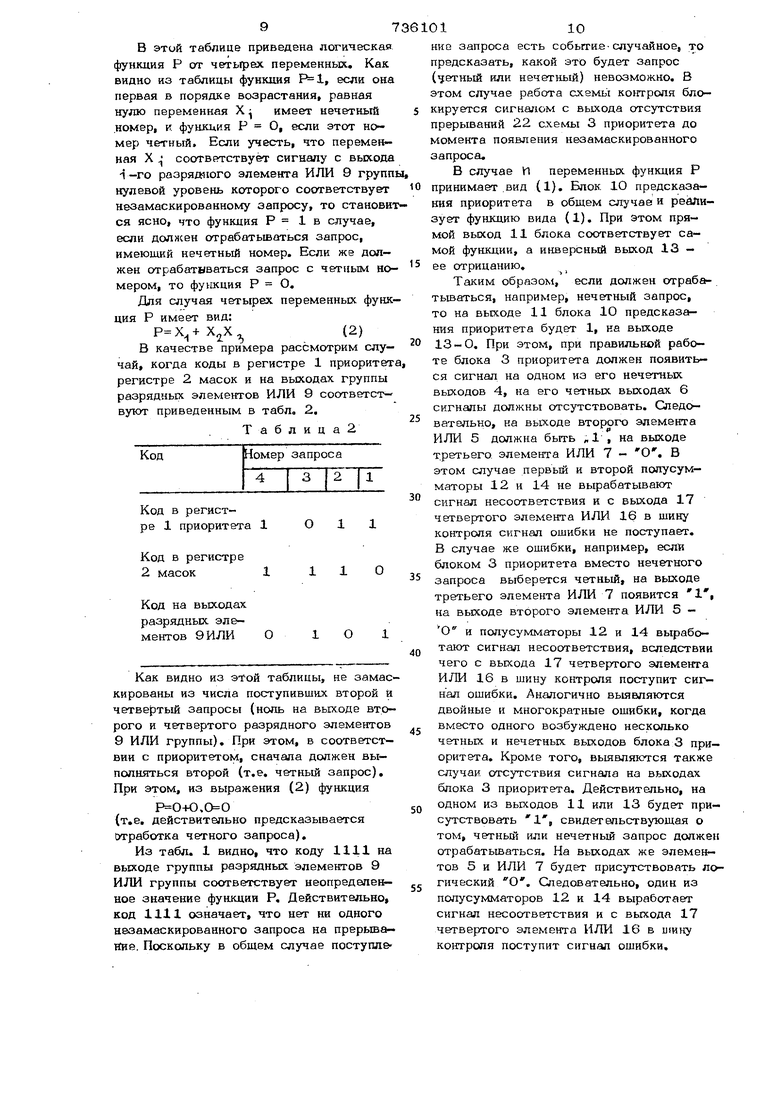

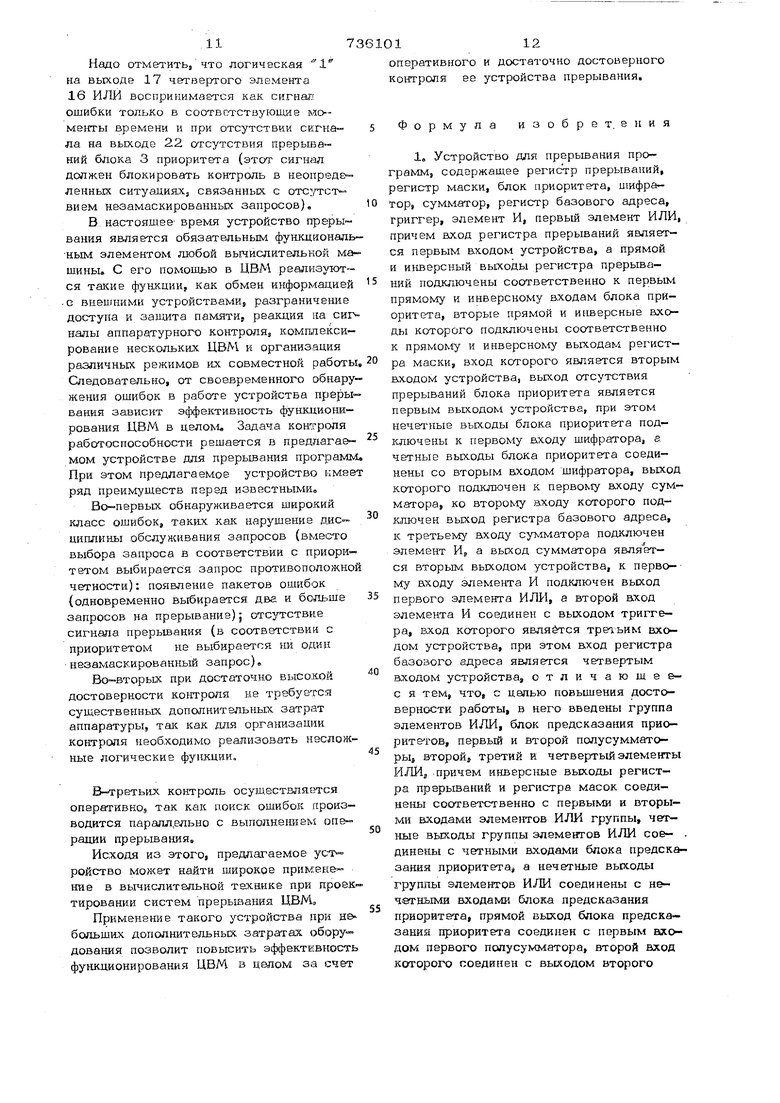

Изобретение принадлежит к вычислительной технике и может быть испопь зовано в системах прерьшания цифровых, вычислительных машин. Известно устройство для обработки запросов с контролем очередности, содержащее блок памяти, записывающий и считывающий кольцевые счетчики, формирователь импульсов, соединенньвй с щифратором, первые схемы И, первые входы которых соединены с шифратором, вторые входы связаны с выходами записывающего счетчика, схемы ИЛИ, соединенные с входами дешифратора, вторые схемы И, первые аходы которых соединены с выходами ячеек памяти, вторые входы - с выходами считьшающего счетчика дв выходы соединены с соответствую щими входами схем ИЛИ ij. Входы бло ка контроля наличия информации соедине- ны с выходами ячеек памяти, а выходы соединены с первыми входами схемы запрета и третьих схем И и с входами бло ка синхронизации, первый и второй выходы которого соединены с входами соогг- ветствующих счетчиков, вторые входы третьих схем И соединены с выходами записьшающего счетчика и с вторыми входами схем запрета, в выходы третьих схем И через схему ИЛИ соединены со счетным входом записьшающего счетчика. Счетный вход считьшающего счетчика соединен с выходом датчика окончания обслуживания и с третьими входами вторых схем И. Больщое количество аппаратуры и отсутствие контроля соответствия выбранного запроса дисциплине обслуживания запросов, делает это устройство несовершенным. Известно устройство для поерьшания программ, содержащее регистр прерывания, регистр защиты, схему вьшвления разрешенных прерьшанийв счетчик, дэшифратор, схему управления, сумматор, группы вет-нлейр схемы свертки, регистр ко5ггрогтьного кода защиты, схемы ИЛИ логическую схр.му регистр номера прерываш5Я и регистр контрольного кода номй 3 pa прерывашш 2, ПервглЛ вх.ои у1:ггройст ва через первую группу вентилей соединен с первой схемой свертки, 13торой аход устройства через регистр зашиты подключен к первому аходу схемы ИЛИ вторым В.ХОДОМ связанной с регистром прерывания, и через регистр к.онтро шного кода защиты - к входу сумматора, Выход схемы выявления разрешени;я прерьшаний через вторую группу вентилей соединен с первыми входами логической схемы и второй схемы свертки, вторые аходы которых подключены к схеме управления. Выход схемы ИЛИ через третью группу вентилей соединен с третьей схемой свертки Выходы второй и третьей схем свертки и первый выход логической схемы пошихючены к сумма тору, остальные аходы которого соединены, соответственно, с выходами первой схемы свертки и схемы управлеют я а вькоды сумматора соединены с регист ром контрольного кода номера прерывания и схемой управления, подключенной к второму вьвсоду логической и к второму входу регистра контрольного кода номера npepbmaifflHj один выход схемы управления соединен через счетчик и дешифратор с входами второй, третьей и четвертой групп Второй вход четвертой группы вентилей связан со схемой управления, а выход - с регистром прерывания и первой схемой свертки. Первый вход регистра номера прерывания соединен со схемой упреьлэ ния, а вход - со счетчиком, выход которого подключен к второму входу регистра номера прерьшанийе Недостатками такого устройства явля ются наличие большого каличества аппаратуры и малое быстродействие, обуслов ленное последоват&пьнььм сложением ИН формации на сумматоре, а тшснсе тема что при возникновении сбоя Ш1К отказа повторяется цикл работы устройства и только затем выдается сигнал ошибки Наибсмтбе близким по тахнической сущ ности к изобретению является устройство для прерывания программ, содержгьшее схему приоритета, аходы которой соединв ны с выходами регистра прерьюаш1й к ре гистра масок, шифратор, входы которого соединены,с входаки управлшощего эле ИЛИ и с основныкта выходаьлз схемы приоритета дополнительный внкод которой соединен с выходной шиной устpoEciBaf н суь-иматор ocHoBiibie входы которого соединень с выходами шифратора и регистра базового адреса Допол01нительный вход сумматора через элемент И соединен с выходами тршчера и управляющего элемента ИЛИ, Однако работоспособность этого устройства в процессе работы не контрапи- руетсЯф Целью изобретения является повышение достоверности работы. Это достигается тем, что в устройств во введены группа элементов ИЛИ, блок предсказания приоритетов, первый и второй пoлycy iмaтopы5 второй, третий и четвертый элементы ИЛИ, причем, инверс- шые выходы регистра прерьшаний и регистра масок-соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, четные выходы группы элементов ИЛИ соединены с четными входами блока предсказания приоритета, а не - четные вькоды группы элементов ИЛ И соединены с нечетными входами блока предсказания приоритета, прямой выход блока предсказания приоритета соединен с первым входом первого полсумматора, второй аход которого соединен с выходом второго элемента ИЛИ, аходы которого по;цшючены к нечетным выходам блока прирритета8 тшерсный выход блока предсказаний приоритета подключен к первому второго полусумматора, второй аход которого соединен с выходом третьего элемента ИЛИ, входы которого соединены с четными выходами блока приоритета. Кроме того, выходы второго и третьего элементов ИЛИ подключены соответственно к первому и втором входам первого- элемента ИЛИ, при этом, выходы первого и второго полусумматоров подключены к первому и вто- РОК-ГУ взсодем четвертого элемента И/ТИ, выход которого является третьим выходом устройства Емок предсказания приоритета содержит группу элементов НЕ, группу элементов И,, элемент НЕ и пятый элемент ИЛИ5 причем первый вход пятого элемента ИЛИ соединен с выходом первого элеме 1та НЕ группы, а остальlibie вхояы пятого элемента ИЛИ соединены с выходами элементов И группы, первые входы которых соединены, соответственно с выходами элементов НЕ группы кроме nepBorOs входы элементов НЕ группы явля10тС5Т нечетными входами блока предсказания приоритета, а четные входы биока предсказания приоритета соедине{а1 с вторыми входами элементов И группы, при этом группа входов каж до,го послэд- ощего элемента И кроме первого соединена со всеми вторыми аходами предьщущшс элементов И группы, соответственно, а аход первого элемента И группы является вторым входом блока предсказания приоритета, выход пятого элем;ента И соединен с аходом элемента НЕ и является прямым выходом блока предсказания приоритета, а выход элемента НЕ является инверсным выходом предсказания приоритета. Блок предсказа шя приоритета реализует логическую функцию )С5- Х2-Х4-)(5. ..,..Xh-1, x2-X4...Xn-i, если п четное;если Пнечетное. ... обозначение двоичных переменных, канодая из которых соответствует сигналу на выходе одного из разрядных: элементов ИЛИ группы И - максимально возможное в данной системе число запросов на пр рывание. Возможность контроля предлагаемого устройства прерывания достигается путем сравнения на полусумматорах сигнала предсказанного приоритета и сигнала, вырабатьшаемого в действительности схе мой приоритета. Блок предсказания приоритета прогнозирует приоритет запроса, подлежащий отработке, а второй и третий многоаходовые элементы ИЛИ определяю четность или нечетность реально отрабатываемого запроса, На фиг, 1 приведена схема предлагае мого устройства для прерьшания програм на фиг, 2 - схема блока предсказания пр оритета. Устройство для прерьшания программ содержит регистр 1 прерьшаний и регист 2масок, выходы которых соединены с входами блока 3 приоритета, а входы являются первым и вторым входами уст ройства соответственно. Нечетные выходы 4 блока 3 приоритета соединены с входами второго многоаходового элемента ИЛИ 5. Четные выходы 6 бпока 3приоритета соединены с входами треть го многовходового элеме1гга ИЛИ 7,,Чет ны а и нечетные выходы 6 и 4 блока 3 приоритета соединены также с входами шифратора 8. Инверсные выходы perHciv 7 1 pa 1 прерьшащ1й и регистра 2 масок соединены с входами соответствующих разрядных элемет-ов ИЛИ 9 группы, выходы которых соединены с входами блока 10 предсказания приоритета. Прямой выход 11 блока Ю предсказания приоритета соединен с первым входом первогх) полусумматора 12. Инверсньц выход 13 блока 1О предсказания приоритета соединен с первым входом второго полусумматора 14. Выходы второго и третьего многовходовых элементов ИЛИ 5 и 7 соединены соответственно с вторыми входами полусум-. маторов 12 и 14, а также с входами первого элемента ИЛИ 15, Выходы полусумматоров 12 и 14 соединены с входами четвертого элемента ИЛИ 16, выход 17 которого соединен с шиной KOHI родя к является третьим выходом уст ройства. Выходы первого элемента ИЛИ .15 и триггера 18 соединены с входами элемента И 19, выход которого соединен с третьим входом сумматора 20, Второй и первый аходы сумматора 2О соединены с выходами регистра 21 базового адреса и выходами шифратора 8, Дополнительный выход (выход отсутствия прерываний) 22 схемы 3 приоритета соэдинен с выходной шиной устройства и является первым выходом устройства. Выходы первого, второго, третьего, четвертого, И--1-го разрядных элементов. ИЛИ 9 обозначены соответственно 23, 24, 25,26 и 27, Выход сумматора второй выход устройства, аход триггера третий вход устройства, а аход регистра базового адреса - четвертый вход устройства. Блок 10 предсказания приоритета содерндат элемент ИЛИ 28, элементты 29 НЕ группы и группу элементов И ЗО, Л.ополнитвпьный вход элемента ИЛИ 28 через элемент НЕ 29 группы соединен с выходом 23 первого разрядного элемента ИЛИ 9: группьи Основные аходы элемента ИЛИ 28 соединены с выходами элементов группы И ЗО. Дополнительный вход канадого элемента группы И 30 соединен через элемент группы НЕ 29 и с выходом соответствутощего разрядного элемента групп ИЛИ 9, Вторые ходы каждого элемента И ЗО группы соединены с выходами всех чет- Hbix разрядных элементов ИЛИ 9 группы, предшествующих выбранному. Например, основной аход первого элемента И ЗО группы соединен с выходом 24 второго разрядного элемента ИЛИ 9 группы, Допоп- 77 нительный вход первого элемента 30 И группы соединен через элемент НЕ 29 с вьрсодом 25 третьего разрядного элемента ИЛИ 9 группы. Прямой вьосод элемента ИЛИ 28 является прямым выходом 11 блока Ю предсказания приори тета. Выход 13, связанный через элемент 31 НЕ с прямым вькодом: элемента ИЛИ 28 является инверсным выходом блока 1О предсказания приорит п:а. Устройство для прерьшания программ функционирует следующим образом. Нали чие запроса на прерывание фиксируется в регистре 1 прарьтаний. В регистре 2 масок по командам программы-диспатчара устанавливается код зажиты от прерываний. Единичное значение в-J-Mразряде кода соответствует разрешению прерывания. Блок 3 приоритета обеспечивает вы- деление сигнала прерьюания с более высоким приоритетом, который определяется слева направо из числа поступивших на схему сигналов прерывания, разрешенных кодом регистра 2 масок. Переход к программе прерьшания происходит при наличии соответствующего запроса и разрешения со стороны программьь-,диспатче- ра, которое фиксируется триггером 18. Выбранный сигнал запроса через второй и третий многовходовые элементы ИЛИ 5 и 7 и первый элемент ИЛИ 15 поступает на вход элемента И 19, с которого на дополнительный вход сумматора 2 О поступает управляющий с цгнал при наличии разрешающего сигнала с вьь хода триггера 18. Адрес начальной команды программы прерьшания формируется суммированием на сумматоре 20 кода номера сигнала прерьшания, который формируется шифра-i тором 8, и кода базисного адреса, расположенного в регистра 21 базисногх) адреса. Факт отсутствия незамаскированных прерьшаний отмечается наличием сигнала на выходе отсутствия прерьша- ния 22 блока 3 приоритета Устройство управления процессора перед выборкой следующей команды должно аналКЗировать состояние этого выхода,. Если сигнал на выходе 22 блока 3 приоритета есть, то выбирается очередная команда программы; если сигнала нет, то начинает выполняться операция прерывания. Ко1ггроль работоспособности производится параллельна с функционированием устройства, При этом во время спработ- ки устройством прерьшания очередного 1 запроса на прерьшание, на выходах группы разрядных злемегегов ИЛИ 9 формируется определенный Код. Поскольку входы -1 -го разрядного элемента ИЛИ 9 группы соединены с инверсными -выходами 1-го разряда регистра 1 прерьшаний И регистра 2 масок, то нуль в таком коде соответствует ситуациям, когда i-и запрос не замаскирован 1 -м триггером регистра 2 масок. Во всех других случаях в .л -м разряде кода будет присутствовать единица. Код с вькодов группы разрядных элементов ИЛИ 9 поступает на входы блока 1О предсказания приоритета. Блок 1О предсказания приоритета предназначен для того, чтобы по преобразованным элементами ИЛИ 9 группы кодам регистра 1 приоритета и регистра 2 масок определить, четный или нечетный запрос должен вьтолняться (под чет ностью или нечетностью запроса понимается его порядковый номер в регистре 1 прерьшаний). Работа блока 10 предсказания приоритета отражена в табл, 1. Таблица В этой таблице приведена погилеская функция Р от четьфех переменных. Как видно из таблицы функция , если он первая в порядке возрастания, равная нулю переменная X имеет нечетный номер, к функция Р О, если этот номер четный. Если учесть, что переменная X соответствует сигналу с выхода i-го разрядного элемента ИЛИ 9 групп нулевой уровень которого соответствует незамаскированному запросу, то станови ся ясно, что функция Р 1 в случае, если должен отрабатываться запрос, имеющий нечетный номер. Если же дсшжен отрабатываться запрос с четным но мером, то функция Р О, Для случая четырех переменных функ ция Р имеет вид: ,(2) В качестве примера рассмотрим случай, когда коды в регистре 1 приоритет регистре 2 масок и на выходах группы разрядных элементов ИЛИ 9 соответствуют приведенным в табл, 2, Таблица2 Код в регистре 1 приоритета 1О Код в регистре 2 масок11 Код на выхода.х разрядных элементов 9ИЛИ О1 Как видно из этой таблицы, не замас кированы из числа поступивших второй и четвертый запросы (ноль на выходе второго и четвертого разрядного элементов 9 ИЛИ группы). При этом, в соответствии с приоритетом, сначапа должен выполняться второй (т.е. четный запрос). При этом, из выражения (2) функция . {т,е, действительно предсказывается отработка четного запроса). Из табл. 1 видно, что коду 1111 на выходе группы разрядных элементов 9 ИЛИ группы соответствует неопредепе ное значение функции Р, Действительно, код 1111 означает, что нет ни одного незамаскированного запроса на прерьша- йие. Поскольку в общем случае поступавHHG запроса есть событие-случайное, то предсказать, какой это будет запрос (четный или нечетный) невозможно. В этом случае работа схемы контроля блокируется сигналом с выхода отсутствия прерываний 22 схемы 3 приоритета до момента появления незамаскированного запроса, В случае И переменных функция Р принимает .вид (1), Блок 1О предсказания приоритета в общем случае и реализует функцию вида (1). При этом прямой вькод 11 блока соответствует самой функции, а инверсный выход 13 ее отрицанию. Таким образом, если должен отрабатьшаться, например, нечетный запрос, то на выходе 11 блока 10 предсказания приоритета будет 1, на выходе 13 - О. При этом, при правильной работе блока 3 приоритета должен появиться сигнал на одном из его нечетных выходов 4, на его четных выходах 6 сигналы должны отсутствовать. Следовательно, на выходе второго элемента ИЛИ 5 должна быть ,1 , на выходе третьего элемента ИЛИ 7 - О, В этом случае первый и второй полусумматоры 12 и 14 не вырабатывают сигнал несоответствия и с выхода 17 четвертого элемента ИЛИ 16 в шину контроля сигнал ошибки не поступает, В случае же ошибки, например, если блоком 3 приоритета вместо нечетного запроса выберется четный, на выходе третьего элемента ИЛИ 7 появится , на выходе второго элемента ИЛИ 5 О и полусумматоры 12 и 14 выработают сигнал несоответствия, вследствин чего с выхода 17 четвертого элемет-а ИЛИ 16 в шину контроля поступит сигнал ошибки. Аналогично выявляются двойные и многократные ошибки, когда вместо одного возбуждено несколько четных и нечетных выходов блока 3 приоритета. Кроме того, выявляются также случаи отсутствия сигнала на выходах блока 3 приоритета. Действительно, на одном из выходов 11 или 13 будет присутствовать , свидетельствующая о том, четный или нечетный запрос должен отрабатываться. На выходах же элементов 5 и ИЛИ 7 будет присутствовать логический О . Следовательно, один из полусумматоров 12 и 14 выработает сигнал несоответствия и с выхода 17 четвертого элемента ИЛИ 16 в 1лину контроля поступит сигнал ошибки. ,117 Надо отмет-итьа что логическая 1 на выкоде 17 четвертого элемента 16 ИЛИ воспринимается как снгна ;. ошибки только в соотвотствующие моменты времени и при отсутствии сигна- ла на выходе 2.2. отсутствия прерьпзаний блока 3 приоритета (этот сигнал должен блокировать контроль в неопределенных ситуалиах, связанных с отс т-стни ем незамаскированньЕК запросов). В. настоящее- время устройство прерывания является обязательным функционалЬ ным элементом любой вычислительной ма шины, С его помощью в ЦВМ реализ тот-ся такие функции, как обмен информацией С внеигними устройствами, разграничение доступа и защита памятИе реакция на сиг налы аппаратурного контроля, комп,пекси рование нескольких ЦВМ и организация различных режимов их совместной работы Следовательно, от своевременного обнару жения ошибок в работе устройства преры вания зависит )ективность функционирования ЦВМ в целок. Задача контроля работоспособности решается в предпагаемом устройстве для прерьшания программ При этом предлагаемое устройство имее ряд преимуществ перед известными. Во-первых обнаруживается широкий класс ошибок, таких как нарушение дис- циплины обслуживания запросов (вмеото выбора запроса в соответствии с приоритетом выбирается запрос противоположно четности): появление пакетов ошибок (одновременно выбирается два и боль,ше запросов на прерывание) j отсутствие сигнала прерывания (в соответствии с приоритетом не выбирается ни один незамаскированный запрос), Во-вторых при достаточно высокой достоверности контроля не требуется существенных дополнительных затрат аппаратуры, так как для организации контроля необходимо реализовать несложные логические функции. В- ретьих контроль осущестзля п-ся оперативно, так как поиск ошибок производится параллельно с выполнением операции прерывания. Исходя из этого, предлагаемое уст ройство может найти широкое применение в вычислительной тахнике при проектировании систем прерывания ЦВМ, Применение такого устройства при не больших дополнительных затратах оборудования позволит повысить эффектк;вность функционирования ЦВМ з целом за счет 112 оперативного и достаточно достоверного контроля ее устройства прерывания. Формула изобрет. ения 1е Устройство для прерывания про- rpaMMs содержащее регистр прерываний, регистр маски, блок приоритета, шифраTops сумматор, регистр базового адреса, триггер, элемент И, первый элемент ИЛИ, причем вход регистра прерываний является первым входом устройства, а прямой и инверсный выходы регистра прерываний подключены соответственно к первым прямому и инверсному входам блока приоритета, вторые прямой и инверсные входы которого подключены соответственно к прямому и инвepcнo {y выходам регистра маски, вход которого является вторым аходом устройства, выход отсутствия прерываний блока приоритета является первым выходом устройства, при этом нечетные выходы блока приоритета подключены к первому входу шифратора, а четные выходы блока приоритета соединены со вторым ьходом шифратора, выход которого подключен к первому аходу сумматора, ко второму входу которого подключен выход регистра базового адреса, к третьему аходу сул1матора подключен элемент И, а выход сумматора являет- ся вторым выходом устройства, к перво-му аходу элемента И подключен выход первого элемента ИЛИ, а второй аход элемента И соединен с выходом триггера, аход которого является третьим входом устройства, при этом аход регистра базового адреса является четвертым аходом устройства, отличающее- с я тем, что, с цепью повьщ1ения достоверности работы, в него введены группа элементов ИЛИ, блок предсказания приоритетов, первый и второй полусуммато- pbis второЙ5 третий и четвертый элеме ггы ИЛИа -причем инверсные выходы регистра прерываний и регистра масок соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, четные выходы группы элеменггов ИЛИ сое- . динеиы с четными входами блока предсказания приоритета, а нечетные выходы группы элементов ИЛИ соединены с нечетными входами блока предсказания приоритета, прямой выход блока предсказания приоритета соединен с первым аходом первого полусумматора, второй вход кся-орого соединен с выходом второго элемента ИЛИ, входы которого подключены к нечетным выходам блока приоритета, инверсный выход блока предсказаний приоритета подключен к первому входу второго полусумматора, второй вход которого соединен с вькодом третье го элемента ИЛИ, входы которого соединены с четными выходами блока приори™ тета, кроме того, выходы второго и третьего элементов ИЛИ подключены соответственно к первому и BTOpoNiy аходам первого элемента ИЛИ, при этом вь ходы первого н второго полусумматоров подключены к первому и второму входам четвер-Ього элемента ИЛИ, выход которого является третьим выходом устройства 2, Устройство по п, 1, о т л и ч а ю щ е е с я тем, что блок предсказания приоритета содержит группу элементов НЕ, группу элементов И, элемент НЕ и пятый элемент ИЛИ, причем первый вход пятого элемента ИЛИ соединен с выходом первого элемента НЕ группы, а остальные входы пятого элемента ИЛИ соединены с выходами элементов И группы, первые входы которых соединены соответственно с вьскодами элеметгов НЕ 10114 группы, кроме первого, входы элементов НЕ группы являются нечетными входами блока предсказания приоритета, а четные ьходы блока предсказания приоритета соединены с Ьторыми аходами элементов И группы, этом группа входов каждого последующего элемента И кроме первого соединена со всеми вторыми входами предьздущих элементов И группы соответственно а аход первого элемента И группы является вторым входом блока предсказания приоритета, выход пятого эпеА-гента И соединен с аходом элемента НЕ и является прямым выходом блока предсказания приоритета, а выход эле мента НЕ является инверсным выходом блока предсказания приоритета. Источники информации, принятые во внимашгв при экспертизе 1,Авторское свидетельство СССР № 350О05, кл. G Об F 15/46, 1970. 2.Авторское свидетельство СССР № 3G8604, кл., Q-06 F 9/18, 1970. За Справочник по цифровой вычислительной TraLHUKe под редакцией Б, Н, Малиновского. Кизв, Техника, 1974, Сс (прототип).

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания программ | 1978 |

|

SU744575A1 |

| Устройство приоритетного прерывания | 1987 |

|

SU1495790A1 |

| Устройство для прерывания программ | 1981 |

|

SU1001103A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1979 |

|

SU783782A2 |

| Многоканальное устройство ввода информации | 1988 |

|

SU1529238A1 |

| Устройство прерывания | 1985 |

|

SU1249517A1 |

| Устройство для обработки прерываний | 1983 |

|

SU1126957A1 |

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство прерывания | 1983 |

|

SU1252776A1 |

Авторы

Даты

1980-05-25—Публикация

1978-01-05—Подача