сд к

со

1чЭ

сс

00

сов. Целью изобретения является повышение надежности. Устройство содержит блок ввода, коммутатор 2, сумматор 3 по модулю два, регистр 4, генератор 5 одиночного импульса, дешифратор- 6, блок 7 приоритета,i Повышение надежности достигается за счет организации ввода информации из каналов связи словами со сдвигом в один биТ; прерыва- НИИ ЭВМ с интервалом накопления, ор- ганизад ии каналов ввода информации, характеризующей состояние каналов связи, каналов ввода тестовой инфор- мациИр аппаратурной избыточности для контроля по четности вводимой информации. Пословный с шагом в один бит ввод информации обеспечршает программное фазирование без циклических

сдвигов слов, программный контроль ввода, так как ЭВМ имеет возможность быстрого доступа к любому начальному положению циклического синхронизма, структурному признаку информации, возможность сравнения двух соседних слов, совпадающих в разрядах при сдвиге одного из них на один бит. Прерывание ЭВМ с интервалом буферного накопления информации уменьшает затраты машинного времени на обработку прерьшаний в расчете на один бит и повышает скорость работы системы устройство ввода - ЭВМ с программной обработкой информации. При этом от ка-- нала связи требуется только обеспечение побитного синхронизма. 2 з.п. ф-лы, 5 ил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

Изобретение относится к вычислительной технике, в частности к устройствам ввода, и может быть использовано в устройствах обработки данных для ввода в ЭВМ со сдвигом в один бит слов двоичных сигналов, поступающих из каналов связи последовательным кодом в сопровождении тактовых импульсов. Целью изобретения является повышение надежности. Устройство содержит блоки 1 ввода, коммутатор 2, сумматор 3 по модулю два, регистр 4, генератор 5 одиночного импульса, дешифратор 6, блок 7 приоритера. Повышение надежности достигается за счет организации ввода информации из каналов связи словами со сдвигом в один бит, прерывания ЭВМ с интервалом накопления, организации каналов ввода информации, характиризующей состоятие каналов связи, каналов ввода тестовой информации, аппаратурной избыточности для контроля по четности вводимой информации. Пословный с шагом в один бит ввод информации обеспечивает программное фазирование без циклических сдвигов слов, программный контроля ввода, так как ЭВМ имеет возможность быстрого доступа к любому начальному положению циклового синхронизма, структурному признаку информации, возможность сравнения двух соседних слов, совпадающих в разрядах при сдвиге одного из них на один бит. Прерывание ЭВМ с интервалом буферного накопления информации уменьшает затраты машинного времени на обработку прерываний в расчете на один бит и повышает скорость работы системы "устройство ввода - ЭВМ" с программной обработкой информации. При этом от канала связи требуется только обеспечение побитного синхронизма. 2 з.п. ф-лы, 6 ил., 1 табл.

Изобретение относится к вычисли- тельной технике, в частности к уст- . ройствам ввода, и может быть использовано в устройствах обработки данньс для ввода в ЭВМ со сдвигом в один бит слов двоичных сигналов, поступаю- щих из каналов связи последователън ым кодом в сопровождении тактовых шшуль сов ,

Цель изобретения - повышение надежности устройства.

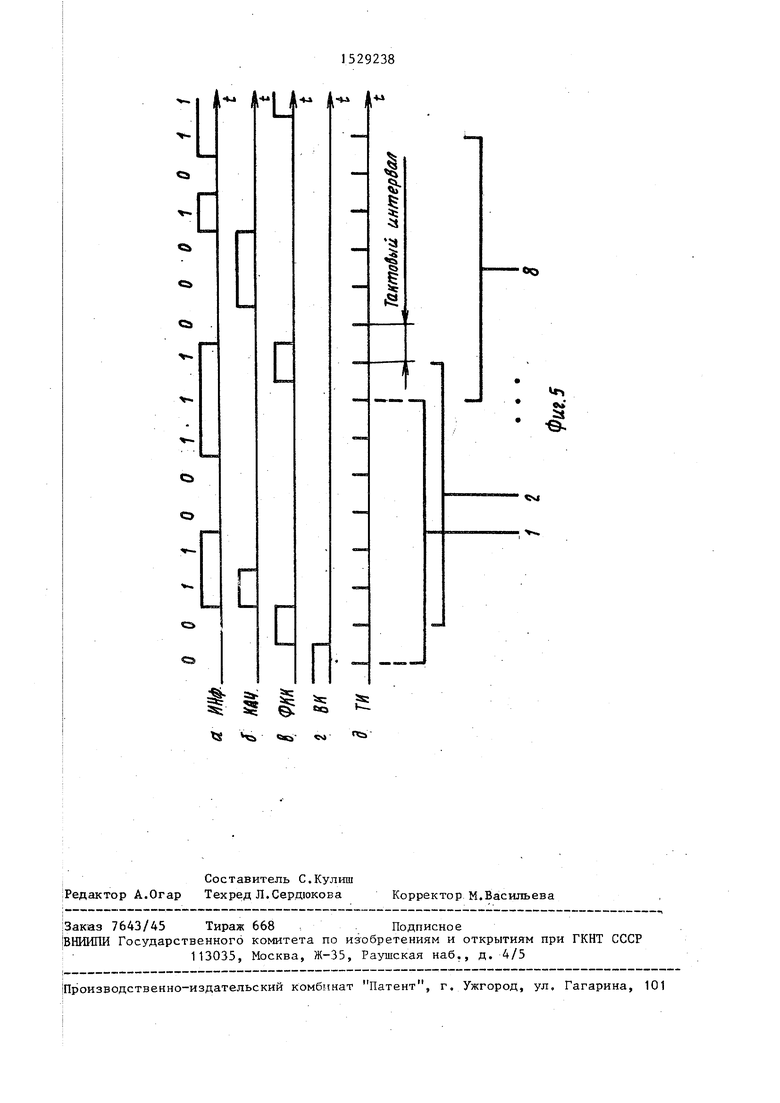

На фиг.1 приведена структурная схема устройства; на фиг.2 -- структурная схема блока ввода; на фиг.З - структурная схема блока приоритета на фиг.4 - формат, управляющего слова; - на фиг.5 -.временные диаграммы входных двоичных сигналов блока ввода. Многоканальное устройство ввода информации (фиг.. 1) содержит блоки 1 ввода, коммутатор 2, сумматор 3 по модулю два, регистр 4, генератор 5 одиночного импульса, дешифратор 6 и блок 7 приоритета. Для блоков 1 ввода Показаны первые синхровходы 8, вторые синхровходы 9, управляющие

входы 10, входы 1 выборки, выходы 12 данных и выходы 13 запроса Регистр 4 является регистром памяти, т.е. ре- .гистром с параллельным приемом и па- раллельной вьдачей, и служит для хра- нения управляющего слова устройства, снимаемого с первых и вторых выходов 14 и 15 данных регистра 4. Дхш блока 7 приоритета показаны синхровход ib.

управляющий вход 17, вход 8 выборки и адресные выходы 19.

Блоки I ввода имеют входы 20 и 21 первой и второй групп устройства.

Кроме того, на фиг. 1 обозначены первый синхровход 22 устройства, второй синхровход 23 устройства, третий синхровход 24 устройстваj управляющие входы 25 устройства, выходы 26 дан- . ных и выход 27 прерьшания.

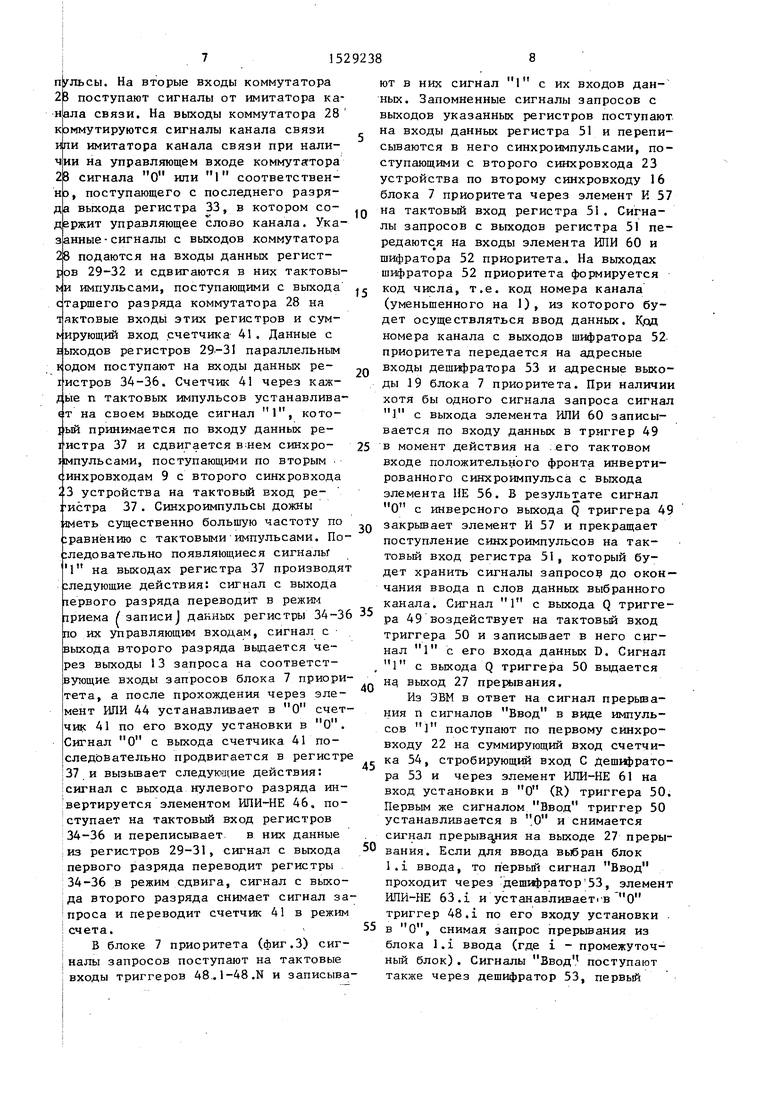

Каждьй блок 1 ввода фиг.2 содержит коммутатор 28, с первого и по одиннадцатый регистры 29-39, триггер 40j счетчик 41 первый и второй эле- менты И 42 и 43, элемент ИЛИ 44, элемент НЕ 45, элемент ИЛИ-НЕ 46 и элемент И-ЖШ 47 .

Блок 7 приоритета фиг.З образуют группа триггеров 48, первый и второй триггеры 49 и 50, регистр 51, дешифратор 52 приоритета, дешифратор 53, счетчик 54, генератор 55 одиночного импульса, элемент НЕ 56, первый и второй элементы И 57 и 58, первый и второй элементы ЙПИ 59 и 60, первый и второй элементы ИПИ-НЕ 61 и 62 и группа элементов ИЛИ-НЕ 63,

, Многоканальное устройство ввода информации из каналов связи работает следующим образом.

Данные от каналов связи по группам входов 20 или от имитаторов каналов связи (на фиг. 1 не показаны) по группам входов- 2J поступают на первую или вторую группу входов блоков

ввода соответственно. В зависимости от режима, устанавливаемого ЭВМ в казвдом из указанных блоков ввода, последние осуществляют ввод в ЭВМ данных из канала связи или от имитатора канала связи.

По входам каждой из указанных групп входов поступают последовательным кодом в виде двоичных сигналов О, 1 следующие данные канала или имитатора канала связи ( фиг.1J: по первому входу данных - информационны сигналы (И11Ф, , фиг. 5а), по второму входу данных - сигналы качества (КАЧ информационных сигналов (фиг. 5б),характеризующие степень уве зенности их приема (КАЧ О - хорошее качество, КАЧ 1 - плохое качество сопровождаемого информационного сигнала), по третьему входу данных - сигналы фазы кодовой комбинации (ФКК, фиг. 5в), следующие одновременно с первым битом кодовой комбинации с периодом циклового синхронизма, по четвертому входу данных - сигналы выключения канала (ВК, фиг. 5г), отображающие состояние канала связи (ВК О - включена, ВК 1 - выключена передяча- информационных сигналов), по тактовому входу - тактовые импульсы (ТИ, фиг. 5д),.сопровождающие двоичные сигналы данных. Сигналы КАЧ, ФКК, ВК в зависимости от вида канала связи могут отсутствовать.

Блоки 1 ввода преобразуют последовательный код данных в параллельный код данных, поступающих при вводе в ЭВМ с их выходов данных на соответствующие группы входов коммутатора 2 и после накопления очередных п бит данных каждого вида (п - емкость буфера входных данных в каждом блоке ввода) выставляют на своих.выходах сигналы запроса прерывания, поступаю- щие на соответствующие входы запроса блока 7 приоритета. Последний формирует на выходе 27 прерьшания сигнал прерывания, а на адресных выходах 19

код числа, поступающий на адресные вхрды коммутатора 2 и коммутирующий на его выходы выходы 12 данных выбранного блока 1 ввода fвыбирается блок 1 ввода с наибольшим приоритетом из вьщавших запрос на прерывание.. ЭВМ в ответ на сигнал прерывания осуществляет ввод слов данных, в которых информационные слова отличаются последовательным сдвигом информацион0

5

0

с

5

ных сигналов на один бит. При этом для ввода каждого слова ЭВМ посылает сигнал Ввод, которьй по первому сишсровходу 22 устройства на первьй синхровход блока 7 приоритета, распределяется им на первьй синхровход 8 выбранного блока 1 ввода и считьша- ет в нем слово данных на выходы 12 данных в следующем формате (фиг.1): разряды информационного слова, разряд качества кодовой комбинации КАЧ КК -, принимающий значение 1 (плохое качество КК) при наличии в информационных разрядах хотя бы одного бита плохого качества и значение О ( хорошее качество КК в противном случае, разряд ФКК для сигнала ФКК, совпадающего по времени с информационным сигналом в разряде 1П1Ф О, задержанный разряд ВК для сигнала ВК, присутствующего в момент ввода слова, разряд Режим, имеющий значение О или 1 при вводе данных из канала связи или от имитатора канала связи соответственно...

Непосредственно в ЭВМ через выходы 26 данных устройства слова вводятся в формате (фиг.1): выходные данные коммутатора 2, являющиеся описанньтми выходными данными блока 1 ввода, контрольный бит четности на выходе сумматора 3 по модулю два, принимающий значение О или 1 таким образом, чтобы сумма единиц во всех разрядах вводимого в ЭВМ слова была четной, код уменьщеиного на единицу номера выбранного блока ввода, т.е. номера канала связи или его имитатора, из которого вводится слово нумерация каналов при кодировании начинается с 0), с блока 7. Для примера в таблице приведен формат вводимых в ЭВМ слов из канала связи с номером 4 для случая N 8 (требуется трехразрядный код номера к.нала) , п 8, in 8, р 6; приведенных в таблице слова данных соответствуют входным данным из временных диаграмм на фиг.5, где N - количество каналов связи m - максимальная разрядность вводимых в ЭВМ информационных слов; п - емкость буфера входных бит данных; р - разрядность кодовой комбинации (период цик- с лового синхронизма).

В блоках 1 ввода на первые входы коммутатора 28 поступают соответственно информационные сигналы, сигна- лы качества, ФКК, ВК и тактовые им-

0

5

0

0

п гльсы. На вторые входы коммутатора 23 поступают сигналы от имитатора канала связи. На выходы коммутатора 28 коммутируются сигналы канала связи ипи имитатора канала связи при наличии на управляющем входе коммута тора 2В сигнала О или 1 соответственно, поступающего с последнего разряда выхода регистра 33, в котором со- держит управляющее слово канала. Указанные- сигналы с выходов коммутатора 28 подаются на входы данных регистров 29-32 и сдвигаются в них тактовы- импульсами, поступающими с выхода старшего разряда коммутатора 28 на тактовые входы этих регистров и сум- иpyющий вход счетчика 41. Данные с Еыходов регистров 29--31 параллельным кодом поступают на входы данных ре- хистров 34-36. Счетчик 41 через каж- f ые п тактовых импульсов устанавлива «т на своем выходе сигнал 1, кото- 1ьм принимается по входу данных ре- I истра 37 и сдвигается в:ием синхро- импульсами, поступающими по вторым синхровходам 9 с второго синхровкода i,3 устройства на тактовый вход ре- : истра 37 . Синхроимпульсы дожны чметь существенно большую частоту по сравнению с тактовыми импульсами. По шедовательно появляющиеся сигналы М на выходах регистра 37 производя :ледующие действия: сигнал с выхода первого разряда переводит в режи14 1риема f записи данных регистры 34-3 по их управляющим входам, сигнал с выхода второго разряда вьщается через выходы 13 запроса на соответствующие входы запросов блока 7 приори

тета, а после прохождения через элемент ИЛИ 44 устанавливает в О счетчик 41 по его входу установки в О. 1Сигнал О с выхода счетчика 41 по- Iследовательно продвигается в регистр |37 и вызывает следующие действия: I сигнал с выхода нулевого разряда ин- вертируется элементом ИЛИ-НЕ 46, по- I ступает на тактовый вход регистров 34-36 и переписывает в них данные :из регистров 29-31, сигнал с выхода первого разряда переводит регистры 34-36 в режим сдвига, сигнал с выхо- :да второго разряда снимает сигнал запроса и переводит счетчик 41 в режим счета.

В блоке 7 приоритета (фиг.З) сигналы запросов поступают на тактовые входы триггеров 48.. 1-48.N и записывют в них сигнал 1 с их входов данных. Запомненные сигналы запросов с выходов указанных регистров поступают на входы данных регистра 51 и перепи- сьшаются в него синхроимпульсами, поступающими с второго синхровхода 23 устройства по второму синхровходу 16 блока 7 приоритета через элемент И 57 на тактовьй вход регистра 51 . Сигналы запросов с выходов регистра 51 перед на входы элемента ИПИ 60 и шифратора 52 приоритета.. На выходах mi paTopa 52 приоритета формируется код числа, т.е. код номера канала (уменьшенного на 1), из которого будет осуществляться ввод данных. К,(Вд номера канала с выходов шифратора 52- приоритета передается на адресные входы дешифратора 53 и адресные выходы 19 блока 7 приоритета. При наличии хотя бы одного сигнала запроса сигнал 1 с выхода элемента ИПИ 60 записывается по входу данных в триггер 49 в момент действия на ::его тактовом входе положительного фронта инвертированного синхроимпульса с выхода элемента НЕ 56. В результате сигнал О с инверсного выхода Q триггера 49 закрьшает элемент И 57 и прекращает поступление синхроимпульсов на тактовый вход регистра 51, который будет хранить сигналы запросо до окончания ввода п слов данных выбранного канала. Сигнал 1 с выхода Q триггера 49 воздействует на тактовьй вход триггера 50 и записьшает в него сигнал 1 с его входа данных D. Сигнал 1 с выхода Q триггера 50 выдается на выход 27 прерывания.

Из ЭВМ в ответ на сигнал прерьша- ния п сигналов Ввод в виде импульсов поступают по первому синхровходу 22 на суммирующий вход счетчика 54, стробирующий вход С Дешифратора 53 и через элемент ИПИ-НЕ 61 на вход установки в О (R) триггера 50. Первым же сигналом Ввод триггер 50 устанавливается в .О и снимается сигнал прерывф ия на выходе 27 прерывания. Если для ввода выбран блок l.i ввода, то первьй сигнал Ввод проходит через -дешифратор 53, элемент ИЛИ-НЕ 63.1 и устанавливаетс В О триггер 48.1 по его входу установки . в О, снимая запрос прерьшания из блока l.i ввода (где i - промежуточный блок) . Сигналы Ввод , поступают также через дешифратор 53, первый

синхровход 8 блока 1 ввода на тактовые входы регистров 38 и 39, триггера 40 и через элемент ИЛИ-НЕ 46 на тактовые входы регистров 34-36, осуществляя последовательньй сдвиг данных из регистра 34 в регистр 38, из регистра 35 в регистр 39 и из регистра 36 в триггер 40. При этом в регистрах 38 и 39, триггере 40 данные сдвигаются передним фронтом, в регистрах 34-36 - задним фронтом сигналов Ввод. Счетчик 54 после счета п сигналов Ввод формирует на своем выходе сигнал 1, запускающий генератор 55 одиночного импульса, который из синхроимпульсов на сйнхровходе 16 выделяет одиночный импульс. Этот импульс проходит через элемент ИЛИ 59 и устанавливает в О счетчик 54 по его входу установки в О, а после инвертирования элементом ИПИ-МЕ 62 - регистр 51, триггер 49 по их входам установки в О, после чего сигнал I с инверсного выхода триггера 49 открывает элемент И 57. Блок 7 приоритета снова готов для обработки запросов прерьшания.

В блоках 1 ввода (фиг.2) выходы 12 данных образуются следующим образом: разряды информационного слова образуются выходами регистра 38, разряд качества кодовой комбинации - выходом элемента И-ИЛК 47, разряд ФКК - выходом триггера 40, разряд ВК - выходом последнего разряда регистра 32, разряд Режим - выходом последнего разряда регистра 33. Данные вводятся в ЭВМ словами с шагом в один бит входных данных. Элемент И-ИЛИ 47 формирует качество р-разрядной кодовой комбинации (). С этой целью выходы регистров 33 и 39 подключены попарно к входам соответствующих элементов И в элементе И-ИПИ 47. На выходах младших разрядов регистра 33 присутствуют соответственно сигналы 1 и О маски кодовой комбинации. Поэтому на выходе элемента И-ИЛИ 47 формируется сигнал 1 (плохое качество .КК) , ее- ли на выходах регистра 38 имеется хотя бы один информационный сигнал плохого качества, и сигнал О в противном случае.

Для управления работой устройства ЭВМ устанавливает на управляющих входах 25 управляющее слово в сопровождении сигнала Вьюод на третьем сйнхровходе 24. Биты управляющего слова

0

5

поступают на входы данных регистра 4 и записываются в него сигналом Вывод, действующим на тактовом входе регистра 4. Одновременно сигнал Вывод запускает генератор 5 одиночного импульса, который выделяет из синхроимпульсов на втором сйнхровходе 23 устройства одиночньй импульс, посту- Q пающий на стробирующий вход дешифратора 6. Формат управляющего блока приведен на фиг. 4. На адресные входы дешифратора 6 с выходов разрядов регистра 4 подается код нойера блока 5 ввода ипи блока приоритета, для которого предназначено управляющее слово. Если это блок приоритета, то одиночный импульс проходит через дешифратор 6, вход 18 выборки бл6ка-7 приорите- та на вход элемента И 58, на другой вход которого через управляющий вход 17 с выхода разряда регистра 4 подается признак установки в О блока 7 приоритета. Если этот признак равен 1, то сигнал I с выхода элемента И 58 проходит через элементы ИПИ 59, ИПИ-НЕ. 61-63 и устанавливает в О триггеры 48-50, регистр 51 и счетчик 54 в блоке 7 приоритета. Если управляющее слово предназначено для блока 1 ввода, то одиночный импульс проходит через дешифратор 6, вход 11 выборки этого блока ввода на входы элементов И 42 и 43. Управляющее слово блока 1 ввода с выходов 14 данных, представленных разрядами регистра 4, поступает через управляющие входы 10 на входы данньрх регистра 33 и вторые входы элементов И 42 и 43. Если в разряде регистра 4 признак загрузки маски равен 1, то сигнал 1 с вы- , хода элемента И 42 поступает на тактовый вход регистра 33 и записьшает в него маску кодовой комбинации. Если в разряде регистра 4 признак установки в О равен 1, то сигнал 1 с выхода элемента И 43 проходит через элементы ИПИ 44 и НЕ 45 и устанавливает в О счетчик 41 , регистры 29- 32, 34-39 и триггер 40 в блоке 1 ввода.. Формула изобретения 1. Многоканальное устройство ввода информации, содержащее блоки ввода, коммутатор, блок приоритета, информационные выходы блоков ввода под слюче- ны к информационным входам коммутато- , ра, выходы запроса блоков ввода подключены к входам запроса блока приорите0

5

0

5

0

5

, адресные выходы КОТОРОГО соедингны с здресными входами KOhSMyxaTopas информационные входы первой группы блоков звода являются входами первой группы устройства, выходы коммутатора и ад- зесные выходы блока приоритета является соответственно выходами данных и адресными выходами устройства, выход прерьшания блока приоритета является ВЫХОДОМ прерьшания устройства, отлич ающе е ся тем, что, с целью повышения надежности устройства, в него введены регистр, дешифратор, генератор одиночного импульса и сумматор по модулю два, входы которого соединены с выходами коммутатора и с адресными выходами блока приоритета,, информационные- входы регистра являются управляющими входами устройства, второй синхровход блока приоритета соединен с вторыми синхро- входами блоков ввода, информационным входом генератора одиночного импульса и является вторым синхровходом устройства, тактовьм вход регистра соединен с входом запуска генератора одиночного импульса и является тре- тьим синхровходом устройства, одни вьпсоды регистра соеди1-2ены с управляющими входами блоков ввода, другие вы ходы регистра соединены с соответст-вующими адресными входами дешифратора, выход генератора одиночного импульса соединен со стробирующим входом дешифратора, один выход которого соединен с в.хрдом выборки блока приоритета, другие , выходы дешифратора , соединены с входами выборки соответ ствующих блоков ввода, информационные входы второй группы блоков ввода являются входами второй группы устройства, синхровыходы блока приоритета соединены с первьми сш1хровходами соответствующих блоков ввода, выход сумматора по модухЕЮ два является контрольным выходом устройства, управляющий вход блока приоритета подключен к соответствующему выходу регистра, первый синхровход блока приоритета является первым синхровходом устройства,

5

0

5

0

5

D

5

0

рые входы коммутатора являются соответственно информационными входами первой.и второй групп блока ввода, управляющий вход коммутатора соединен с выходом последнего разряда пятого регистра и является выходом данных блока ввода, первый вход элемента ИПИ-НЕ соединен с тактовыми входами десятого и одиннадцатого регистров и триггера и является первым синхровходом блока ввода, тактовьм вход девятого регистра является вторым синхровходом блока ввода, входы данных пятого регистра и первые входы первого и второго элементов И являются управляющими входами блока ввода, вторые входы первого и второго элементов И соединены и являются входом выборки блока ввода, выходы десятого регистра, выход элемента И-ИЛИ, прямой выход триггера и выход последнего разряда четвертого регистра являются информационными выходами блока ввода, выход второго разряда девятого регистра соединен с первым входом элемента ИЛИ и является выходом запроса блока ввода, первьй, второй, третий и четвертый выходы коммутатора соответственно соединены с входами данных первого, второго, третьего и четверг- того регистров, четвертый выход коммутатора соединен с тактовыми входами первого, второго, третьего, четвертого регистров и с суммирующим входом счетчика, вход установки в О кото-. рого соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и с входом элемента НЕ, выход первого элемента И соединен с тактовым входом пятого регистра, выход элемента НЕ соединен с входами установки в О с первого по четвертьй, с шестого по одиннадцатый регистров и триггера, выходы первого, второго и третьего регистров соединены соответств.енно с входами данных шестого, седьмого и восьмого регистров, тактовые и управляющие входы которых соединены соответственно с выходом элемента ИЛИ-ЫЕ и с выходом первого разряда девятого регистра, вьЬсод счетчика соединен с входом данных девятого регистра, выход нулевого разряда которого соединен с вторым входом элемента ШИ-НЕ, выходы пятого регистра, кроме последнего, соединены соответственно с первыми входами элемента, И-ИЛИ, вторые входы которого

соединены соответственно.с выходами одиннадцатого регистра, выходы шестого, седьмого и восьмого регистров соединены соответственно с входами данных десятого, одиннадцатого регистров и триггера.

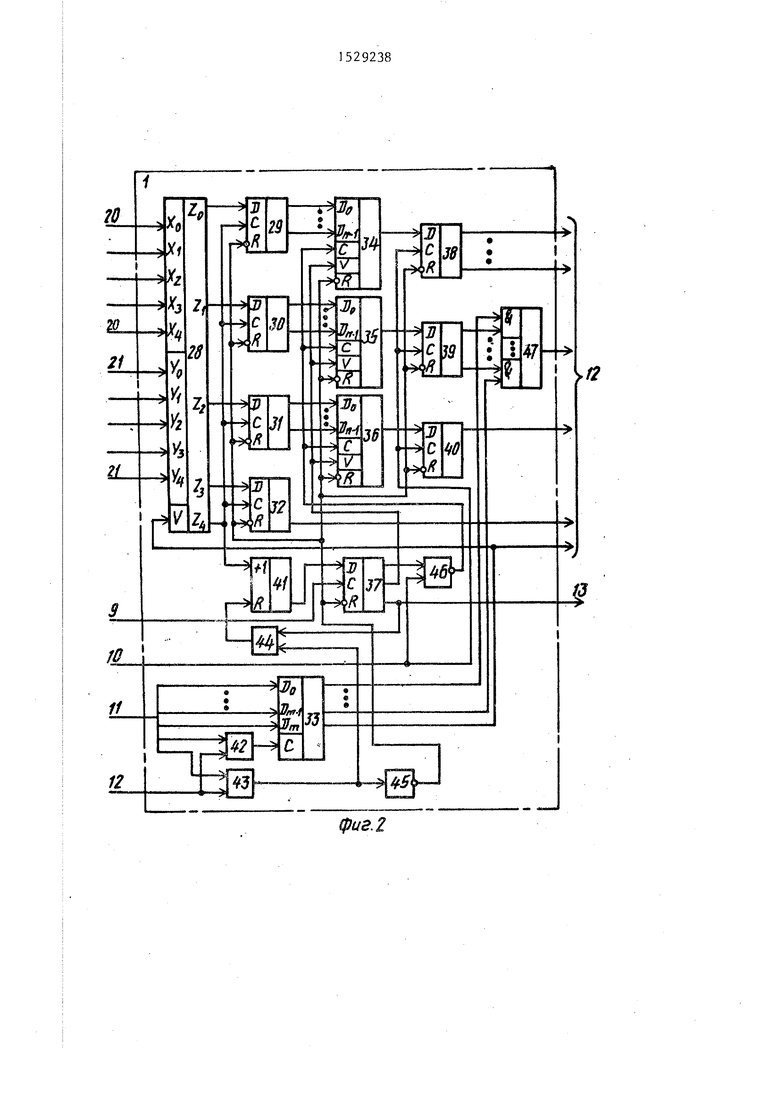

Формат вводимого в ЭВМ слова из канала связи 4 (, , )

0

5

о

0

5

5

которого соединен с выходом первого элемента К, входы установки в О регистра, первого триггера соединены с вЫходом второго элемента ИЛИ-НЕ, вход установки в О второго триггера соединен с выходом первого элемента ИПИ-НЕ, выходы регистра соединены соответственно с входами шифратора и второго элемента ИЛИ, выход которого соединен с входом данных первого триггера, прямой выход первого триггера соединен с тактовым входом второго триггера, вход данных которого соединен с потенциалом логической 1 устройства, инверсньй выход первого , триггера Соединен с вторым входом первого элемента И, вход установки в О счетчика соединен с выходом первого элемента ИЛИ, выход счетчика соединен с информационным входом генератора одиночного импульса, выход которого соединен с первыми входами первого элемента ИЛИ и второго элемента ИЛИ-НЕ, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, с вторыми входами пер- вого и второго элементов ИЛИ-НЕ и с первыми входами группы элементов .ИЛИ- НЕ, вторые входы которых соединены соответственно с выходами дешифратора и являются снихровыходами блока приоритета, вьгход элемента НЕ соединен с тактовым входом первого триггера, прямой выход второго триггера является выходом прерывания блока приоритета, выходы шифратора соединены соответственно с информационными входами дешифратора и являются адресными выходами блока приоритета.

фие.2

Разряды geipeSflfHimeto c/ioSa

«о ец 1

О

min

mt-i

m-i-2

I Разряды маеяи дая ynsjaHUft uHtpopMuifuoffMu (8риряЗв 1) иаи неинформа1{ионной(еразряде-о) I no3utfuu UHqiffpMai/uoHHOio cyjoSa

Ре if им ра/оти fflo/ta 88сдв (0-SSo3om канала cf/tJU

1-SSff3 от имитаторо канала cSgju). Г.ризнак je pyjKu под о Sou ком(Гинас и.и t cTjJffft BSoda ( f-3 tгpc/Jfca О - нет sazpifs u}

признак уста и. ff 0 f/fOKce ввода,приорит8

та(1-устан. ff О O-nfm устан. S о).

КеЗ HffMe a Лбка ббоЗа, приоритета приоритета, Ktf$ чис/га /,..., i-zo, ..., S8o3a).

Фиг. if

2S: 5 э Ча «ass «

| в^-?О;>&ЮЗНД?? ] ЙАТЬЯТш-ГЕХШ^ИЕ^ЖЖ БИГ^ПИОТ^НА ; | 0 |

|

SU379923A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авдеев Н.Ф | |||

| и др | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| М.: ИТЭФ, 1984, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-28—Подача