1

Изобретение относится к радиотехнике и может быть использовано в схемах фазовой автоподстройки систем стабилизации дискретных частот цифровых синтезаторов частоты.

Известный делитель с переменным коэффициентом деления, содержащий счетчик с постоянным коэффициентом пересчета и первый счетчик с переменным коэффициентом пересчета с первой схемой установки, входы которых через схемы совпадения связаны с источником входного сигнала и с выходам.и триггера коммутации, обладает низким быстродействием.

Цель изобретения - повып1е.ние быстродействия делителя.

Для этого в делитель введены триггер управления, инвертор, четыре логических схемы «И, схема «ИЛИ и второй счетч.ик с переменным коэффициентом пересчета и со второй схемой установки, вход которого подключен к выходу счетчика с лостояиным коэффициентом пересчета через первую схему «И, второй вход которой соединен с одним выходом триггера управления, один вход которого подключен к выходу второго счетчика, а второй выход связа.н со входами второй и третьей схем «И, вторые входы которых соединены с выходом счетчика с постоянным коэффициентом пересчета, и со входом четвертой схемы «И, другой вход кото-рой через

схему «ИЛИ нодключен к выходу первого счетчика с неременным коэффициентом пересчета и к выходу третьей с.хемы «И, третий вход которой соединен с одним из выходов первой схемы установки, который через инвертор связан с третьим входом второй схемы «И, выход которой подключен к одному входу триггера коммутации, причем вторые входы триггеров управления и коммутации

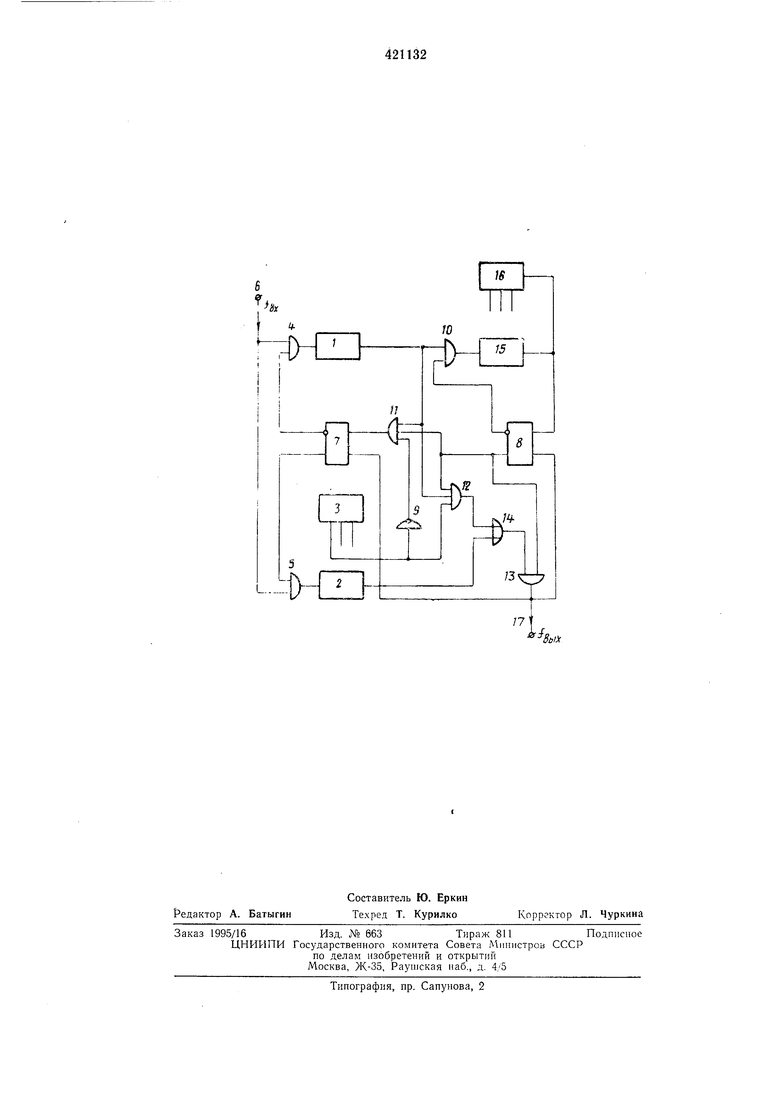

подключены к выходу четвертой схемы «И. На чертеже представлена блок-схема предлагаемого делителя.

Делитель содержит счетчик 1 с постоянным коэффициентом пересчета, первый счетчик 2 с

переменным коэффициентом пересчета с первой схемой 3 установки, входы которых через схемы 4 н 5 совпадения связаны с нсточником входного сигнала (клемма 6) и с выходами триггера 7 коммутации. В схеме имеются также триггер 8 унравления, инвертор 9, логические схемы «И 10-13, схема «ИЛИ 14, второй счетчик 15 с переменным коэффициентом пересчета н со второй схемой 16 установки. Вход счетчика 15 соединен с выходом счетчика 1 через схему «И 10, второй вход которой соединен с одним из вы.ходов триггера 8 унравления. Один вход носледнего подсоединен .к выходу счетчика 15, а второй выход связан со входами схем «И 12 н 11. Вторые входы схем «И 12 и 11 соединены с выходом

счетчика 1 с постоянным КоЭ|ффициентом пересчета и со входом схемы «И iS. Другой вход схемы «И 13 через схему «ИЛИ 14 подключен к выходу счетчика 2 и к выходу схемы «И :12, третий вход которой соединен с одним из выходов схемы 3 установки, который через инвертор 9 связан с третьи м входом схемы «И 11, выход которой подключен к одному входу триггера 7 коммутации. Вторые входы триггеров 7 и i8 подсоединены к выходу схемы «И 13.

Делитель работает следующим образом.

Импульсы с частотой следования /вх через схему 4 совпадения поступают на вход счетчика 1, имеюи1,его коэффициент пересчета AI. С выхода счетчика 1 импульсы уже с ча.стотой следования /nx/Ai через схему «И 10 поступают на вход счетчика 45, у которого с помощью схемы 16 установки коэффициент пересчета Л2 устанавливается ,на единицу .меньше, чем целая часть частного от деления требуемого коэффициента деления делителя (Л/д) на коэффициент пересчета счетчика 1;

/V, .. л,

1.

После появления импульса на выходе счетчИКа 15 производится еще один цикл подсчета входных импульсов счетчиком 1. За это время и.мнульс с выхода счетчика, ,15 переводит триггер в из состояния «О в состояние при этом сигнал разрешения подается на один из ВХОДОВ схем .«И , и снимает,ся с выхода схемы «И 10, а также осуществляется уста,новка счетчика 15 в необходимое исходное состояние с .помощью схемы 16 установки.

В случае, когда Л/д пе кратен NI, первый после появления выходного ямпульса счетчика 15 импульс на выходе счетчика 1 через схему «И il 1 устанавливает триггер 7 в состояние «1. Триггер 7 должен обладать максимальным быстродействием, чтобы до прихода очередного входного импульса перекоммутировать схемы 4 и 5 совпадения и переключить входные импульсы со входа счетчика I на вход счетчика 2.

Счетчи-к 2 производит только досчет количества импульсов, рав.пых остатку от деления //д/yVi, поэто.му коэффициент пересчета счетчика 2 устанавливается схемой 3 устаиовки в пределах от 1 до (). Имлульсы с выхода счетчика 2 через схемы «И l3 и «ИЛИ 14 проходят на выход делителя (клемму 17) и одновременно переводят триггеры 7 и 8 в состояние при этом входные импульсы через схему 4 -совпадения начнут поступать на вход счетчика Л, а его выход через схему «И 10 подключается ко входу счетчика 15. Далее начинается новый цикл работы делителя, причем установку необходимого коэффициента пересчета счетчика 2 можно производить за время заполнения счетчика ilS.

При кратных коэффициентах Л/д и NI остаток от их деления равен нулю, поэто.му сигнал на выходе делителя должен быть сразу же носле появления импульса на выходе счетчика 1 npHi наличии на выходе счетчика 15 сигнала разрешения. При этом не срабатывает

триггер 7, поскольку с нулевого выхода схемы 3 установки чеерз инвертор 9 поступает сигнал запрета на схему «И 10. Счетчик 2 также не работает. Одновременно с нулевого выхода схемы 3 установки сигнал поступает «а

один вход схемы «И 12, на, другом входе которой уже имеется сигнал с едии,ич.ного выхода триггера 8. Поэтому при появлении на выходе счетчика 1 импульса последний проходит через схему «И 12, схему «ИЛИ 14 и схему

«И 13 на выход делителя (клемму 17) с задержкой, обусловленной только временем срабатывания этих элементов.

Предмет изобрете;ния

Делитель с переменным .коэффициентом деления, содержащий счетчик с постоянным коэффициентом пересчета и первый счетчик с

переменным коэффициентом пересчета с первой схемой установки, входы которых через схемы совпадения связаны с источником входного сигна.ла и с выхода.ми триггера коммутации, отличающийся тем, что, С целью

повышения быстродействия, в него введены триггер управления, инвертор, четыре логических схемы «И, схема «ИЛИ и второй счетчик с переменным коэффициентом пересчета и со второй схемой установки, вход которого

подключеи к выходу счетчика с постоянным коэффициентом пересчета через первую схему «И, второй вход которой соединен с одним выходом триггера управления, один вход которого подключен к выходу второго Счетчика,

а второй выход связан со входами второй и третьей схем «И, вторые входы которых соединены с выходо,м счетчика с постоянным коэффициентом пересчета, и со входом четвертой схемы «И, другой вход которой через

схему «ИЛИ подключен к выходу первого счетчика с переменным .коэффициентам пересчета, и к выходу третьей схемы «И, третий вход которой соединен с одним из выходов первой схемы установки, который через инвертор связан с третьим входом второй схемы «И, выход которой подключен к одному входу триггера ко.ммутации, причем -вторые входы триггеров управления и коммутации подключены ко входу четвертой схемы «И.

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1982 |

|

SU1072266A1 |

| Делитель частоты с переменнымКОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU801254A1 |

| Устройство для управления инвертором | 1990 |

|

SU1709482A1 |

| Управляемый цифровой делитель частоты для систем фазовой автоподстройки частоты | 1976 |

|

SU569001A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1812636A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1732465A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Анализатор временных интервалов между импульсами | 1980 |

|

SU900431A1 |

| Делитель частоты с переменным коэффициентом деления | 1973 |

|

SU482898A1 |

Даты

1974-03-25—Публикация

1972-06-20—Подача