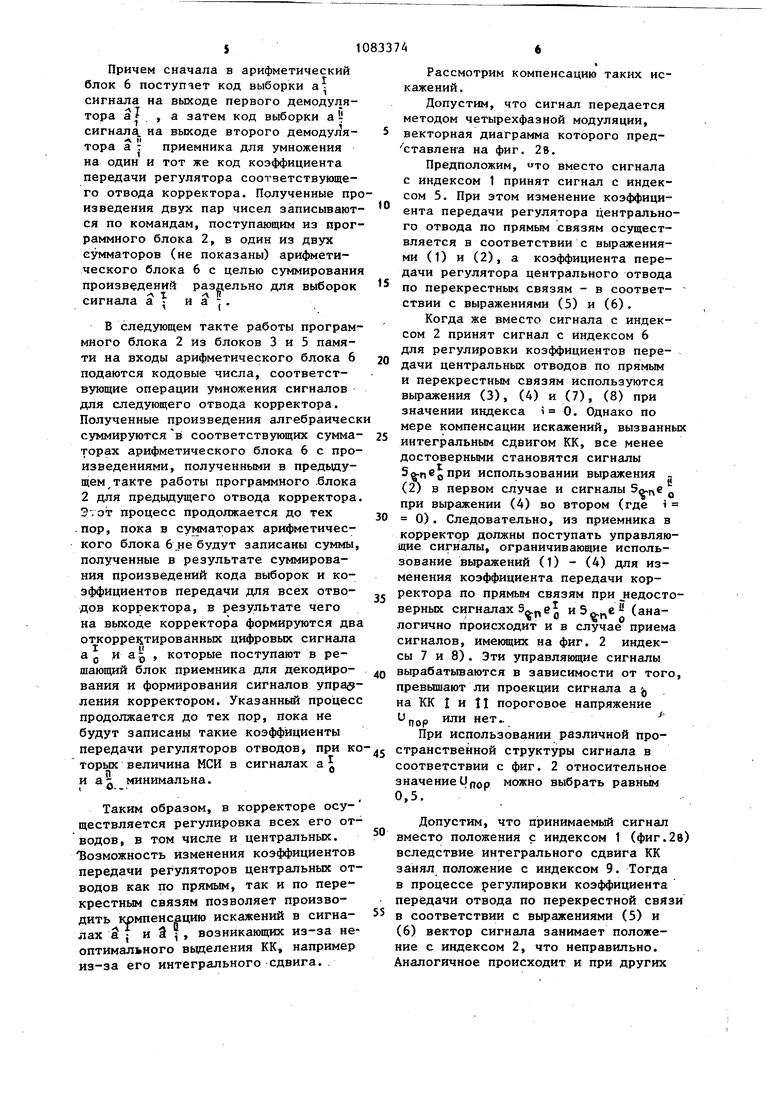

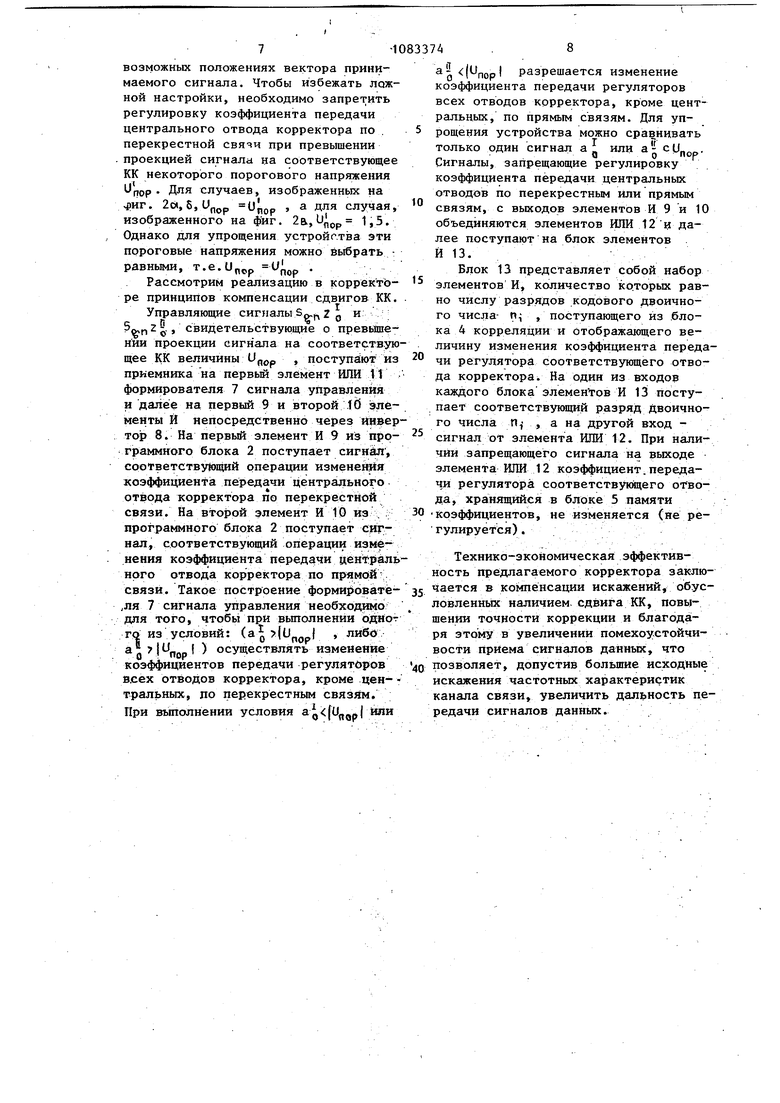

Изобретение относится в электросвязи и может быть использовано для коррекции межсимвольной интерференции (МСИ) в модулированных сигналах передаваемых многопозиционными методами фазовой мбдуляции. Известен цифровой адаптивный корректор межсимвольной интерференции, содержащий последовательно соединенные блок памяти выборок и арифметический блок, выход которого является выходом устройства, вход которого через блок памяти полярностей И знака отклонения амплитуды сигнала от номинала подключен к блоку корреляции, выход которого через блок памяти коэффициентов подключен к другим входам арифметического блока и блока корреляции 1 . Однако точность коррекции такого устройства недостаточна. Наиболее близким к предлагаемому является цифровой адаптивный корректор межсимвольной интерференции, содержащий последовательно соединенные аналого-цифровой преобразователь блок памяти выборок и арифметический блок, а также программный блок, выход которого соединен с другим Владом блока памяти выборок, с вторым входом арифметического блока и первым входом блока памяти коэффициентов, выход которого соединен с третьим входом арифметического бпока, первый выход которого является . выходом устройства, а второй выход соединен с первым входом блока корре ляции, второй вход которого соединен с вторым выходом блока памяти выборок, при этом входы аналого-цифрового преобразователя, программного о блока и третий вход блока корреляции являются входами устройства С2Д. Однако известный корректор обеспечивает недостаточно высокую помехоустойчивость приема сигнала в условиях неоптимального выделения ко. герентного колебайия (КК) в результате снижения точности коррекщадь., Цель изобретения - повьшение точности адаптивной коррекции межсимвольной интерференции путем компенсации искажений, возникающих вследствие интегральных сдвигов КК. Поставленная цель достигается тем, что в цифровой адаптивный корректор межсймвольной интерференции, содержащий последовательно соединенные аналого-цифровой преобразователь блок памяти выборок и арифметический блок, а также программный блок, выход которого соединен с другим входом блока памяти выборок, с вторым входом арифметического блока и первым входом блока памяти коэффициен.тов, выход которого соединение третьим входом арифметического блока, первьм выход которого является выходом устройства, а второй выход соединен с первым входом блока корреляции, второй вход которого соединен с вторым выходом блока памяти выборок, при этом входы аналого-цифрового преобразователя, программного блока и третий вход блока корреляции являются входами устройства, введен формирователь сигнала управления, состоящий из последовательно соединенных первого элемента ИЛИ, входы которого являются входами устройства, инвертора, первого элемента И, второго элемента ИЛИ, блока элементов И, выход которого соединён с вторым входом блока памяти коэффициентов, второго элемента И, первьй вход которого соединен с выходом первого элемента ИЛИ, а второй вход соединен с вторым выходом программного блока, третий выход которого соединен с вторым входом первого элемента И, при этом выход второго элементами соединен с вторым входом второго элемента ИЛИ, второй вход блока элементов И соединен с выходом блока корреляции. На фиг. 1 представлена структурная электрическая схема предлагаемого корректора; на фиг. 2 - векторные диаграммы. Цифровой адаптивный корректор межсимвольной интерференции содержит аналого-цифровой преобразователь 1i, программньй блок 2, блок 3 памяти выборок, блок 4 корреляции, блок 5 памяти коэффициентов, арифметический блок 6, формирователь 7 сигнала управления, инвертор 8, первый 9 и второй 10 элементы И, первьй 11 и второй 12 элементы РШИ, блок элементов И 13. Устройство работает следующим образом. На фиг. 2 изображены возможные Положения вектора при различной пространственной структуре сигналов. При этом точками показаны возможные идеальные положения конца вектора 310 принимаемого сигнала. На фиг. 2в .эти положения показаны цифрами 1-4. На фиг. 2c,S цифрами I и Ц показана относительная величина проекции сигнала на КК; а на фиг. 2в она равна 3. Прием сигналов данньпс осуществляется посредством двух демодуляторов, расположенных в приемнике (не показаны) . Корректор осуществляет кор:рекцию как синфазньк (собственных), так и квадратурных (перекрестных) компонентов МСИ, Корреляция МСИ адаптивным корректором проводится в соответствии со следующим аЛгоритMOM:при компенсации синфазного (собственного) мешающего влияния .1с I г v-eo«f .S n o0S n«o®S n«n t.«c ef«f «f V f n o0 n«j©V при компенсации квадратурного (перекрестного) мешающего влияния с t, Q ,« +S. g-n®o©5 n«i (8 V « ( - знаки проекций .сигналов, подверженных мешаю щему . влиянию на КК 1 и II соответственно;За. и5..с(- - знаки проекций сигналов, созда щих мешаю1Ю1е влияния, на КК и 11 соответственно; . и S е - - знаки отклонени п о амплитуд сиг|1аот номинала от- щих модулям и полярностям кодов выносительно КК I борки а и а | коэффициента пеи11 соответст- редачи соответствующего регулятора венно;отвода корректора. /-J - величина проекции сигналов,создающих мешающие влияния на КК 1 и II соответственГ 7 ° CQ И е И - величина проекции отклонения амплитуды сиггталов а сн и а от номинала на КК 1 и II соответственно. Для реализации алгоритма адаптивной коррекции достаточно использовать только две пары выражений: либо (1), (2), (5), (6), либо (3), (4), (6), (8). На основании выражений (1), (3), (5) и (7) определяется величина изенения коэффициент а- передачи h соответствующего регулятора отвода корректора, а на основании выражеНИИ (2), (4), (6), (8) - знак этого изменения (5 п, ). u- Формирование сигналов , | i п , J / л /ч Ь и Т1 по выражениям (.) (3), (5) и (7) осуществляется в арифметическом блоке 6.. Эти сигналы поступают в блок 4 корреляции и обозначены на фиг. 1 как п; . Для формирования сигнала Зо-.Ь;} с I с поступают сигналы -р-о о .o и S а: с выходов приемника и сигналы Ьо-« с выходов V Ч| блока 3 памяти выборок. По командам программного блока 2 и в соответствии с использованным среднеквадратичным алгоритмом настройки адаптивного корректора, в блоке 4 корреляции вырабатываются сигналы о величине и знаке изменения коэффициента передачи соответствующего отвода, которые в виде п-разрядньк чисел хранятся в блоке 5 памяти коэффициентов. В каждом такте работы программного блока 2 из блоков 3 и 5 памяти в блок умножения арифметического блока 6 поступают два rt -разрядных кодовых числа, соответствуюПричем сначала в арифметический блок 6 поступчет код выборки а сигнала на выходе первого демодулятора а| , а затем код выборки аJ сигнала на выходе второго демодулятора а 7 приемника для умножения на один и тот же код коэффициента передачи регулятора соответствующего отвода корректора. Полученные пр изведения двух пар чисел записывают ся по командам, поступающим из прог раммного блока 2, в один из двух сумматоров (не показаны) арифметического блока 6 с целью суммировани произведений раздельно для выборок ТЛГИТвТТ г ТTi О сигнала а В следующем такте работы програм много блока 2 из блоков 3 и 5 памяти на входы арифметического блока 6 подаются кодовые числа, соответствующие операции умножения сигналов для следующего отвода корректора. Полученные произведения алгебраичес суммируются в соответствующих сумма торах арифметического блока 6 с про изведениями, полученными в предыдущем такте работы программного .блока 2 для предьщущего отвода корректора Э от процесс продолжается до тех .пор, пока в сумматорах арифметического блока будут записаны суммы полученные в результате суммирования произведений кода выборок и коэффициентов передачи для всех отводов корректора, в результате чего на выходе корректора формируются дв откорре1(;тированных цифровых сигнала которые поступают в реи а- , шающий блок приемника для декодировайия и формирования сигналов упра ления корректором. Указанный процес продолжается до тех пор, пока не будут записаны такие коэффициенты передачи регуляторов отводов, при ко торых величина МСИ в сигналах а и а минимальна. Таким образом, в корректоре осуществляется регулировка всех его отводов, в том числе и центральных. Возможность изменения коэффициентов передачи регуляторов центральных отводов как по прямым, так и по пере крестным связям позволяет производить компенсацию искажений в сигналах S j и 3 , возникающих из-за неоптимального выделения КК, например из-за его интегрального сдвига. Рассмотрим компенсацию таких искажений. Допустим, что сигнал передается методом четырехфазной модуляции, векторная диаграмма которого представлена на фиг. 2в. Предположим, «то вместо сигнала с индексом 1 принят сигнал с индексом 5. При этом изменение коэффициента передачи регулятора центрального отвода по прямым связям осуществляется в соответствии с выражениями (1) и (2), а коэффициента передачи регулятора центрального отвода по перекрестным связям - в соответствии с выражениями (5) и (6). Когда же вместо сигнала с индексом 2 принят сигнал с индексом 6 для регулировки коэффициентов передачи центральньк отводов по прямым и перекрестным связям используются вьфажения (3), (4) и (7), (8) при значении индекса i 0. Однако по мере компенсации искажений, вызванных интегральным сдвигом КК, все менее достоверными становятся сигналы использовании выражения . (2) в первом случае и сигналы о при выражении (4) во втором (где i 0). Следовательно, из приемника в корректор должны поступать управляющие сигналы, ограничивающие использование выражений (1) - (4) для изменения коэффициента передачи корректора по прямым связям при J eдocтoверных сигналах (анаогично происходит и в случае приема сигналов, имеющих на фиг. 2 индексы 7 и 8). Эти управляющие сигналы ырабатьтаются в зависимости от того, ревышают ли проекции сигнала а j, а КК I и II пороговое напряжение или нет.. При использовании различной пространственной структуры сигнала в соответствии с фиг. 2 относительное значение и pop можно выбрать равным Допустим, что принимаемый сигнал вместо положения с индексом 1 (фиг.2в) вследствие интегрального сдвига КК занял положение с индексом 9. Тогда в процессе регулировки коэффициента пер(гдачи отвода по перекрестной связи в соответствии с выражениями (5) и (6) вектор сигнала занимает положение с индексом 2, что неправильно. Аналогичное происходит и при других возможных положениях вектора принимаемого сигнала. Чтобы избежать ложной настройки, необходимо запретить регулировку коэффициента передачи центрального отвода корректора по перекрестной свячи при превышении проекцией сигнала на соответствующее КК некоторого порогового напряжения пор Д- случаев, изображенных на ИГ. 2«,5, Unop : , а для случая, 2u,U;,p 1.5. изображенного на фиг. Однако для упрощения устройства эти пороговые напряжения можно выбрать : т.е.и„„„ и равными, ...«прр .f,p Рассмотрим реализацию в корректоре принципов компенсации сдвигов КК. Управляющие сигналы Sg, 2 g и ; с свидетельствующие о превьйпении проекции еигнала на соответс.твую щее КК величины и , поступают из приемника на первый элемент ИЛИ |1 формирователя 7 сигнала управления и далее на первый 9 и второй IЬ элементы И непосредственно через иивер тар 8. На первый элемент И 9 из программного блока 2 поступает сигнйл, соответствуйщий операции изменения коэффициента передачи центрального отвода корректора по перекрестили связи. На второй элемент И 10 из программного блока 2 поступает сигнал, соответствующий операции изменения коэффициента переда1чи централь ного отвода корректора по прямо1Й связи. Такое построение формир овате,ля 7 сигнала управления необходи14о для того, чтобы при выполнении однот го из условий: (а(и,др| , либо а осуществлять изменение коэ нциентов передачи регулятйров всех отводов корректора, кроме центральных, по перекрестным связям. При вьтолнении условия ao( или разрешается изменение коэффициента передачи регуляторов всех отводов корректора, кроме центральных, по прямым связям. Для упрощения устройства можно сравнивать только один сигнал а или а- c(J Сигналы, запрещающие регулировку коэффициента передачи центральных отводов по перекрестным Или прямым связям, с выходов элементов И 9 и 10 объединяются элементов ИЛИ 12 и далее поступаютна блок элементов И 13. Блок 13 представляет собой набор элементов И, количество которых равно числу разрядов кодового двоичнопоступающего из .блого числа- п ка 4 корреляции и отображающего величину изменения коэффициента передачи регулятора соответствующего отвода корректораi На один из входов каждого блока элементов И 13i поступает соответствующий разряд двоичного числа п,- , а на другой вход сигнал от элемента ИЛИ 12. При наличии запрещающего сигнала на выходе элемента ИЛИ 12 коэффициент.передачи регулятора соответствующего отвода, хранящийся в блоке 5 памяти коэффициентов, не изменяется (не регулируется) . Технико-экономическая эффективность предлагаемого корректора заключается в компенсации искажений, обусловленных наличием, сдвига КК, повышении точности коррекции и благодаря этому в увеличении помехоустойчивости приема сигналов данных, что позволяет, допустив большие исходные искажения частотных характеристик канала связи, увеличить дальность передачи сигналов данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой адаптивный корректорСигНАлА | 1978 |

|

SU832733A1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Корректор межсимвольных искажений | 1984 |

|

SU1220130A1 |

| Цифровой адаптивный корректор межсимвольных искажений в сигналах данных | 1979 |

|

SU921099A2 |

| Цифровой корректор сигналов | 1979 |

|

SU862366A1 |

| Устройство для адаптивной коррекции межсимвольных искажений | 1981 |

|

SU951725A1 |

| Цифровой адаптивный корректор меж-СиМВОльНыХ иСКАжЕНий B СигНАлАХ дАН-НыХ | 1978 |

|

SU801269A1 |

| Адаптивный корректор сигнала | 1978 |

|

SU794735A1 |

| Устройство для адаптивной коррекции межсимвольной интерференции | 1981 |

|

SU951724A1 |

| Цифровой адаптивный корректор | 1986 |

|

SU1417196A1 |

ЦИФРОВОЙ АДАПТИВНЬЙ КОРРЕКТОР МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ, содержащий последовательно соединенные аналого-цифровой преобразователь, блок памяти выборок и арифметический блок, а также программный блок, выход которого соединен с другим входом блока памяти выборок, с вторым входом арифметического блока и первым входом блока памяти коэффициентов, выход которого соединен с третьим входом арифметического блока, первый выход которого является выходом устройства, а второй выход соединен с первым входом блока корреляции, второй вход которого соединен с вторым выходом блокапамяти выборок, при этом входы аналого-цифрового преобразователя, программного блока и третий вход блока корреляции являются, входами устройства, отличающийся тем, что, с целью повышения точности адаптивной коррекции межсимвольной интерференции, введен формирователь сигнала управления, состоящий и: последовательна соединенных первого элемента ИЛИ, входы которого являются входами устройства, инвертора, первого элемента И, второго элемента ИЛИ, блока элементов И, выход 1 которого соединен с вторым входом блока памяти коэффициентов, второго (Л элемента И, первый вход которого соединен с выходом первого элемента ИЛИ, а второй вход соединен с вторым выводом программного блока, третий выход которого соединен с вторым входом первого элемента И, при этом вькод второго элемента И соединен с эо вторым входом второго элемента ИЛИ, :о :/s второй вход блока элементов И соединен с вьгходом блока корреляции. vl

Ж

т

и

t

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3727136, кл | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3633105, кл | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

Авторы

Даты

1984-03-30—Публикация

1982-12-14—Подача