1

Изобретение относится к технике электросвязи и может использоваться в устройствах, связанных с приемом модулированных сигналов данных, передаваемых по каналам тональной частоты.

Известен адаптивный корректор синала, содержащий аналого-цифровой преобразователь, у которого первы.й выход через блок памяти выборок сигнала соединен с блоком умножения а второй выход упомянутого аналогоцифрового преобразователя подключен к входу блока управления, выходы которого соединены с входами первого и второго сумматоров, а также с входами блоков памяти выборок сигнала, памяти полярностей, сигнала, памти коэффициентов и входом блока памяти знака отклонения амплитуды сигнала от номинального значения, другой вход которого соединен с выходом первого сумматора по модулю два первого блока сумматоров, вход которого через блок памяти полярностей сигнала соединен с входами первого и третьего сумматоров по модул два второго блока сумматоров, а выход блока памяти знака отклонения . амплитуды сигнала от номина.яьиогр

значения подсоединен к входам первого и второго сумматоров по модулю два второго блока сумматоров, кроме того, выход накопителя через блок памяти коэффициентов соединен с входом накопителя и вторым входом блока умножения, выход которого подключен к входам первого и второго сумматоров 1-3

0

Однако известный адаптивный корректор сигнала обладает медленным процессом настройки при передаче данных методами однополосной и двухполосной модуляции.

5

Цель изобретения - ускорение процесса настройки корректора.

Для этого в адаптивный корректор сигнала, содержащий аналого-цифровой преобразователь, у которого первый выход через блок памяти выборок

0 сигнала соединен с блоком умножения, а второй выход упомянутого аналогоцифрового преобразователя подключен к входу блока управления, вькоды

5 которого соединены с входами первого и второго сумматоров, а также с входами блоков памяти выборок сигнала, памяти полярностей сигнала, памяти коэффициентов и входом блока памяти знака отклонения амплитуды сигнала

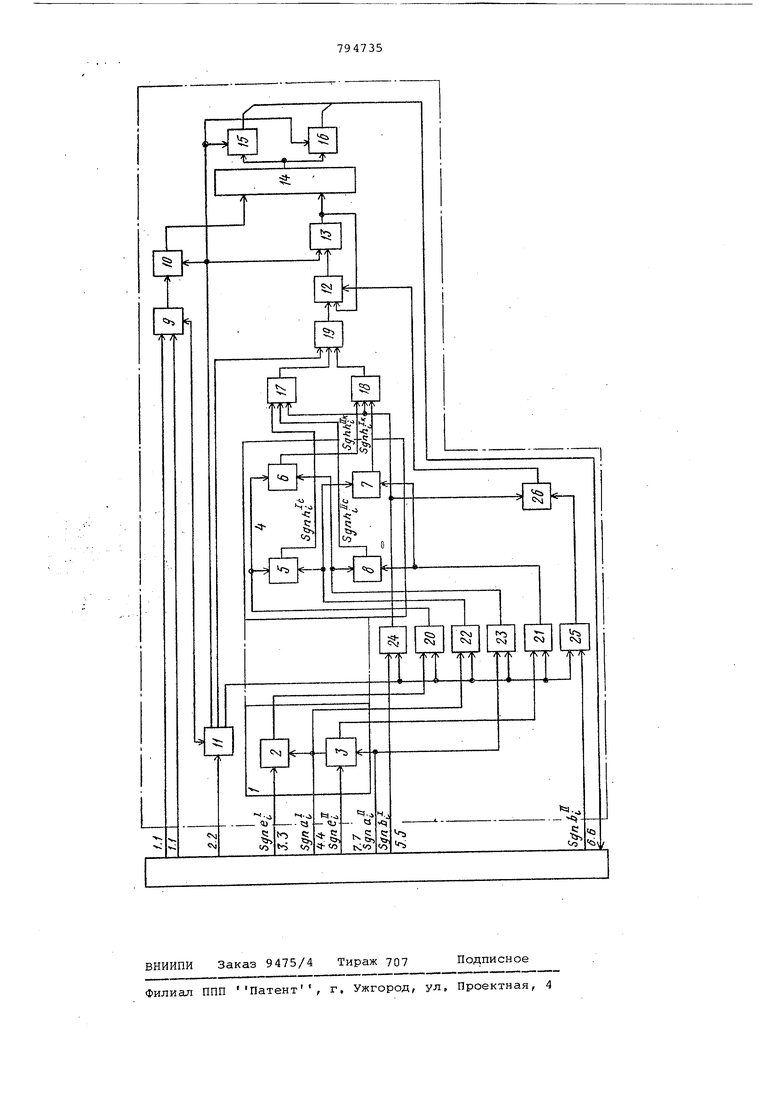

0 ОТ номинального значения, другой вход которого соединен с выходом пе вого сумматора по модулю два первого блока сумматоров, вход которого через блок памяти полярностей сигна ла соединен с входами первого и тре тьего сумматоров по модулю два второго блока сумматоров, а выход блока памяти знака отклонения амплитуд подсоединен к входам первого и втор го сумматоров по модулю два второго блока сумматоров, кроме того, выход накопителя через блок памяти коэффи циентов соединен с входом накопителя и вторым входом блока умножения, выход которого подключен к входам первого и второго сумматоров, введе ны два блока памяти амплитуды сигнала, дополнительный блок памяти полярностей сигнала, дополнительный блок памяти знака отклонения амплитуды от номинального значения, три коммутатора и блок форм1-1рования весового накопления, при этом выход первого блока памяти амплитуды сигнала подключен к входу блока формирования весового накопления и к вхо дам первого и второго коммутаторов , второй и третий входы которых соединены соответственно с выходами первого и четвертого, а также второ го и третьего сумматоров по модулю два второго блока сумматоров, кроме того, второй вход блока формирования весового накопления подключен к выходу второго блока памяти ампли туды сигнала, а выход дополнительного блока памяти полярностей сигнала соединен с входом второго сумматора по модулю два первого блока сумматоров, выход которого через до полнительный Рлок памяти знака отклонения амплитуды сигнала от номинального значения соединен с входами третьего и четвертого сумматоров по модулю два второго блока суммато ров , а выход дополнительного блока мяти полярностей сигнала в свою очередь подключен к входам второго и четвертого сумматоров по модулю два второго блока сумматоров, кроме того, выход блока управления, так же как и выходы первого и второго коммутаторов, подсоединен к входам третьего коммутатора, выход которого соединен со вторым входом накопи теля, третий вход которого подключен к выходу упомяну.того блока формирования весового накопления. На чертеже представлена структурная электрическая схема предлагаемого корректора. Адаптивный корректор сигнала содержит пегвый блок 1 сумматоров, состоящий из первого 2 и второго 3 сумматоров по модулю два соответственно, второй блок 4 сумматоров, сос тоящий из первого 5., второго 6, третьего 7 и четвертого 8 сумматоров по модулю два соответственно, аналого-цифровой преобразователь 9, блок 10 памяти выборок сигнала, блок 11 управления, накопитель 12, блок 13 памяти коэффициентов, блок 14 умно- жения, первый 15 и второй 16 сумматоры соответственно, первый 17, вто.рой 18 и третий 19 коммутаторы соответственно, блок 20 памяти знака отклонения амплитуды сигнала от номинального значения, дополнительный блок 21 памяти знака отклонения амплитуды сигнала от номинального значения, блок 22 памяти полярности сигнала, дополнительный блок 23 памяти полярности сигнала, блоки 24 и 25памяти амплитуды сигнала, блок 26формирования весового накопления. Кроме того, на чертеже показано соединение адаптивного корректора сигнала с приемником 27. Адаптивный корректор сигнала работает следующим образом. Запишем выражения, описывающие алгоритм работы корректора при приеме сигналов данных методами двухкратная относительная фазовая модуляция (ДОФМ) и трехкратная относительная фазовая модуляция (ТОФМ). При этом следует иметь ввиду, что ближайшее собственное мешающее влияние отстоит от регистрируемого элемента сигнала на время , равное вум периодам следования линейных элементов, а сигнал, создающий пере pecTHoe мешающее влияние, отстоит на время, равное одному периоду слеования линейных элементов. Для случая компенсации собственного мешающего влияния S nhf SgnaJ®S9. aSSgne V S nh -SgnajiQS no/eSgne/ (2) Для случая компенсации перекрестного мешающего влияния )nh S9na|© Sgna.©SgneJ ,(J) Sgnh.- -S na - QSgnq.-eSgne.C) де h, - меищющее влияние, Sgnh i Sgnhзнаки проекций собственного мешающего влияния на когерентные колебания 1 и II) знаки проекций перекрестного мешающего влияния на когерентные колебания 1 и IIV -знаки проекций искаженного сигнала ag и проекций сигнала а , создающего межсимвольную помеху на когерентные колебания I и II ; -знаки отклонения амплитуды принятого сигнала а и а относительно нормированного значения.

Алгоритм работы корректора при приеме сигналов с относительной фазовой модуляцией с частично подавленной одной боковой полосой (ОФМ ОБП) и комбинированной четырехпозиционной амплитудой и относительной фазой модуляции с частично подавленной одной боковой полосы частот КЛОФМ и ОБП) можно также описать выражениями (1) - (k) при условии сдвига одного из демодулированных сигналов йа время, равное Т.

В предложенном адаптивном корректоре сигнала использованы блоки памяти с последовательным вводом и выводом информации, что позволяет просто реализовать алгоритм работы корректора в соответствии с выражениями {1 ) (t)

Для этого с соответствующих выходов приемника 27 на входы сумматора 2 по модулю два блока 1 поступашэт сигналы Sgna л Sgne , а на входы сумматора 3 по модулю два блока 1 поступают сигналы Sgna и 5дпе|Сигналы с выходов первого и второго сумматоров (2, 3) по модулю два блока 1 записываются соответственно в блоки 20 и 21. Кроме того, сигналы Sgna- и Sgna в свою очередь записываются в блоки 22 и 23.

Сигнал с выхода блока 20 поступает на первый и второй cyNiMaTopH (5, 6) по модулю два блока 4. Причем на вторые входы этих сумматоров подаются сигналы Sgna и Sgna с Выходов блоков 22 и 23. Сигнал с выхода блока 21 поступает на входы третьего и четвертого сумматоров (7, 8) по модулю два блока 4, на вторые входы KOTODPdx подаются сигналы Sgnaf и Sgna- с выходов блоков 22 и 23. Таким образом, на выходе первого сумматора (5) по модулю два получаем сигнал в соответствии с выражением (1), на выходе второго сумматора (6) по модулю два - сигнал SgnhJ в соответствии с выражением (4) , на выходе третьего сумматора (7) по модулю два - сигнал Sgnh в соответствии с выражением (3) и, наконец на выходе четвертого сумматора (о) по модулю два - сигнал Sgnh в соответствии с выражением (2) .

Сигналы с выходов первого и четвертого сумматоров (5, 8) по модулю два, отражающие направление регулировки в- соответствии с выражениями (1) и (2), с целью компенсации синфазного мешающего воздействия , поступают на входы первого коммутатора (17). На вход второго коммутатора (18) подаются сигналы с выходов второго и третьего сумматоров (6, 7) по модулю два, отображающие направление регулировки в соответствии с выражениями (3 и Ц),

с целью компенсации мешающего воздействия.

Поскольку в режиме ТОФМ целесообразно для формирования сигналов об изменении коэффициента передачи регуляторов отводов использовать демодулированные сигналы с большой амплитудой, что необходимые переключения осуществляются первым и вторым коммутаторами (17, 18) по сигналам, поступающим с выхода первого блока

0 (24) памяти амплитуды сигнала, в котором в двоичном виде записаны значения амплитуды (большая или малая) сигналов af . .

На входы третьего коммутатора

5 (19) поступают сигналы с выходов первого и второго коммутаторов (17, 18) . Управление работой третьего коммутатора (19) осуществляется блоком 11, который подключает на вход

0 накопителя 12 сначала сигналы для поочередной регулировки коэффициентов передачи регуляторов всех отводов по прямым связям (с выхода коммутатора 17) , а затем - сигналы для

5 регулировки всех отводов по перекрестным связям (с выхода коммутатора 18).

Для ускорения процесса настройки корректора амплитуда принимаемых сигналов а, и а- учитывается (в режиме ТОФМ и АОФМ ОБП) при интег0рировании сигналов, отображающих знак направления изменения коэффициента передачи регулятора соответст-. вующего отвода, накопителем 12.

Сигнал о введении того или иного

5 веса при интегрировании формируется в зависимости от используемого метода модуляции блоком 26 по сигналам, поступающим с- выходов блоков 24, 25, т.е. по сигналам SgnbtJ- и

0 Sgnb . Изменение веса при интегрировании эквивалентного изменения емкости накопителя: чем больше вес, тем меньше его емкость. В соответствии с выбранным алгоритмом работы корректора при передаче сиг5налов методами ДОФМ и ОФМ ОБП блок 26 вырабатывает сигнал, соответствующий большому весу, а при передаче сигналов методом АОФМ ОБП блок 26 вырабатывает сигнал, соот0ветствующий малому (увеличение в 2 раза емкости накопителя) или большому весу при интегрировании в зависимости от амплитуды сигналов а: и а

5

Таким образом, в режиме АОФМ ОБП только в том случае, если и на выходе первого и на выходе второго демодуляторов зарегистрированы сигналы с малым значением амплитуды, в блоке 26 формируется сигнал о накоп0лении с малым весом в накопителе 12, т.е. в последний вводится еще один дополнительный разряд. С выхода накопителя 12 п-разрядное цифровое число, соответствующее коэффициенту

5

передачи регулятора отвода, записывается в блок 13.

Сигнал с выхода блока 13 поступает на вход блока 14, на второй вход которого поступают п-разрядные числа, соответствующие выборкам принимаемого сигнала. Процесс формирования выборок осуществляется следующим образом.

Аналоговые сигналы с выходов первого и второго модуляторов приемника 27 поступают на преобразователь в котором производится стробировани ицемодулированных аналоговых сигнало в отсчетные моменты времени, запоминание и хранение амплитуды полученного напряжения выборки, а также преобразование этого напряжения п-разрядное кодовое число. Процесс преобразования осуществляется таким образом, что сначала преобразуется сигнал выборки с выхода первого демдулятора, а затем - сигнал выборки с выхода второго демодулятора приемника 27. В такой же очередности производится запись в блок 10 двух п-разрядных чисел выборок, полученных в результате преобразования. После окончания процесса преобразовния блок 11 вырабатывает сигналы, необходимые для.работы блоков 10, 13, 20, 21, 22, 23, 24, 25, накопителя 12 и сумматоров 15, 16. В каждом такте работы блока 11 из блоков

10и 13 в блок 14 поступают два п-разрядных числа, соответствующие модулям и полярностям кодов выборок

и коэффициента передачи соответствующего отвода корректора. Причем сначала в блок 14 поступает код выборки первого демодулятора, а затем код выборки демодулятора приемника 27 для умножения на один и тот же код коэффициента передачи регулятора. Полученные произведения двух пар п-разрядных чисел записываются по командам, поступающим из блока

11в соответствующие сумматоры 15 и 16.

В следующем такте работы блока 11 из блоков 10 и 13 на входы блока 14 будут поданы п-разрядные числа для следующего отвода корректора.

Результаты умножения алгебраически суммируются в сумматорах 15 и 16 с числами, хранящимися в них от предьщущего такта работы блока 11 для предшествующего отвода. Этот процесс будет продолжаться до тех .пор, пока в сумматорах 15, 16 не будут записаны суммы, полученные в результате суммирования произведений кодов вык борок и коэффициентов передачи для всех отводов корректора. Кодовые числа с выходов сумматоров 15, 16 поступают в решающее устройство приемника 27 для декодирования и формирования сигналов управления адаптивным корректором.

в процессе надстройки корректора в блоке 13 записываются такие числа коэффициентов передачи для всех его отводов по прямым и перекрестным связям, при которых величина максимальной интерференции минимальна.

Из рассмотрения работы корректора следует, что в нем осуществляется последовательная регулировка всех отводов корректора, в частности и центральных отводов. Возможность ре гулировки центральных отводов и, прежде всего, по перекрестным связям, при которых величина межсимвольной интерференции минимальна, позволяетпроизводить компенсацию интегральных

5 сдвигов несущего колебания. Следует иметь в виду, что такая компенсация возможна, только при приеме сигналов, сформированных методами ДОФМ и ТОРФМ.

0 Рассмотрим процесс компенсации этого сдвига на примере. Допустим, что сигналы данных передаются методом ДОФМ. В этом случае вектор сигнала может принимать четыре положения

5 1.1,2.2,3,3,4,4, 5,5,6,6, 7 ..7. Предпо.ложим, что когерентные колебания I и I I сдвинулись по фазе на угол .

Возникшие при этом искажения сигнала не являются следствием межсимвольной интерференции (МСИ), поэтому коэффициенты передачи регуляторов всех отводов, кроме центральных, остаются неизменными. При смещении несущих Околебаний на угол Ч вектор сигнала

с займет новое положение. В этом случае сигнал а на выходе первого демодулятора уменьшится на величину , а сигнал а на выходе второго демодулятора увеличится на величину . , Таким образом, с целью компенсации

0 сдвига несущего колебания, для рассматдолриваемого примера сигнал а

i лсен быть увеличен, а сигнал а

уменьшен за счет добавления с нужным знаком сигналов а и а соответствен ОАлгоритм работы корректора для

регуляторов центральных отводов описывается выражениями (1) - () при i 0.

Регуляторы центральных отводов

по прямым и перекрест - ым связям изменяют в соответствии с (1) - С) коэффициенты передачи с целью компенсации , ,

В результате такой регу гировки

амплитуды сигналов а -и ajj примут номинальное значение, что эквивалентно компенсации сдвига несущих колебаний , ,

Число разрядов п, т , е. точность

преобразования выборок и емкость блоков 10, 13, 20, 21, 22, 23, 24, 25, выбирается исходя из требуемой точности компенсации межсимвольной интерференции и величины исходных искажений в канале связи.

Формула -изобретения

Адаптивный корректор сигнала, содержащий аналого-цифровой преобразователь , у которого первый выход через блок памяти выборок сигнала соединен с блоком умножения, а второй выход упомянутого аналого-цифрового преобразователя подключен к входу блока управления, выходы которого соединены с входами первого и второго сумматоров , а также с входами .блоков памяти выборок сигнала, памяти полярностей сигнала, памяти коэффициентов и входом блока памяти знака отклоне-. НИН амплитуды сигнала от номинального значения, другой вход которого соединен с выходом первого сумматора по модулю два первого блока сумматоров , вход которого через блок памяти полярностей сигнала соединен с входами первого и третьего сумматоров по модулю два второго блока сумматоров, а выход блока памяти знака отклонения амплитуды сигнала от номинсшьного значения подсоединен к входам первого и второго сумматоров по модулю два второго блока сумматоров, кроме того, выход накопителя через блок памяти коэффициентов соединен с входом накопителя и вторым входом блока умножения, выход которого подключен к входам первого и второго сумматоров, отличающийся тем, что, с целью ускорения процесса настройки корректора при передачи данных методами однополюсной и двухполюсной модуляции, введены два блока памяти амплитуды сигнала, дополнительный блок памяти полярностей сигнала, дополнительный блок памяти знака отклонения амплитуды сигнала

от номинального значения, три коммутатора и блок формирова-ния весового накопления, при этом выход первого блока памяти амплитуды сигнала пйдключен- к входу блока формирования весового накопления и к входам первого и второго коммутаторов, второй и ,третий входы которых соединены соответственно с выходами первого и четвертого, а также второго и третьего сумматоров по модулю два второго блоoка сумматоров, кроме того, второй вход блока формирования весового накопления подключен к выходу второго блока памяти амплитуды сигнала, а выход дополнительного блока памяти

5 полярностей сигнала соединен с входом второго сумматора по модулю два первого блока.сумматоров, выход которого через дополнительный блок памяти знака отклонения амплитуды сигна0ла от номинального значения соединен с входами третьего и четвертого сумматоров по модулю два второго блока сумматоров, а выход дополнительного блока памяти полярностей сигнала в свою очередь подключен к входам вто5рого и четвертого сумматоров по модулю два второго блока сумматоров, кроме того, выход блока управления так же как и выходы первого и второго коммутаторов подсоединен к входам

D третьего коммутатора, выход которого соединен со вторым входом накопителя, третий вход которого подключен к упомянутого блока формирования весового накопления.

5

Источники информации, -принятые во внимание при экспертизе

1. Патент США № 3633105, кл. 325-42, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой адаптивный корректор межсимвольных искажений в сигналах передачи данных | 1978 |

|

SU780209A1 |

| Цифровой корректор сигналов | 1979 |

|

SU862366A1 |

| Устройство для адаптивной коррекции межсимвольных искажений | 1981 |

|

SU951725A1 |

| Цифровой адаптивный корректорСигНАлА | 1978 |

|

SU832733A1 |

| Устройство для адаптивной коррекции межсимвольной интерференции | 1981 |

|

SU951724A1 |

| Цифровой приемник многопозиционных сигналов | 1982 |

|

SU1062890A1 |

| Цифровой адаптивный корректор межсимвольной интерференции | 1982 |

|

SU1083374A1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Корректор межсимвольных искажений | 1984 |

|

SU1220130A1 |

| Цифровой адаптивный корректор меж-СиМВОльНыХ иСКАжЕНий B СигНАлАХ дАН-НыХ | 1978 |

|

SU801269A1 |

Авторы

Даты

1981-01-07—Публикация

1978-10-26—Подача