.ходу регистра адреса, пятый вход блока индикации подключен к выходу четвертосо регистра, второй вход которого подключен к FiTopOM) выходу блока сравнения, iuecToA

нход блока сравнения подключен к выходу третьего регистра, второй вход которого подключен к третьему выходу блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее блок памяти, адресный вход которого подключен к первому выходу адресного регистра, информационный вход блока памяти подключен к первому выходу регистра информации и к первому входу блока элементов И, выход блока памяти подключен к первому входу регистра информации, второй вход которого подключен к первому выходу первого блока сумматоров по модулю два, третий вход регистра информации подключен к первому входу первого блока сумматоров по модулю два и к первому выходу первого буферного регистра, выходы которого являются информационными входами устройства,, второй выход первого буферного регистра подключен к второму входу первого блока сумматоров по модулю два, второй выход которого подключен к первому входу регистра ошибок, второй вход регистра ошибок подключен к выходу первого блока свертки, первый и второй входы которого подключены соответственно к второму и третьему выходам регистра адреса, второй выход регистра информации подключен к первому входу блока сравнения, второй вход которого подключен к первому выходу второго блока сумматоров по модулю два, вход второго блока сумматоров по модулю два подключен к третьему выходу регистра tинформации, четвертый вход которого подключен к первому выходу второго буферного регистра, второй выход второго блока сумматоров по модулю два подключен к второму входу блока элементов И, третий вход которого подключен к выходу первого дешифратора, первый выход блока сравнения подключен к входу первого дешифратора, к входу второго дешифратора и к входу блока анализа синдромов, первый выход которого подключен к входу счетчика, сбоев, выход второго дешифратора подключен к четвертому входу блока элементов И, выход которого подключен к входу второго буферного регистра, второй выход второго буферного регистра подключен к входу второго блока свертки и является информационным выходом устройства, второй выI ход блока анализа синдромов подключен к третьему входу регистра ошибок, чет(Л вертый вход которого подключен к выходу второго блока свертки, выход регистра ошибок подключен к входу элемента ИЛИ, выход которого является управляющим выходом устройства, входы первого буферного регистра являются информационными BxojlliMH устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит четыре регистра, два тригге-Nj ра, блок селекции и блок индикации, пер05 вый и второй входы которого подключены СО СП к выходам соответственно первого и второгр триггеров, третий вход блока (шдикаIND ции подключен к выходу первого регистра, первый вход которого подключен к первому входу второго, третьего и четвертого регистров, к первым входам первого и второго триггеров и к первому выходу блока анализа синдромов, вторые входы первого и второго триггеров подключены к соответствующим выходам блока селекции, первый и второй входы которого подключены соответственно к выходу первого дешифратора и к первому выходу регистра информации, четвертый вход блока индикации подключен к выходу второго регистра, вто рой вход которого подк.цочен к третьему вы

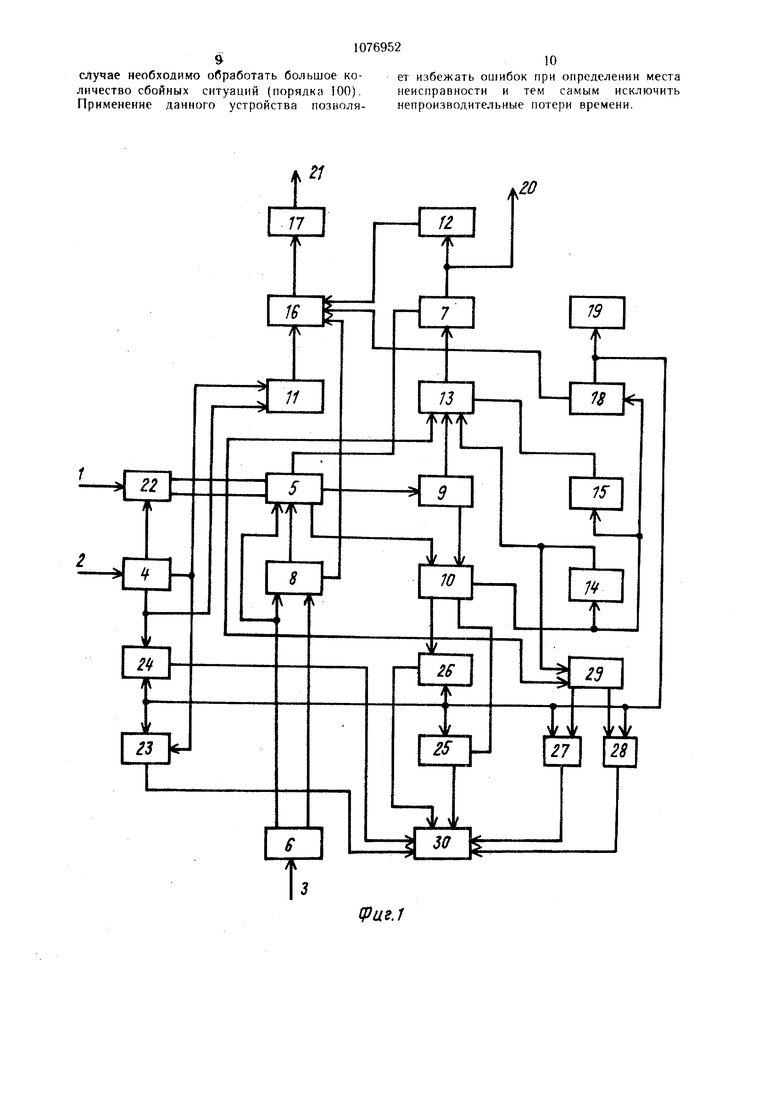

Изобретение относится к построению устройств контроля и диагностики и может быть использовано в специализированных и универсальных вычислительных машинах. Известно устройство для контроля памяти I. Недостатком указанного устройства является то, что оно не обеспечивает возможности локализации неисправностей параллельно с решением задач на ЭВМ. Известно устройство сбора ошибочной информации в памяти 2. Недостатками устройства являются большие затраты оборудования (введено дополнительное запоминаюшее устройство) и потери времени, связанные с фиксацией состояния регистров памяти при любой ошибке. Наиболее близким к предлагаемому является запоминаюшее устройство с самоконтролем, позволяющее выполнить коррекцию информации в случае возникновения сбоев, искажающих один разряд в слове. А в случае сбоев, приводяших к искажению двух и более разрядов, известное устройство позволяет в донолнительном .запоминаюшем устройстве запомнить состояния регистров оперативной памяти для носледуюшего анализа. Недостатком известного устройства является то, что в случае неисправностей, приводящих к искажению информации в одном разряде, не сохраняется состояние регистров оперативной памяти для обеспечения локализации места неисправности. Поэтому локализация таких неисправностей не может быть осуществлена параллельно с решением задачи, что приводит к снижению быстродействия запоминающего устройства и уменьшению коэффициента технического использования ЭВМ. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее блок памяти, адресный вход которого подключен к первому выходу адресного регистра, информационный вход блока памяти подключен к первому выходу регистра информации и к первому входу блока элементов И, выход блока памяти подключен к 11р|-)ному входу регистра информации, второй вход KOTOf)OrO ПОДКЛЮчен к первому выходу первого блока сумматоров по модулю два, третий вход регистра информации подключен к первому входу первого блока сумматоров по модулю два и к первому выходу первого буферного регистра, входы которого являются информационными входами устройства, второй выход первого буферного регистра подключен к второму входу первого блока сумматоров по модулю два, второй выход которого подключен к первому входу регистра ошибок, второй вход регистра ошибок подключен к выходу первого блока свертки, первый и второй входы которого подк тючены соответственно к второму и третьем)- выходам, регистра адреса, второй выход регистра информации подключен к первому входу блока сравнения, второй вход которого подключен к первому выходу второго блока сумматоров по модулю два, вход второго блока сумматоров по модулю два подключен к третьему выходу регистра информации, четвертый вход которого подключен к первому выходу второго буферного регистра, второй выход второго блока сумматоров по модулю два подключен к второму входу блока элементов И, третий вход которого подключен к выходу первого дешифратора, первый выход блока сравнения подключен к входу первого дешифратора, к входу второго дешифратора и к входу блока анализа синдромов, первый выход которого подключен к входу счетчика сбоев, выход второго дешифратора подключен к четвертому входу блока эле.ментов И, выход которого подключен к входу второго буферного регистра, второй выход второго буферного регистра подключен к входу второго блока свертки и является информационным выходом устройства, второй выход блока анализатора синдромов подключен к третьему входу регистра ошибок, четвертый вход которого подключен к выходу второго блока свертки, выход регистра ошибок подключен к входу элемента ИЛИ, выход которого является управляюши.м выходом устройства, входы первого буферного регистра являются инфор.мяционными входами устройства, дополните;1Ь 1О введены четыре регистра, два триггера, блок селекции и блок индикации, первый и второй входы которого подключены к выходим соответственно первого и второго триггеров. третий вход блока индикации подключен к выходу первого регистра, первый вход которого подключен к первому входу второго, третьего и четвертого регистров, к первым входам первого и второго триггеров и к первому выходу блока анализа синдромов, вторые входы первого и второго триггеров подключены к соответствующим выходам блока селекции, первый и второй входы которого подключены соответственно к выходу первого дешифратора и к первому выходу регистра информации, четвертый вход блока индикации подключен к выходу второго регистра, второй вход которого подключен к третьему выходу регистра адреса, пятьш вход блока индикации подкл ючен к выходу четвертого регистра, второй вход которого подключен к второму выходу блока сравнения, шестой вход блока сравнения подключен к выходу третьего регистра, второй вход которого подключен к третьему выходу блока сравнения. На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 и 3 приведены функциональные схемы блока анализа синдрома и блока индикации. Устройство содержит входы 1-3, регистр 4 адреса, регистр 5 информации, буферные регистры 6 и 7, блоки 8 и 9 сумматоров по модулю два, блок 10 сравнения, блоки 11 и 12, сверток по модулю два, блок 13 элементов И, дешифраторы 14 и 15, регистр 16 ошибок, элемент ИЛИ 17, блок 18 анализа синдрома, счетчик 19 сбоев, выходы 20 и 21, блок 22 памяти, регистры 23-26, триггеры 27 и 28, блок 29 селекции и блок 30 индикации. Вход 1 в устройство представляет собой двухпроводную линию, по которой поступают сигналы «Запись, «Чтение, задающие режим работы блока 22 памяти. Вход 2 в устройство представляет собой линию, по которой передается код адреса с контрольными разрядами. Контроль организован побайтно. Вход 3 в устройство представляет собой 72-проводную линию. По входу 3 поступает информация, каждый байт которой сопровождается одним контрольным разрядом Регистр 4 адреса построен на О-триггеpax и служит для запоминания адреса, по которому необходимо выполнить обращение к блоку оперативной памяти. Регистр 5 информации служит для хранения информации при записи в оперативную памяти и после чтения. Помимо 64-х информационных разрядов, он содержит восемь разрядов корректирующего кода. Построен на Д-триггерах. Буферный регистр 6 служит для хранения информации, предназначенной для записи в оперативную память. Помимо ,64-х информационных разрядов содержит восемь контрольных разрядов по одному на каждые восемь разрядов информации. Построен на триггерах. Буферный регистр 7 служит для хранения информации, считанной из оиератив„ой памяти. Содержит 64 информационных разряда, восемь контрольных разрядов и восемь разрядов кода коррекции. Построен на Д-триггерах. Блок 8 сумматоров по модулю два обеспечивает проверку правильности приема 1нформации на первый буферный регистр 6, а также формирует разряды корректирующего кода в соответствии с кодом Хэйминга. На входы блока 8 поступают информационные и контрольные разряды с выходов 1буферного регистра 6. Первый выход блока 8 представляет собой код коррекции, сформированный для всего 64-х разрядного информационного слова. Он подключен к входу регистра 5 информации. Второй выход блока 8 представляет собой выходы восьми сверток, каждая из которых сворачивает восемь информационных разрядов и один соответствующий им контрольный, поступающие с выходов регистра 6. Второй выход поступает на первый вход регистра 16 ошибок. Блок 8 реализован на схемах сложения по модулю два, например, 500 ИЕ 60. Блок 9 сумматоров по модулю два служит для формирования по поступающим на его вход 64-м информационным разрядом кода коррекции по коду Хэмминга (первый выход) и восьми контрольных разрядов для контроля по модулю два (второй выход). Блок 9 реализован, например, на интегральных схемах 500 ИЕ 60. Блок 10 сравнения служит для формиро вания кода синдрома. Представляет собой восемь схем сравнения, на каждую и которых поступает разряд кода коррекции с выхода регистра 5 информации и с выхода блока 9 сумматоров по модулю два. Блок 11 сверток по модулю два служит для контроля правильности приема кода адреса на регистр 4 адреса. Реализован на 500 ИЕ 60. Блок 12 сверток по модулю два служит для контроля правильности приема информации на буферный регистр 7. Реализован на 500 ИЕ 60. Блок 13 элементов И служит для передачи на буферный регистр 7 разрядов информационных, контрольных и кода корреляции в прямом коде или с инверсией. При каждой передаче инвертируются два разряда; информационный и контрольный. соответствующий тому байту, в который входит инвертируемый информацио(шый разряд, или один разряд кода корреляции. Дешифратор 14 предназначен для определения по коду синдрома разряда, неверно считанного из блока 22 памяти на регистр 5 информации. Выход дешифратора

14 поступает на вход блокл 3 элементо И. Дешифратор 15 служит для определения по коду синдрома номера байта, в которол находится неверно считанный информационный разряд. На ден1ифраторов 14 и 15 поступает выход блока 10 сравнения, на котором формируется код синдрома. Регистр 16 ошибок служит для фиксации факта возникновения некорректируемой ошибки. При возникновении такой о нибки для обеспечения возможности анализа причин сбоя работа оперативной памяти, а также устройств, с которыми она же1{а, должна быть приостановлена.

Способы анализа таких ситуаций могут быть самые разнообразные: как ручные, так и автоматические, однако для изобретения это не имеет принциниальпого значения.

Элемент ИЛИ 17 вырабатывает сигна.г приостапова работы оперативной памяти и сог1ряженн1..1х с нею устройств в случае неравенства нулю хотя бы одного разряда регистра 16 ошибок.

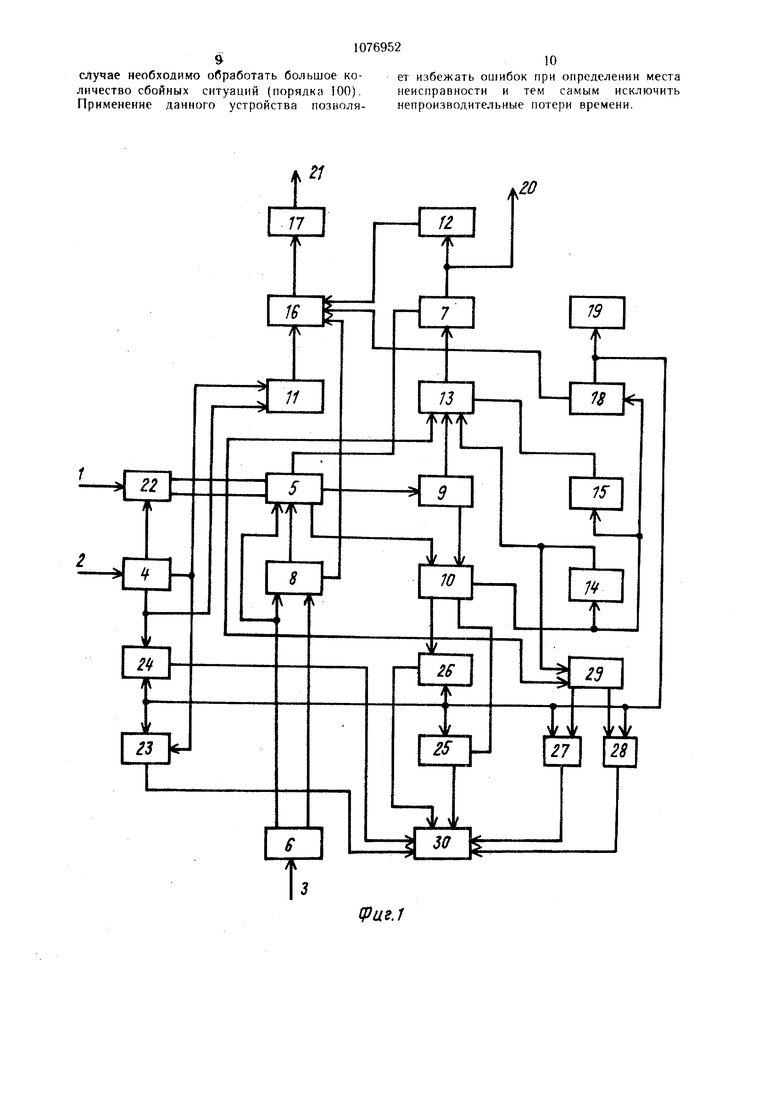

Блок 18 анализа синдрома служит для распознания по коду синдрома коррелирует Mbix ошибок ог1еративной памяти. Функциональная схема блока 18 приведена на фиг. 2 и содержит элеме1гг ИЛИ 18.1, элементы И 18.2, 18.3 и 18.4, элемент ИЛИ 18.5.

Иоявление сигнала на выходе элемента 18.2 говорит о том, что в коде синдрома разряд обшей четности равен единице, а остальные разряды не равны гулю, т. с. имеет место корректируемая ошибка. Иоявление си1нала на выходе элемента 18.3 говорит о том, что в коде синдрома разряд общей четности равен пулю, а остальные разряды не равны нулю, т. е. имеет место двойная ошибка. Появление сигнала на выходе элемента 18.4 говорит о том, что произошла тройная ошибка или неверен разряд общей чет1К)сти. Двойные и тройные ошибки устройством пе корректируются, при этом элементом 18.5 вырабатывается признак некорректируеме)й ошибки.

Счетчик 19 сб(зев служит для псздсчета числа корректируемых ошибок. Oi содержит восемь разрядов, старший разряд подключен пе по счетному, а по установочному входу. Этот разряд сигнализирует о достижении счетчиком 19 максимального значения. В нулевое состояние старший разряд счетчик сбоев 19 устанавливается п)и начальном сбросе. Счетчик 9 выполнен на триггерах, имеет индикаииорп1ые выходы. Первый выход представляет собой 72-х проводнук линию, Fi которой 64 шины используются д.1я передачи информации в восемь контрольны.х разрядов. Второй выход пррдставляе1 собой однопроводную линию, по которой передается сигнал приостанови работ, )a-i ивной амяти и со1 ряженцых устройств н случае возникновения некорректируемой .

Блок 22 оперативной памяти служит для хранения информации и включает в себя, помимо заноминаюнитх мат)иц, схемы деП1ифрап,ии адреса и схемы уси;1ения считываемь х и занис1 1ваемых разрядов информации. Регистр 23 служит для запоминания состояний eди ичныx выходов регистра 4 адреса. Р егпстр 24 служит для запоминания состояний нулевых выходов регистра 4 адреса. Регистр 25 служит для запомипа1П1я состояний прямых выходов схе.м сравнения блока И). Регистр 26 служит для загюмина Н1я состояний и 1версных выходов схем сравнений блока 10. Регистры 23--26 по строе1П:)1 на синхронных Р триггерах. Ин(}10рмация на регистры 23---26 заносится в случае возн.11К -1онения корректируемой ошибки по сигналу с в 11ходн б;юка 18 а 1ализа синдрома. Триггер 27 с.тужит для запоминания единично1о выхода разряда, 11ри 1ятого ч)и счит1) из б.тока оперативной памяти па регистр 5 информации неверно, а триггер 28 хранит состояние улевого выхода указанного разряда. Оба триггера 27 и 28 представ.ляют собой Ктриггеры.

ГЗлок 29 селекции служит для разряда регистра информации, неверно считанного из блока памяти. С выходов блока 29 состояния улево1 о и единичного выходов разряда передаются для запоминания на входы триггеров 27 и 28Выбор разряда осуществляется в соотг етствии с возбужденной выходной шиной детцифратора 14. Блок 29 селекции построен селекторах 500 ЛМ 01.

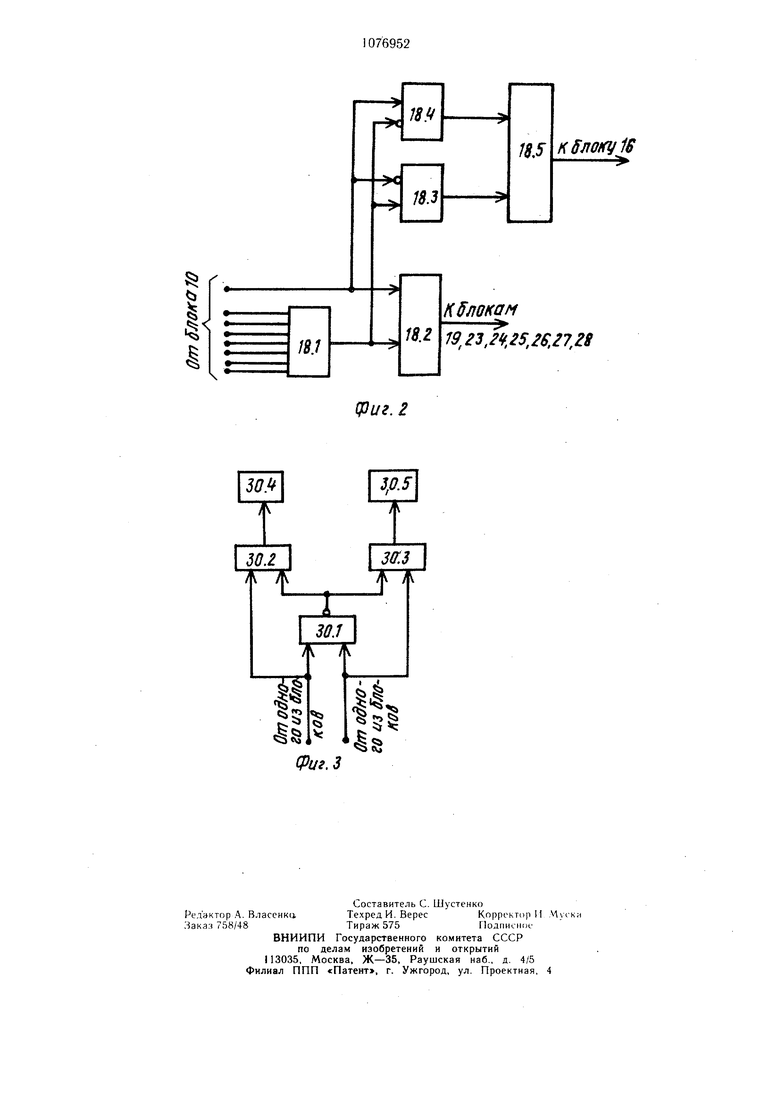

Блок 30 индикации служит для индикации места неисправности. В каждо.м конкретном случае это может быть номер разряда, адрес, поле адреса, указывающее одну из координат. Кроме того, блок 30 укаЗЕзГвает характер неисправности «Иропада 1ие единицы, «Ложпая единица. 1о входам блок 30 индикации связар с регистрами 23-- 26 и триггерами 27 и 28.

Функциональная схема одного разряда блока индикации приведена на фиг. 3. Она содержит элементы И 30.1, 30.2 и 30.3 элементы 30.4 и 30.5 индикации (ламггочка акаливания или светод.чоды). Блок 30 индикации работает следующим образ1)м. Е:сли при возникновении сбоев а ализируе.мый разряд блоков 4, 10 и 5 находится в разных состояниях, то будут устанон,тены в единичное состояние триггеры. нходяп1ие и в блоки 23-27 и в блоки 24, 26 и 28. В этом случае на выходе 30. i имеем 3aiipeшаюший сигнал и ни один индикационный элемент не включается. Нс..ти же при возникновении сбоев анали разряд блоков 4.10.5 iiaxd/uncH в одном каком-либо состоя П1и, roijia то;и,ко один триггер соответству)|цсго ра.зряда блоков 23-28 устанавливается в единичное состояние. При этом включается один из индикационных элементов 30.4, 30.5, и.мею1ЦИХ разную цветовую окраску.

Перед началом работы устройства в период выполнения регламентных работ блоки устройства 19, 23, 24, 25, 26, 27 и 28 по цепи начальной установки нриводятся в исходное нулевое состояние. Чтобы не нерегружать чертежи связями, не имеющими принциниальиого значения, цень начальной установки не показаны.

Устройство имеет два режима работы: «Запись и «Чтение. В режиме «Запись из устройств, сопряженных с оперативной памятью, на регистр 4 адреса поступает адрес, по которому необходимо выполнить запись, на буферный регистр 6 поступает информация с контр()лы11)ми разрядами. Правильность приема адреса контролируется блоком 11 сверток по модулю два, а информации -- блоком 8 сумматоров по модулю два. Рсли информация принята неправильно на указанные регистры, то блоками 11 и 8 вырабатываются сигналы ошибки, которые )стапавливают в единицу соответствующие разряды регистра 16 ошибок и в результате процесс записи прекращается. Ксли ошибки не были обнаружены, блоком 8 сумматоров но модулю два формируется код коррекции и информация совместно с кодом коррекции принимается на регистр 5 пиформа 1ии. При поступлении по- первому входу в устройство сигнала «Запись ин(()ормация совместно с кодом коррекции записьп ается в блок 22 памяти.

В режиме «Чтение из устройств, сопряженных с оперативной памятью, на регистр 4 адреса заносится адрес, по которому необходимо В п1олнить обращение. Затем по первому входу I в устройство в блок 22 памяти поступает сигпал «Чтение. В результате на регистр 5 поступает информация с кодо.м коррекции. Информационные разряды с третьего выхода регистра информации поступают на вход блока 9 сумматоров по модулю два. Блоком 9 в соответствии с информацией, поступившей на его вход, по первому выходу формируется код коррекции, а по второму выходу коптрольные разряды.

Код коррекции с второго выхода регистра информации (считанный) и код коррекции с первого выхода второго блока 9 сумматоров (сформированный) сравниваются в блоке 10 сравнения. В результате на выходе блока сравнения образуется код . поступаюп1ий в блок 18 анализа синдрома. Если блоком 18 обнаружена некорректируемая ошибка, на его выходе формируется сигнал, устанавливающий соответствующий разряд регистра 16 ошибок в единицу, что приостанавливает работу оперативной памяти и сопряженных стройств. Если блоком 18 анализа синобнаруживается корректируемая

арома ошибка. то состояние счетчика 19 сбоев увеличивается на единицу. Дешифратор 15 возбуждает соответствующий коду синдрома вход блока 13 вентилей и через него информация передается на буферный регистр 7 (информационные разрядын раз-ряды кода коррекции). Дешифратор 15 возбуждает соответствуюп1.пй коду синдрома вход блока 13 вентилей, через который передаются контрольные разряды на буфер1Цз1Й регистр 7. Одновременно состояние разрядов регистра 4 адреса, выходов блока 10 сравнения, искаженног-о разряда регистра 5 информации копируются на регистры и триггеры блоков 23 - 28. Затем откорректированная информация поступает на-бу- , ферпый регистр 7, провер;гется блоком 12 сверток по .модулю дпа и передается в устройства, сопряженн11 е с оперативной памятью. iVpo.Me того, с 6y(JiepHoro регистра 7 информациоппые раз|)ялы и разряды кода коррекцпи передаются на вход регистра )ормацип для регенерации.

Учшывая, что устройство работает непрерырлю, н Н|)оцессе юализации задкам без затраг по.лезного мапиппюго времени удается ofiiiaOoTaTb значите.пьное количество сбоев. П сплу указаппых особепностей п6CTpoefiHR устройства блоком индикации инфицируются состояние полей регистров, имеи)П1пх обп1ий характер для всех сбоев. Например, если сбой возникает по одному какому-либо разряд}, то в иоле блока индикации, с блоком сравнения, после обработки всех сбоев будет индицироваться номер сбс)йного разряда. Если HcnciipaniiocTii связппа с смпибкой схем передачи адреса или схем деши(|1рацип адреса, то, 11)11 условии достижения счетчиком 19 сбоев максим ма, в б;1ок(. индикации будет индицироваться и.чи 01 крстньп1 адрес, или одна координат адреса.

Предлагае.мое устройство позволит обеспечит1 локализацию неисправностей оперативной памяти, имеющих перемещающийся характер и приподяпшх к искажению информации в одном разряде,

параллел по с рсп ением задач па ЭВМ, без затрат времени и без существенного увеличения оборудова1П1я.

Изобретеьше стало возможным благодаря возможности обработки сбойной информации, одновременно с ее фиксацией на дополшггельных регпст)ах. без накопления в буферных зацомпнак)П1их устройствах. Наиболее целесообразно использование данного устройства для поиска неисправностей оперативпой памяти типа 2.5Д. В

2,5Д, одни памяти, построенной по схеме и те же обмотки испо.и.зуютс; и как адресные, и как разрядн111е. lIovTo iy в ряде случаев неисправность к счсм.чх деип)фрации адреса воспринимаете-; K;IK ачрядиая. Для обеспечения прави.чыичо диагноза о этом

случае необходимо обработать большое количество сбойных ситуаций (порядка 00). Применение данного устройства позволяет избежать ошибок при определении места неисправности и тем самым исключить непроизводительные потери времени.

(рцг.1

Фиг.З

p.5

| I | |||

| БОРОНА - КОРЧЕВАЛЬНАЯ МАШИНА | 1923 |

|

SU1030A1 |

| Под ред | |||

| А | |||

| Н | |||

| Ларинова | |||

| М | |||

| «Статистика, 1977, с | |||

| Приспособление к тростильной машине для прекращения намотки шпули | 1923 |

|

SU202A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Солесос | 1922 |

|

SU29A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Крутильный аппарат | 1922 |

|

SU233A1 |

Авторы

Даты

1984-02-28—Публикация

1981-11-23—Подача