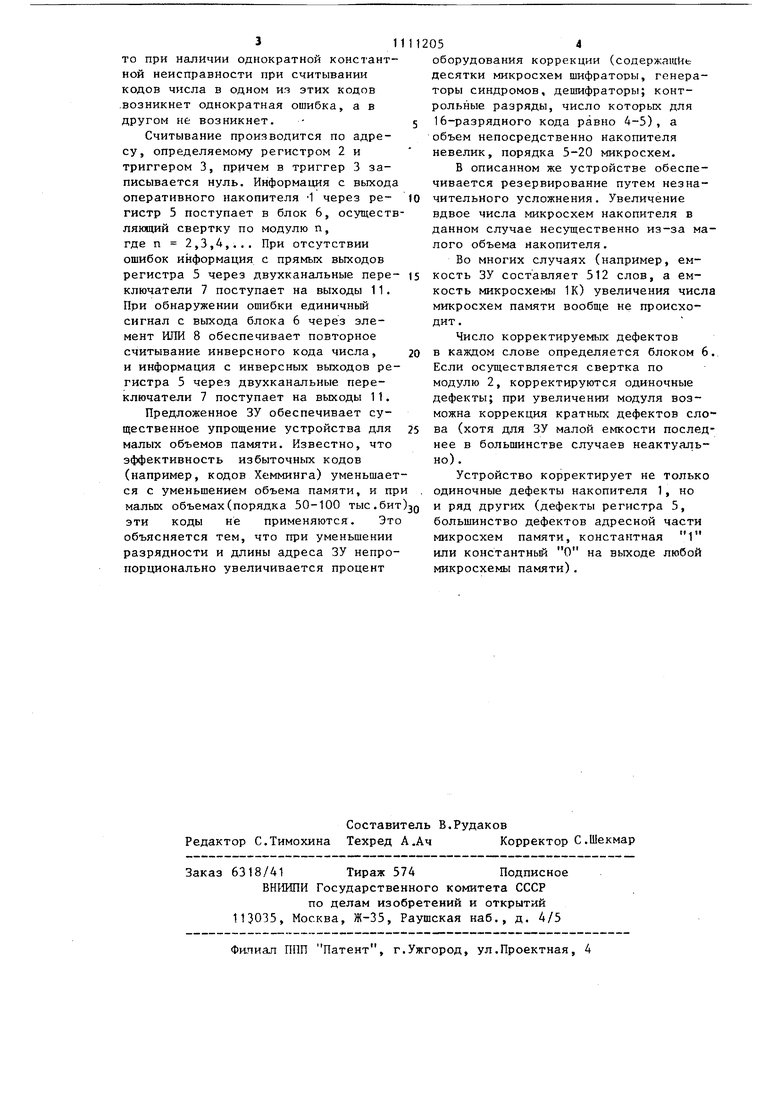

Изобретение относится к вычислительной технике, конкретно к запоми нающим устройствам с произвольной в боркой. Известно запоминающее устройство срдержащее накопитель, входной регистр адреса, узел коррекции одиноч ных ошибок l . Недостатком этого устройства являются большие аппаратурные затра ты. Наиболее близким к дaннo ry изобре уению является запоминающее устройст во с использованием избыточного кода (например, кода Хемминга), содержащее оперативный накопитель, соединенный через регистр адреса с адресными шипами, причем выходы накопителя соединены со входами регистра информации, прямые и инверс ные выходы которого через группу двухканальных переключателей соединены с вьгходными числовыми шинами 2J . Недостатком этого запоминающего устройства является его сложность. Особенно существенно это для запоминакш(его устройства (ЗУ) небольшой емкости (до 50-100 тыс. бит), когда суг-тарный объем оборудования коррекции (схема кодирования, избыточные разряды, генератор синдромов, схема декодирования) близок или даже превы шает объем оборудования собственно З Цель изобретения - упрощение уст ройства . Поставленная цель достигается тем что в запоминающее устройство с кор рекцией ошибок, содержащее оператив ньй накопитель, одни из входов которого подключены к выходам регистра адреса, входы которого являются одни ми из адресных входов устройства, а выходы оперативного накопителя соединены со входами регистра числа, прямые и инверсные выходы которого подключены к одним из входов двухканальных переключателей, выходы которых являются информационными выходами устройства, введены двухразрядные сумматоры по модулю два, триггер элемент ИЛИ и блок свертки по модулю входы KOTopoio подключены к прямым выходам регистра числа, а выход соед нен с другими входами двухканальных переключателей и первым входом элемента ИЛИ, причем первые входы двухразрядных сумматоров по модулю два являются информационными входами устройства, вторые входы двухразрядных сучматоров по модулю два и элемента ЛПИ подключены к выходу триггера, вход которого является другим адреснэ1м входом устройства, выходы двухразрядных сумматоров по модулю два и элемента ИЛИ соединены с другими входами оперативного накопителя. На чертеже приведена функциональная схема запоминающего устройства. Запоминающее устройство содержит оперативный накопитель 1, регистр 2 адреса, триггер 3, сумматоры А по модулю два, регистр 5 числа, блок 6 свертки по модулю, двухканальные переключатели 7, элемент ИЛИ 8. Устройство имеет информационные 9 и адрес- . ные 10 входы и информационные выходы 11. Запоминающее устройство работает следующим образом. Запись информации производится дважды. При первой записи на вход триггера 3 поступает нуль,при этом информация на выходе сумматоров 4 по модулю два соответствует информации на входах 9 числовых, и в оперативный накопитель 1 записывается прямой код числа по адресу, определяемому регистром 2 и триггером 3. При второй записи на вход триггера 3 поступает единица, которая через элемент ИЛИ 8 поступает на адресньй вход накопителя 1, при этом информация на выходе сумматоров 4 по модулю два инвертируется, и в оперативный накопитель 1 записывается инверсньй код числа по адресу, определяемому регистром 2 и триггером 3. Оссбенностью оперативного накопителя 1 является то, что возникающие в нем отказы являются констант 1ыми, вследствие чего считываемая по адресу А| из j-го отказавшего разряда инфop aция oi.;; всегда равна либо логическому нулю, либо логической . едини11,е. В результате, если записываемая в j-и разряд по адресу Aj инфоркация Sij совпадает с ol-ij , то при считывании кода числа по этому алресу в нем не возникает однократной ошибки. Если ty,j , то в считанном коде числа возникает однократная ошибка. Так как в операTHBHbiii накопитель 1 информация записьшае-ся и в прямом и в инверсном кодах в разные ячейки накопителя.

то при наличии однократной константной неисправности при считывании кодов числа в одном из этих кодов .возникнет однократная ошибка, а в другом не возникнет. Считывание производится по адресу, определяемому регистром 2 и триггером 3, причем в триггер 3 записывается нуль. Информация с выхода оперативного накопителя 1 через регистр 5 поступает в блок 6, осуществляющий свертку по модулю п, где п 2,3,4,... При отсутствии ошибок информация с прямых выходов регистра 5 через двухканальные переключатели 7 поступает на выходы 11. При обнаружении ошибки единичный сигнал с выхода блока 6 через элемент ИЛИ 8 обеспечивает повторное считывание инверсного кода числа, и информация с инверсных выходов регистра 5 через двухканальные переключатели 7 поступает на выходы 11.

Предложенное ЗУ обеспечивает существенное упрощение устройства для малых объемов памяти. Известно, что эффективность избыточных кодов (например, кодов Хемминга) уменьшается с уменьшением объема памяти, и пр малых объемах(порядка 50-100 тыс.бит эти коды не применяются. Это объясняется тем, что при уменьшении разрядности и длины адреса ЗУ непропорционально увеличивается процент

оборудования коррекции (содержащие десятки микросхем шифраторы, генераторы синдромов, дешифраторы; контрольные разряды, число которых для 16-разрядного кода равно 4-5), а объем непосредственно накопителя невелик, порядка 5-20 микросхем.

В описанном же устройстве обеспечивается резервирование путем незначительного усложнения. Увеличение вдвое числа микросхем накопителя в данном случае несущественно из-за малого объема накопителя.

Во многих случаях (например, емкость ЗУ составляет 512 слов, а емкость микросхемы 1К) увеличения числ микросхем памяти вообще не происходит.

Число корректируемых дефектов в каждом слове определяется блоком 6 Если осуществляется свертка по модулю 2, корректируются одиночные дефекты; при увеличении модуля возможна коррекция кратных дефектов слова (хотя для ЗУ малой емкости последнее в большинстве случаев неактуально) .

Устройство корректирует не только одиночные дефекты накопителя 1, но и ряд других (дефекты регистра 5, большинство дефектов адресной части микросхем памяти, константная 1 или константный О на выходе любой микросхемы памяти).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1991 |

|

SU1837364A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Запоминающее устройство | 1978 |

|

SU696871A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК И КОРРЕКЦИЕЙ ОДИНОЧНОЙ ОШИБКИ | 1993 |

|

RU2062512C1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК, содержащее оперативный накопитель, одни из входов которого подключены к выходам регистра адреса, входы которого являются одними из адресных входов устройст ва, а выходы оперативного накопителя соединены с входами регистра числа, прямые и инверсные выходы которого подключены к одним из входов двухканальных переключателей, выходы которых являются информационными выходами устройства, отличающееся тем, что, сцелью упрощения устройства, в него введены двухразрядные сумматоры по модулю два, триггер, элемент ИЛИ и блок свертки по модулю, входы которого подключены к прямым выходам регистра числа, а выход соединен с другими входами двухканальных переключателей и первым входом элемента ИЛИ, причем первые входы двухразрядных сумматоров по модулю два являются информационными входами устройства, вторые входы двухразрядных сумматоров по модулю два и элемента ИЛИ подключены КЛ к выходу триггера, вход которого является другим адресным входом устройства, выходы двухразрядных сумматоров по модулю два и элемента ИЛИ соедйне- о ны с другими входами оперативного накопителя. //

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1978 |

|

SU769624A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство | 1979 |

|

SU873276A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-08-30—Публикация

1983-06-27—Подача