(54) ПРОЦЕССОР ВВОДА-ВЫВОДА С КОРРЕКЦИЕЙ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Процессор ввода-вывода | 1979 |

|

SU798782A1 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Селекторный канал | 1973 |

|

SU517019A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для создания одно- и мультипроцес.сорных вычислительных систем.

Известны процессоры, в качестве которых могут служить, машины Звм/370 (модели 125, 135, 145 и др.) , ЕС ЭВМ (Модели ЕС-1035, ЕС-1045 и др.) 1J

Недостатком данных ЭВМ является то, что в них корректируются лишь однократные ошибки, а двух- и трех- . кратные ошибки вызывают отказ в работе вычислительной системы.

Наиболее близким к изобретению является процессор ввода-вывода,содержащи{1 блок управления командами, операционный блок, блок управления оперативной памятью, блок микррпрограммного управления и набор каналов ввода-вывода, входы и первые выходы которых подключены к выходным и входным информационным шинам, к которым подключены соответственно выход и первый вход операционного блока, первые входы и выходы блока микропрограммного управления, блока управления оперативной памятью и блока управления командами, вход-выход ко- торого подключен к шинам центрального процессора, а второй выход - к

запросным шинам, к которым подключены вторые выходы каналов ввода-вывода и второй вход блока микропрограммного управления, второй выход которого подключен к .управляющим шинам, к которым также подключен второй вход операционного блока, а вход-выход и второй выход блока управления оперативной памятью подключены к шинам

10 оперативной памяти U2l .

Недостатком известного процессора является отсутствие коррекции двухи трехкратных ошибок. Следовательно, надежность процессора снижается из-за 15 отсутствия коррекции этих ошибок.

Цель изобретения - повышение надежности процессора.

Поставленная цель достигается тем, что в процессор, содержащий 20 блок формирования, блок управления оперативной памятью, операционный блок, блок микропрограммного управления и каналы ввода-вывода, при этом вход-выход блока управления

25 подключен к шине центрального процессора, запросный выход блока управления подключен к первым выходам каналов ввода-вывода и через шину запроса соединен с вхоДом запроса

30 блока микропрограммного управления.

выход приостанова микропрограммы которого подключен к входу каждого канала ввода-вывода и через выходную информационную шину с адресным входо блока управления, с первым входом операционного блока и адресным входом блока управления оперативной памятью, первый вход-выход которого соединен с шиной оперативной памяти адресный выход блока управления оперативной памятью подключен к шине оперативной памяти, первый выход блка управления оперативной памятью через входную информационную шину подключен к адресному выходу блока управления, к первому входу операционного блока, к выходу приостанова микропрограммы блока микропрограммного управления и второму выходу каждого канала ввода-вывода, управляющий выход микрокоманд блока микропрограммного управления подключен к второму входу операционного блока введены блок анализа числа ошибок, блок фиксации ошибок и регистр данных, при этом вход выход регистра данных подключен к шине оперативной памяти, вход-выход блока фиксации ошибок соединен с шиной оперативной памяти, первый выход блока фиксации ошибок через шину запроса подключен к первому входу регисра данных, первый выход которого через выходную информационную шину подключен к первому входу блока фиксации ошибок, второ выход которого соединен .с вторым выходом регистра данных и через входную информационную шину подключена к первому входу операционного блока, второй вход регистра данных соединен с первым, выходом операционного блока, адресньом входом блока управления оперативной памятью и через выходную информационную шину к первому входу блока анализа числа ошибок, второй вход которого через управляющую шину подключен к управт дяющему выходу блока микропрограммного управления и второму входу блока фиксации ошибок, третцй вход которого подключен к информационном выходу блока управления оперативной памятью-, третий выход блока фиксаци ошибок через шину запроса соединен с запросным входом блока микропрограммного управления, четвертый выхо блока фиксации ошибок подключен к первому и второму адресному входам блока микропрограммного управления, третий адресный вход которого подключен к выходу блока анализа.

Кроме того, блок фиксации ошибок содержит элементы ИЛИ, триггер з-апрта, триггер запроса, дешифратор, формирователь синдрома, формирователь контрольных разрядов и регистр при этом вход формирователя контрольных разрядов является первым

входом блока, выход формирователя контрольных разрядов соединен с входом регистра, вход-выход которого является входом-выходом блока, выход регистра подключен к первому входу формирователя синдрома, второй вход которого является третьим входом блока, выход формирователя синдрома подключен к входу дешифратора,группа выходов KOloporo, кроме первого, подключена к соответствующим входам каждого элемента ИЛИ, при этом первая группа выходов дешифратора является вторым выходом блока, первый выход дешифратора и группа выходов каждого элемента ИЛИ, кроме второго, являются четвертым выходом блока, третьим выходом которого является . выход триггера запроса, первый вход которого подключен к выходу второго элемента ИЛИ,первый вход которого подключен к выходу третьего элемента ИЛИ, а второй вход - к выходу четвертого элемента ИЛИ, единичный вход триггера запроса, триггера запрета И объединенные сбросовые входы триггеров являются, группой входов блока, nepBEDJM выходом которого является нулевой выход триггера запрета,выход триггера запроса является третьим выходом блока.

Кроме того, блок анализа содержит триггеры, элементы И и НЕ, пороговые элементы и сумматор по модулю два, при этом вход сумматора по модулю два объединен с входами пороговых элементов и является первым входом блока, выход сумматора по модулю два подключен к входу первого элемента НЕ и первому входу первого элемента И, выход каждого элемента И подключен к управляющему входу соответствующего триггера, кроме последнего, синхронизирующие входы которых объединены и являются вторым входом блока, выходы триггеров являются вы.ходом блока, выход первого порогового элемента подключен к входу второго элемента НЕ и первому входу второго элемента И, второй вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с управляющим входом последнего триггера и выходом второго порогового элемента, выход второго элемента НЕ подключен к первому входу третьего элемента И, второй вход которого объединен с вторым входом первого элемента И и подключены к выходу второго элемента НЕ.

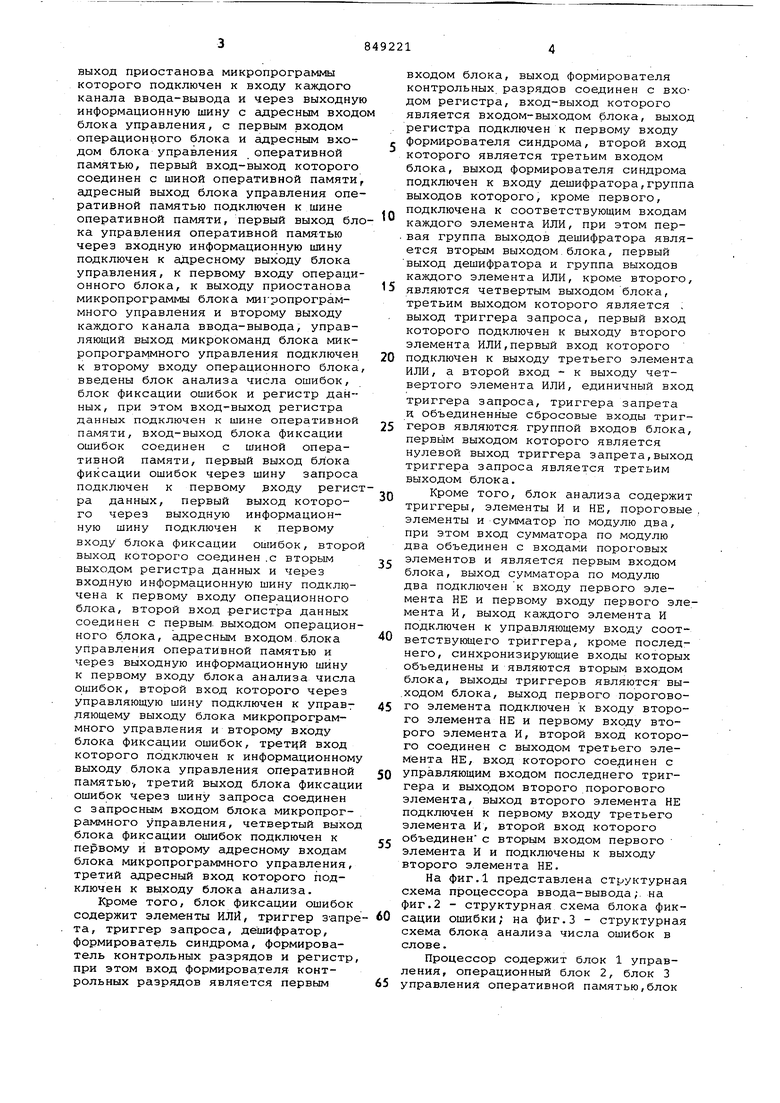

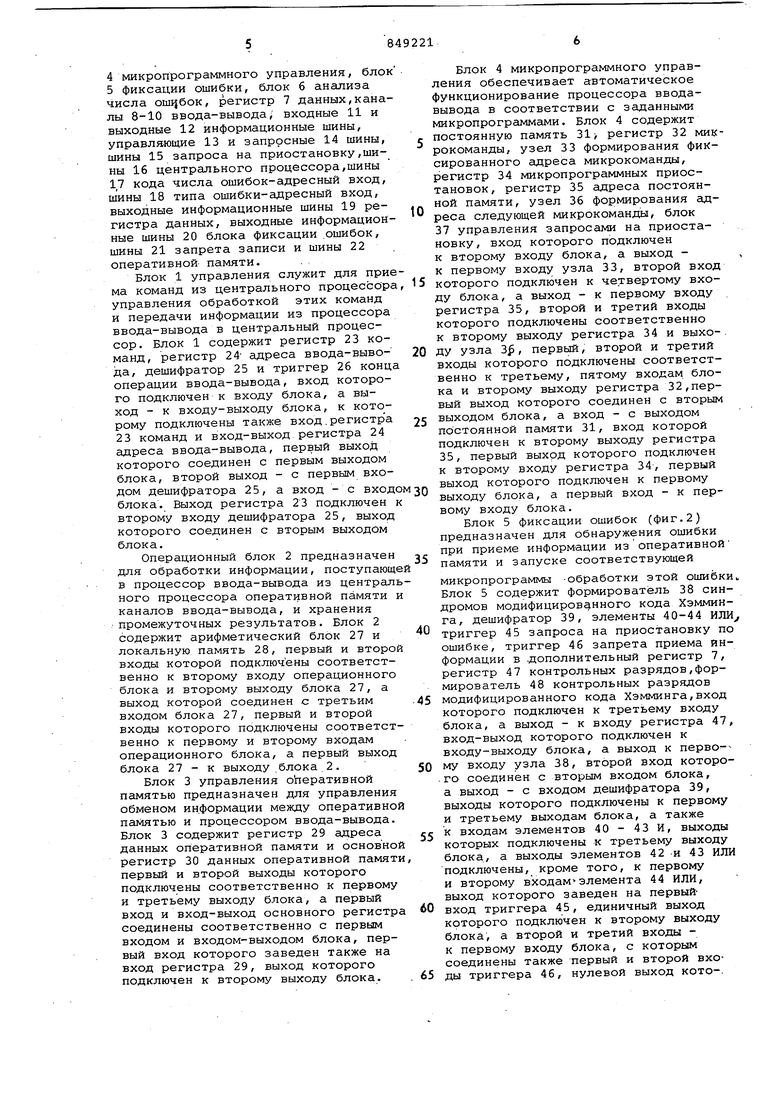

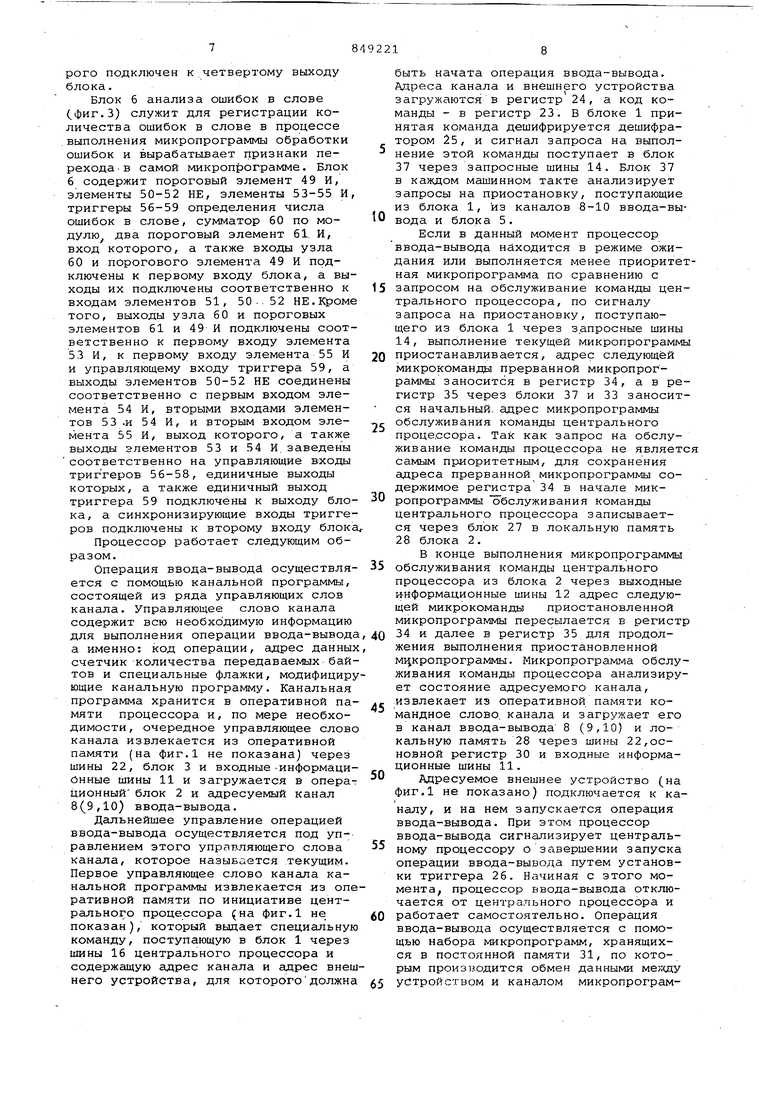

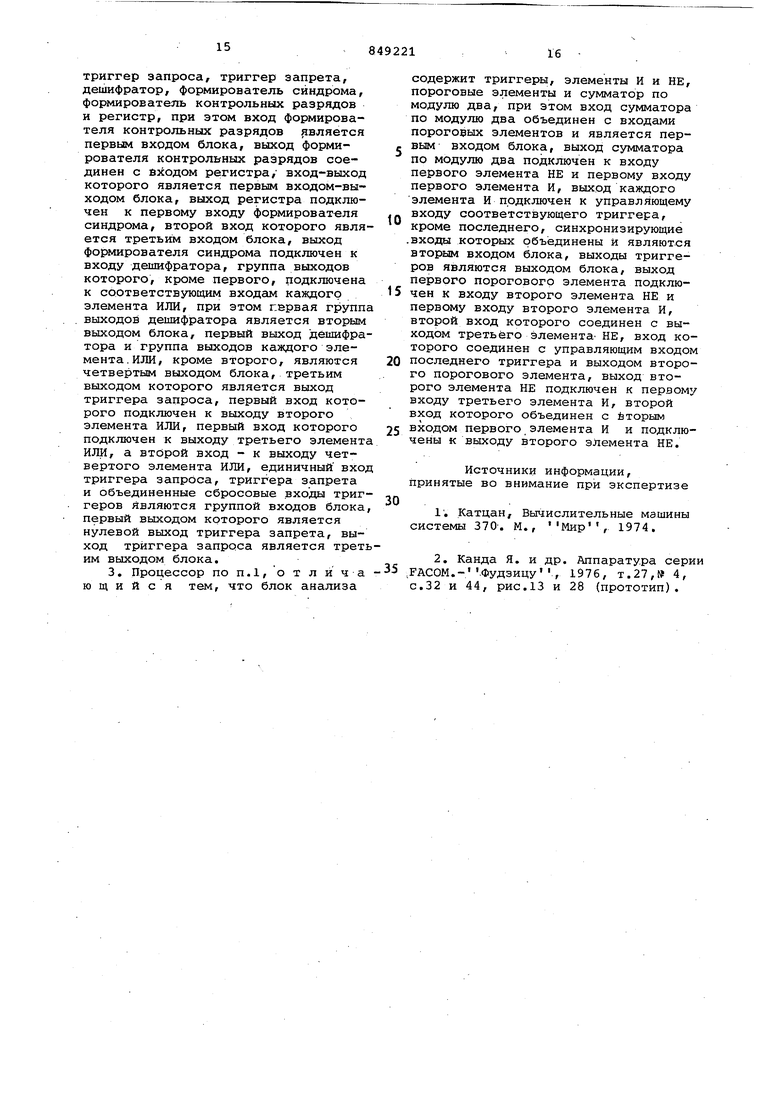

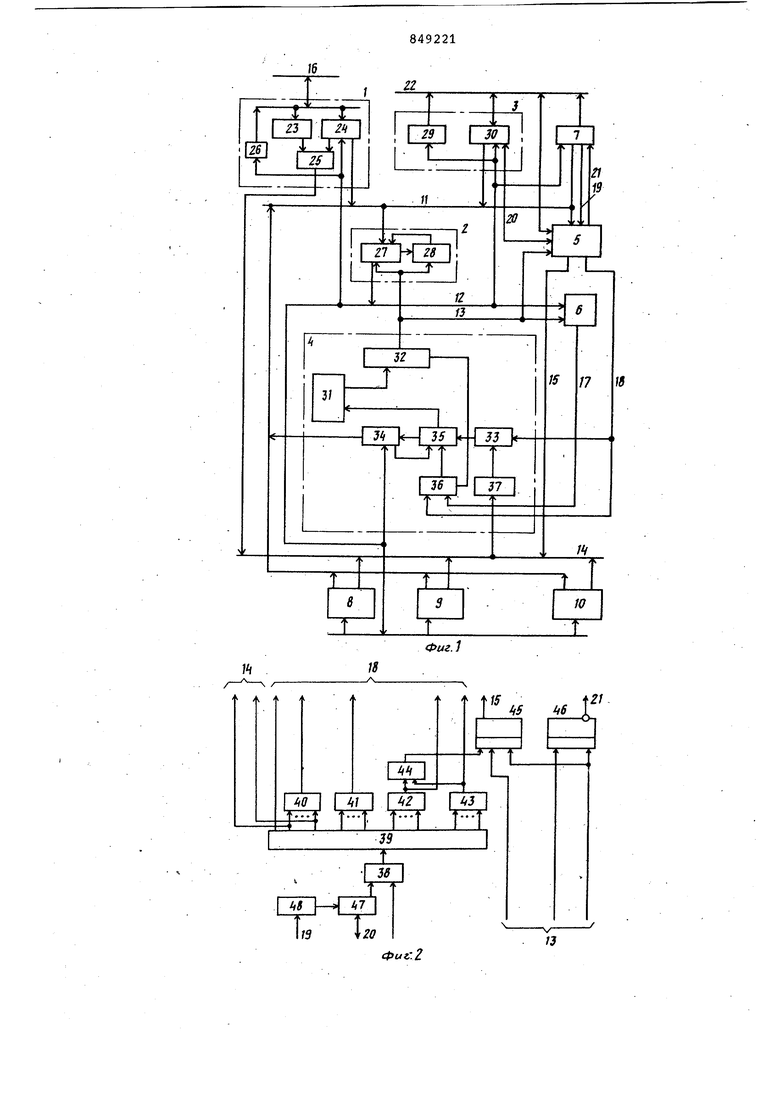

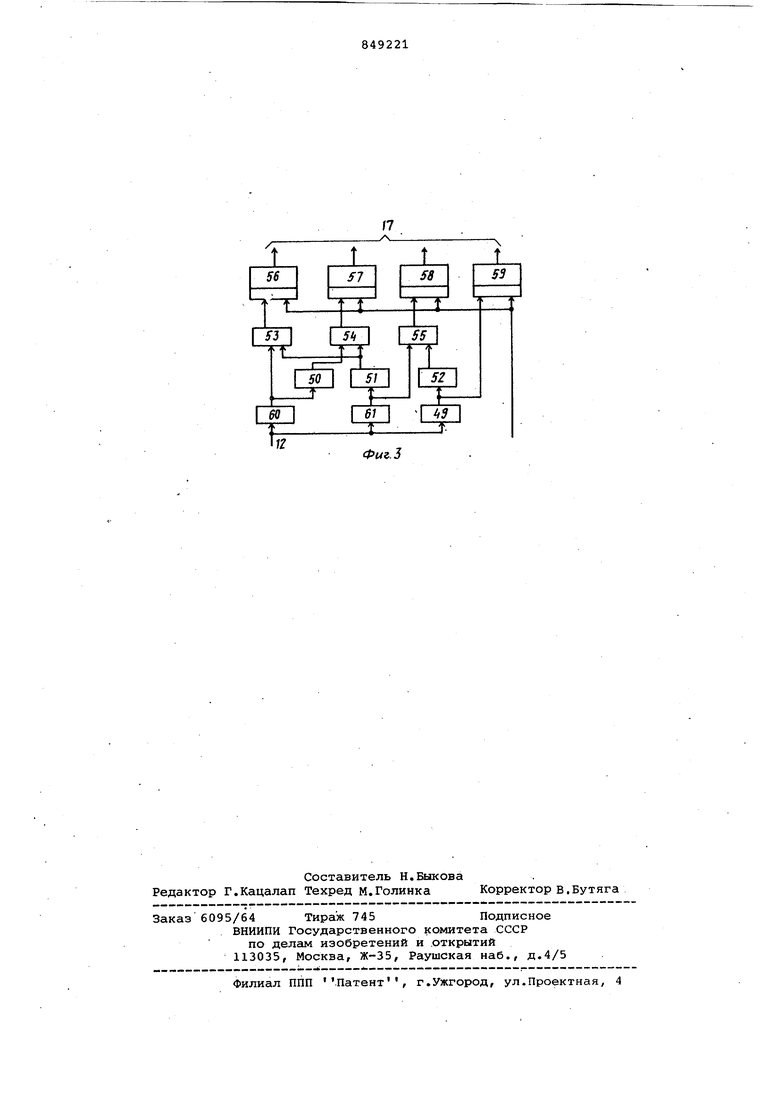

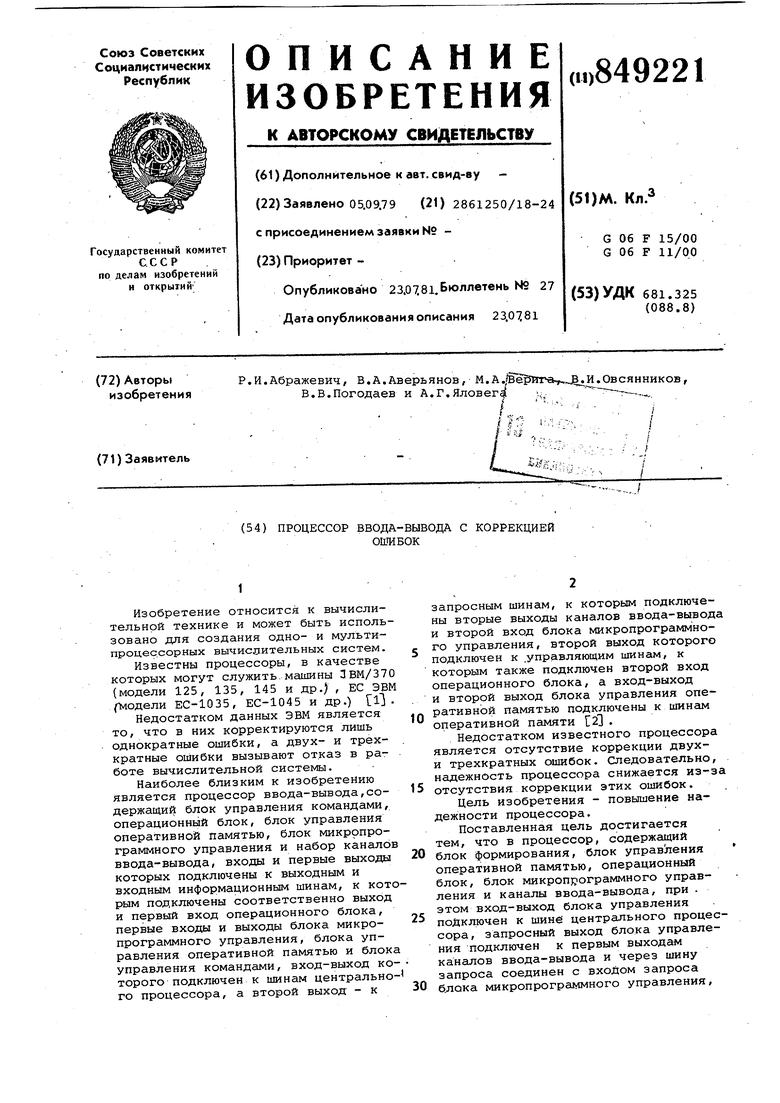

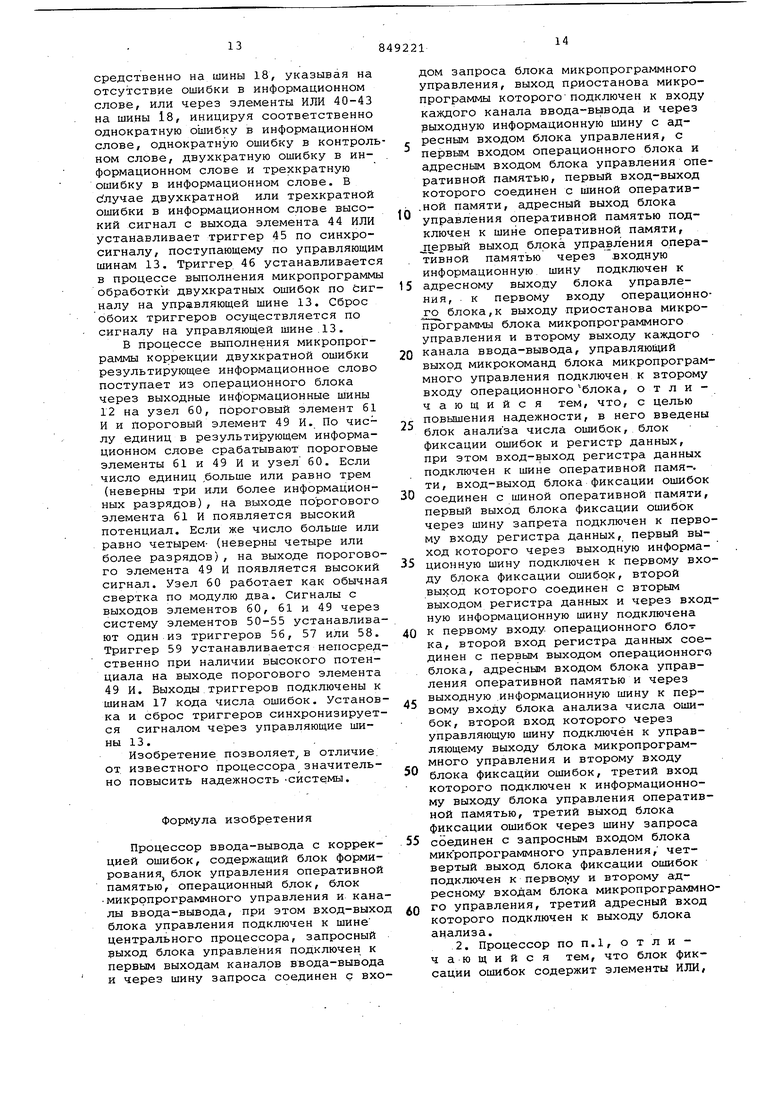

На фиг.1 представлена структурная схема процессора ввода-вывода; на фиг.2 - структурная схема блока фиксации ошибки; на фиг.З - структурная схема блока анализа числа ошибок в слове.

Процессор содержит блок 1 управления, операционный блок 2, блок 3 управления оперативной памятью,блок

4микропрограммного управления, блок

5фиксации ошибки, блок 6 анализа числа ошибок, регистр 7 данных,каналы 8-10 ввода-вывода; входные 11 и выходные 12 информационные шины, управляющие 13 и запросные 14 шины, шины 15 запроса на приостановку,шины 16 центрального процессора,шины

17 кода числа ошибок-адресный вход, шины 18 типа ошибки-адресный вход, выходные информационные шины 19 регистра данных, выходные информационные шины 20 блока фиксации ,ошибок, шины 21 запрета записи и шины 22 оперативной памяти.

Блок 1 управления служит для приема команд из центрального процессора управления обработкой этих команд и передачи информации из процессора ввода-вывода в центральный процессор. Блок 1 содержит регистр 23 команд, регистр 24- адреса ввода-вывода, дешифратор 25 и триггер 26 конца операции ввода-вывода, вход которого подключен к входу блока, а выход - к входу-выходу блока, к кото рому подключены также вход .регистра 23 команд и вход-выход регистра 24 адреса ввода-вывода, первый выход которого соединен с первым выходом блока, второй выход - с первым входом дешифратора 25, а вход - с входо блока. Выход регистра 23 подключен к второму входу дешифратора 25, выход которого соединен с вторым выходом блока.

Операционный блок 2 предназначен для обработки информации, поступающе в процессор ввода-вывода из центрального процессора оперативной памяти и каналов ввода-вывода, и хранения промежуточных результатов. Блок 2 содержит арифметический блок 27 и локальную память 28, первый и второй входы которой подключены соответственно к второму входу операционного блока и второму выходу блока 27, а выход которой соединен с третьим входом блока 27, первый и второй входы которого подключены соответственно к первому и второму входам операционного блока, а первый выход блока 27 - к выходу блока 2.

Блок 3 управления оперативной памятью предназначен для управления обменом информации между оперативной памятью и процессором ввода-вывода. Блок 3 содержит регистр 29 адреса данных оперативной памяти и основной регистр 30 данных оперативной памяти первый и второй выходы которого подключены соответственно к первому и третьему выходу блока, а первый вход и вход-выход основного регистра соединены соответственно с первым входом и входом-выходом блока, первый вход которого заведен также на вход регистра 29, выход которого подключен к второму выходу блока.

Блок 4 микропрограммного управления обеспечивает автоматическое функционирование процессора вводавывода в соответствии с заданными микропрограммами. Блок 4 содержит постоянную память 31 регистр 32 микрокоманды, узел 33 формирования фиксированного адреса микрокоманды, регистр 34 микропрограммных приостановок, регистр 35 адреса постоянной памяти, узел 36 формирования адреса следующей микрокоманды, блок 37 управления запросами на приостановку , вход которого подключен к второму входу блока, а выход к первому входу узла 33, второй вход которого подключен к четвертому входу блока, а выход - к первому входу регистра 35, второй и третий входы которого подключены соответственно к второму выходу регистра 34 и выходу узла 3, первый, второй и третий входы которого подключены соответственно к третьему, пятому входам блока и второму выходу регистра 32,первый выход которого соединен с вторым выходом блока, а вход - с выходом постоянной памяти 31, вход которой подключен к второму выходу регистра 35, первый выход которого подключен к второму входу регистра 34, первый выход которого подключен к первому выходу блока, а первый вход - к первому входу блока.

Блок 5 фиксации ошибок (фиг.2) предназначен для обнаружения ошибки при приеме информации из оперативной памяти и запуске соответствующей

микропрограммы -обработки этой ошибк Блок 5 содержит формирователь 38 синдромов модифицированного кода Хэмминга, дешифратор 39, элементы 40-44 ИЛ триггер 45 запроса на приостановку п ошибке, триггер 46 запрета приема информации в .дополнительный регистр 7, регистр 47 контрольных разрядов,формирователь 48 контрольных разрядов модифицированного кода Хэмминга,вход которого подключен к третьему входу блока, а выход - к входу регистра 47 вход-выход которого подключен к входу-выходу блока, а выход к перво му входу узла 38, второй вход которого соединен с вторым входом блока, а выход - с входом дешифратора 39, выходы которого подключены к первому и третьему выходам блока, а также к входам элементов 40 - 43 И, выходы которых подключены к третьему выходу блока, а выходы элементов 42 и 43 ИЛИ подключены, кроме того, к первому и второму входам элемента 44 ИЛИ/ выход которого заведен на первыйвход триггера 45, единичный выход которого подключен к второму выходу блока, а второй и третий входы к первому входу блока, с которым соединены также первый и второй входы триггера 46, нулевой выход кото-.

рого подключен к четвертому выходу блока.

Блок 6 анализа ошибок в слове Сфиг.З) служит для регистрации количества ошибок в слове в процессе выполнения микропрограммы обработки ошибок и вырабатывает признаки перехода -в самой микропрограмме. Блок б содержит пороговый элемент 49 И, элементы 50-52 НЕ, элементы 53-55 И, триггеры 56-59 определения числа ошибок в слове, сумматор 60 по модулю два пороговый элемент 61. И, вход которого, а также входы узла 60 и порогового элемента 49 И подключены к первому входу блока, а выходы их подключены соответственно к входам элементов 51, 50-52 НЕ.Кроме того, выходы узла 60 и пороговых элементов 61 и 49 И подключены соответственно к первому входу элемента 53 И, к первому входу элемента 55 И и управляющему входу триггера 59, а выходы элементов 50-52 НЕ соединены соответственно с первым входом элемента 54 И, вторыми входами элементов 53 .и 54 И, и вторым входом элемента 55 И, выход которого, а также выходы элементов 53 и 54 И. заведены соответственно на управляющие входы триггеров 56-58, единичные выходы которых, а также единичный выход триггера 59 подключены к выходу блока, а синхронизирующие входы триггеров подключены к второму входу блока

Процессор работает следующим образом.

Операция ввода-выводй осуществляется с помощью канальной программы, состоящей из ряда управляющих слов канала. Управляющее слово канала содержит всю необходимую информацию для выполнения операции ввода-вывода а именно: код операции, адрес данных счетчик количества передаваемых байтов и специальные флажки, модифицирующие канальную программу. Канальная программа хранится в оперативной памяти процессора и, по мере необходимости , очередное управляющее слово канала извлекается из оперативной памяти (на фиг.1 не показана) через шины 22, блок 3 и входные-информационные шины 11 и загружается в операт Дионный блок 2 и адресуемый канал 8(9,10) ввода-вывода.

Дальнейшее управление операцией ввода-вывода осуществляется под управлением этого управляющего слова канала, которое называется текущим. Первое управляющее слово канала канальной программы извлекается из оперативной памяти по инициативе центрального процессора (на фиг.1 не показан), который выцает специальную команду, поступающую в блок 1 через шины 16 центрального процессора и содержащую адрес канала и адрес внешнего устройства, для которогодолжна

быть начата операция ввода-вывода. Адреса канала и внешнего устройства загружаются в регистр 24, а код команды - в регистр 23. В блоке 1 принятая команда дешифрируется дешифратором 25, и сигнал запроса на выполнение этой команды поступает в блок 37 через запросные шины 14. Блок 37 в каждом машинном такте анализирует запросы на приостановку, поступающие из блока 1, из каналов 8-10 ввода-вывода и блока 5.

Если в данный момент процессор ввода-вывода находится в режиме ожидания или выполняется менее приоритеная микропрограмма по сравнению с запросом на обслуживание команды центрального процессора, по сигналу запроса на приостановку, поступающего из блока 1 через запросные шины 14, выполнение текущей микропрограмм приостанавливается, адрес следующей микрокоманды прерванной микропрограМмы заносится в регистр 34, а в регистр 35 через блоки 37 и 33 заносится начальный, адрес микропрограммы обслуживания команды центрального процессора. Так как запрос на обслуживание команды процессора не являет самым приоритетным, для сохранения адреса прерванной микропрограммы содержимое регистра 34 в начале микропрограммы обслуживания команды центрального процессора записывается через блок 27 в локальную память 28 блока 2.

В конце выполнения микропрограммы обслуживания команды центрального процессора из блока 2 через выходные информационные шины 12 адрес следующей микрокоманды приостановленной микропрограммы пересылается в регист 34 и далее в регистр 35 для продолжения выполнения приостановленной М1 кропрограммы. Микропрограмма обслуживания команды процессора анализирует состояние адресуемого канала, .извлекает из оперативной памяти командное слово, канала и загружает его в канал ввода-вывода 8 (9,10) и локальную память 28 через шины 22,основной регистр 30 и входные информационные шины 11.

Адресуемое внешнее устройство (на фиг.1 не показано) подключается к каналу, и на нем запускается операция ввода-вывода. При этом процессор ввода-вывода сигнализирует центральному процессору о завершении запуска операции ввода-вывода путем установки триггера 26. Начиная с этого момента, процессор ввода-вывода отключается от центрального процессора и работает самостоятельно. Операция ввода-вывода осуществляется с помощью набора микропрограмм, хранящихся в постоянной памяти 31, по которым производится обмен данными ме;аду устройством и каналом микропрограмма обслуживания передачи данных, считывание управляющих слов каналамикропрограмма обслуживания команды центрального процессора; завершение операции ввода-вывода-микропрограмма обслуживания канала . Возникающие в процессе работы запросы на обслуживание процессор делит по приоритетности и при наличии сигнала запроса наиболее приоритетной микропрограммы прерывает выполняемую менее приоритетную микропрограмму.

В процессе считывания информации из оперативной памяти могут возникать ошибки, хранения информации в оперативной памяти и в трактах считывания и передачи информации ме)(да1У оперативной памятью и процессором. Вероятности появления двойных и тройных ошибок приближаются к вероятности появления одиночной ошибки. Поэтому, для коррекции одиночной,двойной и тройной ошибок в процессор введены дополнительный регистр 7 данных оперативной памяти, блок 5 фиксации ошибки и блок 6 анализа числа ошибок в слове. Коррекция перечисленных ошибок осуществляется под управлением микропрограмм. Информация хранится в оперативной памяти в модифицированном коде Хэмминга, т.е. информационное слово дополняется контрольным словом, разряды которого сформированы по правилу модифицированного .кода Хэмминга, отличающе гося от обычного кода Хэмминга тем, что самому информационному слову и его обратному значению ставится в соответствие одинаковое контрольное слово. При считывании информационного слова из оперативнойпамяти по адресу, хранящемуся в регистре 29, информационное слово через шины 22 оперативной памяти заносится в основной 30 и дополнительный 7 -регистры данных оперативной памяти. Контрольное слово, соответствующее содержимому информационного слова, а также содержимое основного регистра 30 поступают в блок 5 через шины 22-20. При неипичии ошибки блок 5 формирует следующие сигналы на шины 18 типа ошибки: ошибка в одном из разрядов информационного слова, -ошибка в одном из разрядов контрольного слова, двойная ошибка в информационном слове, тройна1я ошибка в информационном слове. При отсутствии ошибки на шины 18 выдается специальный сигнал,указывающий на отсутствие оиибки.

Одновременно с формированием типа ошибки на шинах 18 блок 5 вырабатывает сигнал на шине 15 запроса на приостановку, по которым в -узле 33 формируется один из фиксированных адресов микропрограммыj обрабатывающей одну из перечисленных ошибок.Коррекция ошибки в одном из информационныхили контрольных разрядах информационного или контрольного слова выполняется как в известном процессоре.

Микропрограмма коррекции двухкратной ошибки работает следующим образом.

Информационное слово с инверсных выходов регистра 30 со старыми контрольными разрядами, хранящимися в блоке 5, записывается в оперативную память через шины 22.

йлполня;ется чтение слова из опе0ративной памяти, информационное слово записывается в регистр 30, контрольное - в блок 5. При чтении оперативной памяти значение информации в дополнительный регистр 7 блоки5руется сигналом на шине.21, поступа бщему из блока 5.

После чтения слова из оперативной памяти производится поразрядное сравнения информационного слова основного регистра 30 с инвертирован0ным информационным словом дополнительного регистра 7. Поразрядное сравнение производится с помощью операционного блока 2, для чего содержимое основного 30 и дополни5тельного 7 регистров поступает в блок 2 через шины 11. Наличие единиц в разрядах результирующего информационного слова указывает на наличие . ошибок в данных разрядах.

0

Результирующее информационное слово запоминается в блоке 2, ангшизируетск на нуль, а также выдается через шины 12 в блок 6 анализа числа ошибок в слове. Блок 6 по наличию

5 единиц в результирующем информационном слове вырабатывает признаки однократной, двухкратной, трехкратной, четырехкратной и более кратной ошибки в информационном слове, прочи0танном из оперативной памяти. Эти признаки поступают в узел 36 через . шины 17 для последующего анализа и ветвлений в микропрограмме.

Если результирующее информационное слово имеет нулевое значение,

5 микропрограмма коррекции двухкратной ошибки заканчивается , так как дву скратная ошибка имеет место в контрольном слове. В этом случае информационное слово из регистра 7 пере0сылается в регистр 30 через блок 2.

Если результирующее информационное слово имеет четырехкратную или более кратную ошибку, блок 6 вырабатывает на шинах 17 признак, по кото5рому производится переход к микропрограмме обработки аппаратной ошибки.

Если по результирующему информационному слову блок б вырабатывает однократную, двухкратную или трех0кратную ошибку, -информационное слово из регистра 7 передается через входные информационные шины 11 в блок 2, который инвертирует в этом слове разряд (ы) с ошибкой (ами), указан5

ный (ые) в результируюцем информационном слове, запомненном в блоке 2. Скорректированное информационное слово через шины 12 засылается в регистр 30. Информационное слово из регистра -30 через шины 20 подается в блок 5 для.формирования синдромов модифицированного кода Хэмминга. По сфс5рмированному синдрому в блоке 5 и кратности ошибок, признак которой находится в блоке 6, может сформироваться четыре вида коррекции двойной ошибки:

из регистра 7 записывается в регистр 30 через операционный блок 2.

Микропрограмма коррекции трехкратной ошибки выполняется аналогично коррекции двухкратной ошибки, далее коррекция происходит следующим .,

Если результирующее информационное слово имеет нулевое значение, блок б вырабатывает на шине 17 признак, указывающий, что содержимое регистра 7 -является безошибочным, после чего информационное слово из дополнительного регистра 7 пересылается в регистр 30 через блок 2. Ошибочным в этом случае является контрольное слово. На этом микропрограмма коррекции тройной ошибки заканчивается , так как информационное слово не содержит ошибки.

Если результирующее информационное слово имеет ненулевое значение, производится переход к микропрограмме обработки аппаратной ошибки.

После завершения микропрограммы коррекции двух- или трехкратной ошибки производится переход к прерванной микропрограмме процессора ввода-вывода.

Контрольные разряды, поступающие через шины 22 или из формирователя ,48, на вход-которого поступает инфомационное слово из дополнительного регистра данных оперативной памяти по выходным информационным шинам 19 заносятся в регистр 47, а затем вместе с информационным словом осноного регистра данных оперативной памяти, поступающим по выходным информационным шинам 20, подаются через узел 38 на вход дешифратора 39 синдромов. Информация с выхода дешифратора 39 поступает на входные информационные шины 11, указывая номер разряда с ошибкой для дальнейшего анализа в микропрограмме обрат ботки двухкратной ошибки, или непосредственно на шины 18, указывая на отсутствие ошибки в информационном слове, или через элементы ИЛИ 40-43 на шины 18, иницируя соответственно однократную ошибку в информационном слове, однократную ошибку в контрольном слове, двухкратную ошибку в информационном слове и трехкратную ошибку в информационном слове. В Случае двухкратной или трехкратной ошибки в информационном слове высокий сигнал с выхода элемента 44 ИЛИ устанавливает триггер 45 по синхросигналу, поступающему по управляющим шинам 13. Триггер 46 устанавливается в процессе выполнения микропрограммы обработки- двухкратных ошибок по Сигналу на управляющей шине 13. Сброс обоих триггеров осуществляется по сигналу на управляющей шине. 13.

В процессе выполнения микропрограммы коррекции двухкратной ошибки результирующее информационное слово поступает из операционного блока через выходные информационные шины 12 на узел 60, пороговый элемент 61 И и пороговый элемент 49 И. По числу единиц в результирующем информационном слове срабатывают пороговые элементы 61 и 49 и и узел 60. Если число единиц ,больше или равно трем (неверны три или более информационных разрядов), на выходе порогового элемента 61 И появляется высокий потенциал. Если же число больше или равно четырем- (неверны четыре или более разрядов), на выходе порогового элемента 49 И появляется высокий сигнал. Узел 60 работает как обычная свертка по модулю два. Сигналы с выходов элементов 60, 61 и 49 через систему элементов 50-55 устанавливают один из триггеров 56, 57 или 58. Триггер 59 устанавливается непосредственно при наличии высокого потенциала на выходе порогового элемента 49 И. Выходы триггеров подключены к шинам 17 кода числа ошибок. Установка и сброс триггеров синхронизируется сигналом через управляющие шины 13.

Изобретение позволяет, в отличие, от известного процессора значительно повысить надежность -системы.

Формула изобретения

Процессор ввода-вывода с коррекцией ошибок, содержащий блок формирования, блок управления оперативной памятью, операционный блок, блок микропрограммного управления и каналы ввода-вывода, при этом вход-выход блока управления подключен к шине центрального процессора, запросный выход блока управления подключен к первым выходам каналов ввода-вывода и через шину запроса соединен с входом запроса блока микропрограммного управления, выход приостанова микропрограммы которогоподключен к входу каждого канала ввода-вывода и через выходную информационную шину с адресным входом блока управления, с первым входом операционного блока и адресным входом блока управления оперативной памятью, первый вход-выход которого соединен с шиной оператив.ной памяти, адресный выход блока

0 управления оперативной памятью подключен к шине оперативной памяти, ервый выход блока управления операт71вной памятью через .входную информационную шину подключен к

5 адресному выхо.ду блока управления, к первому входу операционного блока,к выходу приостанова микропрограм1.1ы блока микропрограммного управления и второму выходу каждого канала ввода-вывода, управляющий

0 выход микрокоманд блока микропрограммного управления подключен к второму входу операционного блока, отличающийся тем, что, с целью повышения надежности, в него введены

5 блок анализа числа ошибок, блок фиксации ошибок и регистр данных, при этом вход- выход регистра данных подключен к шине оперативной памя-. ти, вход-выход блока фиксации ошибок

D соединен с шиной оперативной памяти, первый выход блока фиксации ошибок через шину запрета подключен к первому входу регистра данных, первый выход которого через выходную информа5ционную шину подключен к первому входу блока фиксации ошибок, второй выход которого соединен с вторым выходом регистра данных и через входную информационную шину подключена к первому входу, операционного бло-г

0 ка, второй вход регистра данных соединен с первым выходом операционного блока, адресным входом блока управления оперативной памятью и через выходную информационную шину к пер5вому входу блока анализа числа ошибок, второй вход которого через управляющую шину подключён к управляющему выходу блока микропрограммного управления и второму входу

0 блока фиксации ошибок, третий вход которого подключен к информационному выходу блока управления оперативной памятью, третий выход блока фиксации ошибок через шину запроса

5 соединен с запросным входом блока микропрограммного управления, четвертый выход блока фиксации ошибок подключен к первому и второму адресному входам блока микропрограммного управления, третий адресный вход

0 которого подключен к выходу блока анализа.

триггер запроса, триггер запрета, деиюфратор, формирователь синдрома, формирователь контрольных разрядов и регистр, при этом вход формирователя контрольных разрядов является первым входом блока, выход формирователя контрольных разрядов соединен с входом регистра/ вход-выход которого является первым входом-выходом блока, выход регистра подключен к первому входу формирователя синдрома, второй вход которого является третьим входом блока, выход формирователя синдрома подключен к входу дешифратора, группа выходов которого, кроме первого, подключена к соответствующим входам каждого элемента ИЛИ, при этом г.ервая группа выходов дешифратора является вторым выходом блока, первый выход дешифратора и группа выходов каждого элемента. ИЛИ, кроме второго, являются четвертым выходом блока, третьим выходом которого является выход триггера запроса, первый вход которого подключен к выходу второго элемента ИЛИ, первый вход которого подключен к выходу третьего элемента ИЛИ, а второй вход - к выходу четвертого элемента ИЛИ, единичный вход триггера запроса, триггера запрета и объединенные сбросовые входы триггеров являются группой входов блока первый выходом которого является нулевой выход триггера запрета, выход триггера запроса является третьим выходом блока.

содержит триггеры, элементы И и НЕ, пороговые элементы и сумматор по модулю два, при этом вход сумматора по модулю два объединен с входами пороговых элементов и является первым ВХОДОМ блокэ, ВЫХОД сумматора по модулю два подключен к входу первого элемента НЕ и первому входу первого элемента И, выход каждого элемента И подключен к управляющему

входу соответствующего триггера.

кроме последнего, синхронизирующие входы которых объединены и являются вторым входом блока, выходы триггеров являются выходом блока, выход первого порогового элемента подключей к входу второго элемента НЕ и первому входу второго элемента И, второй вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с управляющим входом

последнего триггера и выходом второго порогового элемента, выход второго элемента НЕ подключен к первому входу третьего элемента И, второй вход которого объединен с йторым

входом первого элемента И и подклюены к выходу второго элемента НЕ.

Источники информации, принятые во внимание при экспертизе

1; Катцан, Вычислительные машины системы 370-. М., Мир, 1974.

мТЫрч

т

фиг:.2

Авторы

Даты

1981-07-23—Публикация

1979-09-05—Подача