и с вторым установочным входом триггера адреса слова, выход которого связан с управляющим входом второго коммутатора, выход которого соединен с информационным входом регистра микрокоманд, выход сумматора по модулю два соединен с первым информационным входом второго коммутатора, выход второго элемента И соединен с первым информационным входом регистра ошибок, выход которого является выходом ошибок устройства, выход элемента ИЛИ соединен с вторым входом второ119. . го элемента И, выход регистра синдромов соединен с входом .элемента ИЛИ, второй выход дешифратора соединен с вторым информационным входом регистра ошибок, вход синхронизации устройства соединен с тактовыми входами регистра ошибок, регистра адреса буферного регистра адреса и триггера адреса слова, второй выход блока формирования кода Хэмминга с единен с вторым информационным входом второго коммутатора .

| название |

год |

авторы |

номер документа |

| Запоминающее устройство с самоконтролем |

1984 |

- Смирнов Геннадий Дмитриевич

- Запольский Александр Петрович

- Подгорнов Анатолий Иванович

- Костинский Аркадий Яковлевич

- Шугаев Александр Михайлович

|

SU1243032A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК |

1979 |

- Абражевич Ремуальд Игнатьевич

- Аверьянов Вадим Алексеевич

- Верига Маргарита Андреевна

- Овсянников Валерий Иванович

- Погодаев Валерий Викторович

- Яловега Алексей Григорьевич

|

SU849221A1 |

| Устройство для управления каналами |

1984 |

- Запольский Александр Петрович

- Пронин Владислав Михайлович

- Хамелянский Владимир Семенович

- Цесин Борис Вульфович

- Рымарчук Александр Григорьевич

|

SU1372329A2 |

| Микропрограммное устройство для управления каналами ЭВМ |

1982 |

- Верига Маргарита Андреевна

- Овсянников Валерий Иванович

- Погодаев Валерий Викторович

- Сиротко Елена Анатольевна

- Церлюкевич Алла Иосифовна

|

SU1068938A1 |

| Процессор с совмещением операций |

1982 |

- Елисеев Александр Александрович

- Мацуев Виталий Иванович

- Петушков Александр Николаевич

- Роговская Татьяна Ивановна

|

SU1138805A1 |

| Устройство для восстановления работы процессора |

1984 |

- Запольский Александр Петрович

- Пронин Владислав Михайлович

- Хамелянский Владимир Семенович

- Цесин Борис Вульфович

|

SU1179342A1 |

| Микропрограммное устройство управления |

1984 |

- Подгорнов Анатолий Иванович

- Мойса Ромуальд Станиславович

- Костинский Аркадий Яковлевич

- Шугаев Александр Михайлович

|

SU1262516A1 |

| Микропрограммное устройство управления |

1984 |

- Костинский Аркадий Яковлевич

- Безруков Владимир Александрович

- Рымарчук Александр Григорьевич

|

SU1264172A1 |

| Устройство защиты от ошибок внешней памяти |

1981 |

- Типикин Александр Петрович

- Петров Вячеслав Васильевич

- Горшков Николай Васильевич

- Токарь Александр Петрович

- Бабанин Александр Герасимович

- Пеньков Александр Георгиевич

- Гвоздев Владимир Викторович

|

SU1018119A1 |

| Процессор |

1984 |

- Лопато Георгий Павлович

- Смирнов Геннадий Дмитриевич

- Чалайдюк Михаил Фомич

- Пыхтин Вадим Яковлевич

- Асцатуров Рубен Михайлович

- Запольский Александр Петрович

- Подгорнов Анатолий Иванович

- Пронин Владислав Михайлович

- Шкляр Виктор Борисович

|

SU1247884A1 |

УСТРОЙСТВО ДОЯ КОРРЕКЦИИ ШКРОКОМАНД, содержащее блок памяTHj выходной регастр, блок фррьмрования кода Хэмьшнга, схему сравнения, регистр , дешифратор, сумматор по модулю два, триггер блокировки, регистр микрокоманд, первый элемент И, причем выход блока памяти соединен с инфор.мациоыным входом выходного регистра, выход информационных разрядов которогосоединен с входом блока формирования кода Хэмминга и первым информационным входом сумматора по модулю- два, первый выход блока форьмрования кода Хэмминга соединен с первым входом схемы сравнения, выход контрольных разрядов выходного регистра соединен с вторым входом схемы сравнения, выход которой соединен с входом триггера блокировки и регистра синдромов, выход которого соединен с вxoдa м дешифратора, первый выходкоторого соединен с вторым входом сумматора по модулю два, выход сумматора по модулю два связан с информационным входом блока памяти, прямой выход триггера Г , I . ----ЛЛ. блокировки соединен с вторым входом выходного регистра, вход синхронизации устройства соединен с тактовым входом выходного регистра, тактовым входом регистра синдромов, входами синхронизации триггера блокировки, регистра микрокоманд и первым входом первого элемента И, инверсный выход триггера блокировки связан с вторым входом первого элемента И, выход которого соединен с входом записи блока памяти, выход контрольных разрядов выходного регастра соединен с третьим информационным входом сумматора по модулю два, выход регистра микрокоманд соединен с выходом микро(Л команд устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены регистр адреса, два коммутатора, буферный регистр адреса, элемент ИЛИ, второй элемент И, триггер адреса слова, регистр ошибок, причем выход регистра адреса связан 05 4 с адресным входом блока памяти н информационным входом буферного регистра адреса, выход которого соединен с О первым информационным входом первосо го коммутатора, выход которого соединен с информационным входом регистра адреса, прямой выход триггера блокировки соединен с управляющим входом первого коммутатора, первым входом второго элемента И, входом разрешения записи буферного регистра адреса, первым установочным входом триггера адреса слова и является выходом блокировки устройства, адресный вход устройства соединен с вторым информа-ционным входом первого коммутатора

1

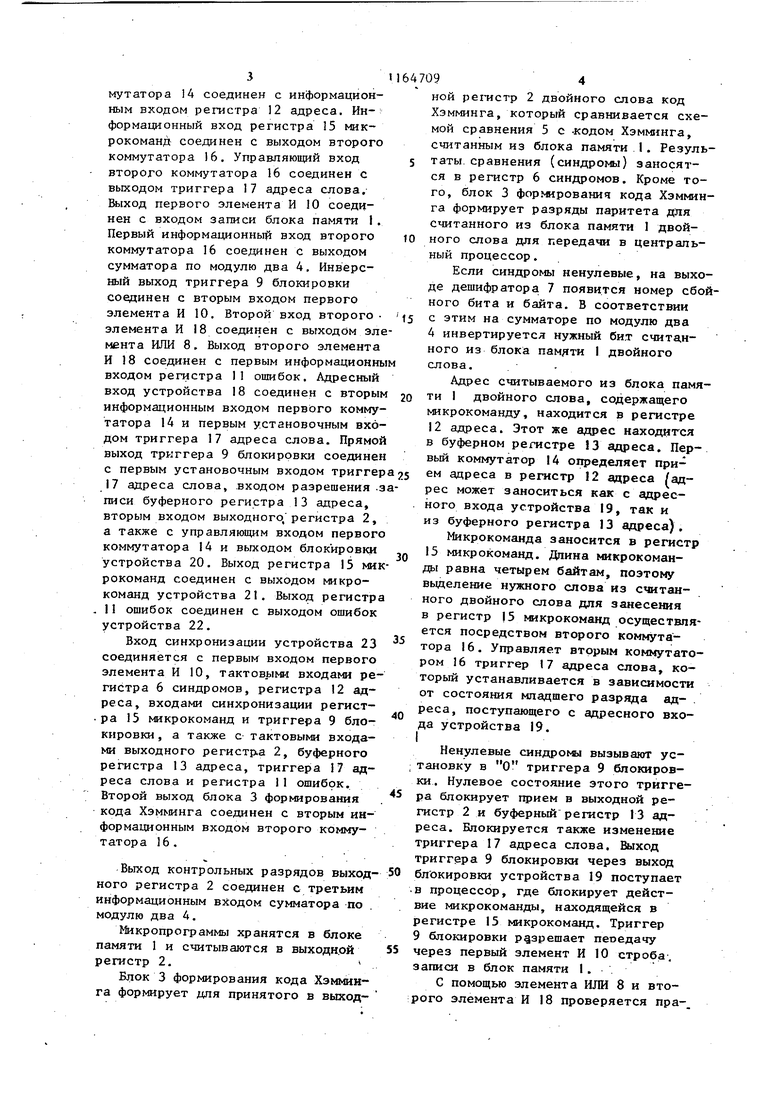

Изобретение относится к вычислительной технике и может быть использовано при построении устройств микропрограммного управления.

Цель изобретения - повышение быстродействия,

Изобретение корректирует случайные ошибки, возникающие в управляющей памяти процессора в процессе цикла коррекции. При этом введение режима коррекции не требует удлинения цикла процессора (в сравнении с прототипом), что в конечном счете ведет к повышению быстродействия процессора.

На (}иг. I изображена схема устройства для выборки микрокоманд; на фиг. 2 - временная диаграмма работы устройства.

Устройство для выборки к«крокома ды (фиг. 1) содержит блок памяти 1, выходной регистр 2, блок 3 формирования кода Хэмминга, сумматор по модулю два 4, схему сравнения 5, регистр 6 синдромов, дешифратор 7, элемент ИЛИ 8, триггер 9 блокировки, первый элемент И 10, регистр ошибок 11, регистр 12 адреса, буферный регистр 13 адреса, первый коммутатор 14, регистр 15 г крокоманд, второй коммутатор 16, триггер 17 адреса слова, второй элемент И 18, адрес1л 1й вход устройства 19, выход блокировки устройства 20, выход микрокоманд устройства 21, выход ошибок устройства 22, вход

синхронизации устройст за 23. Выход блока памяти 1 соединен с информационным входом выходного регистра

2. Выход информационных разрядов выходного регистра 2 соединен с входом блока 3 формирования кода Хэмминга и первым информационным входом сумматора по модулю два 4. Выход сумматора по модулю два 4 соединен с информационным входом блока памяти 1. Первый выход блока 3 формирования кода Хэммингс соединен с первым входом схемы ср 1внения 5.Выход контрольных разрядов выходного регистра 2 соединен с вторым входом схемы сравнения 5. Выход схемы сравнения 5 соединен с входом регистра 6 синдромов, выход которого соединен с входами дешифратора 7 и элемента ИЛИ 8. Первый выход дешифратора 7 соединен с вторым входом сумматора по модулю два 4. Выход схемы сравнения 5 соединен с входом триггера 9 блокировки. Прямой выход триггера 9 блокировки соединен с первым входом второго элемента И 18. Второй информационный вход регистра 1I ошибок соединен с вторым выходом дешифратора

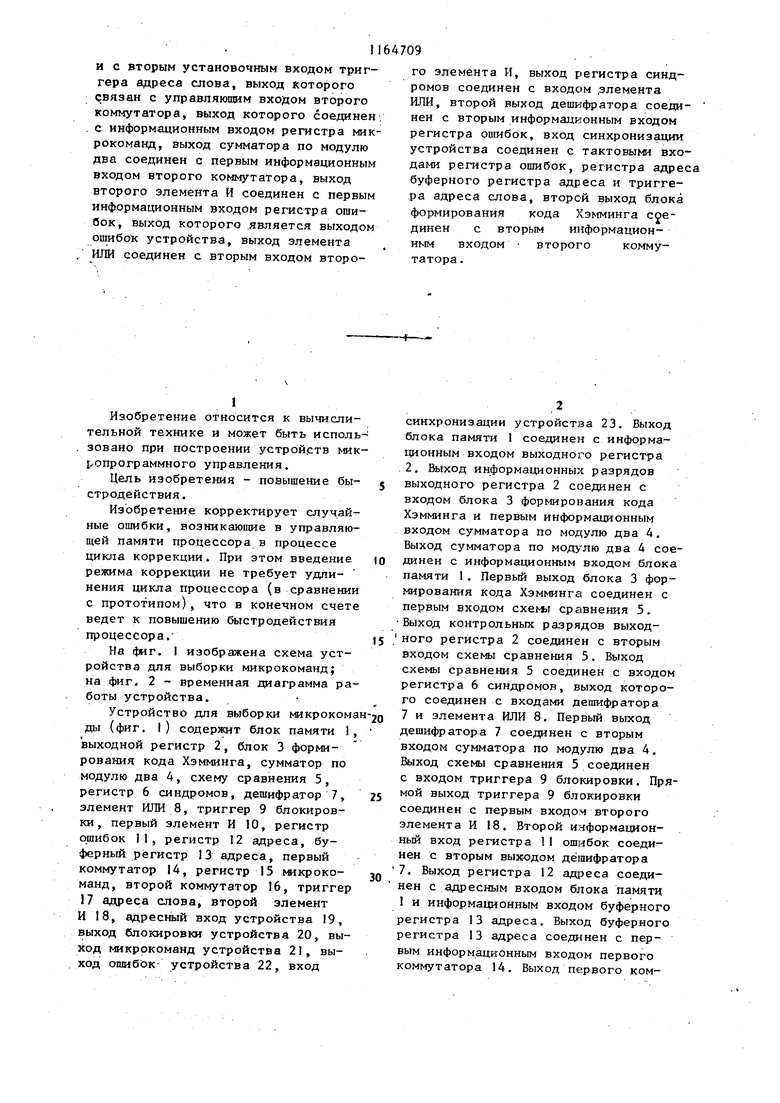

7. Выход регистра 12 адреса соединен с .адресным входом блока памяти 1 и информационным входом буферного регистра 13 адреса. Выход буферного регистра 13 адреса соединен с первым информационным входом первого коммутатора 14, Выход первого коммутатора 14 соединен с информационным входам регистра 12 адреса. Информационный вход регистра 15 микрокоманд соединен с выходом второго коммутатора )6. Управляющий вход второго коммутатора 16 соединен с выходом триггера 17 адреса слова. Выход первого элемента И 10 соединен с входом записи блока памяти I, Первый информационный вход второго коммутатора 16 соединен с выходом сумматора по модулю два 4, Инверсный выход триггера 9 блокировки соединен с вторым входом первого элемента И 10. Второй вход второгоэлемента И 18 соединен с выходом эл мента ИЛИ 8. Выход второго элемента И 18 соединен с первым информационны входом регистра 11 ошибок. Адресный вход устройства 18 соединен с вторы информационным входом nepBiaro коммутатора 14 и первым установочным вхо дом триггера 17 адреса слова. Прямо выход триггера 9 блокировки соедине с первым установочным входом триггер 17 адреса слова, .входом разрешения . писи буферного регистра 13 адреса, вторым входом выходного,регистра 2, а также с управляющим входом первог коммутатора 14 и выходом блокировки устройства 20. Выход регистра 15 ми рокоманд соединен с выходом микрокоманд устройства 21. Выход регистр . 11 ошибок соединен с выходом ошибок устройства 22. Вход синхронизации устройства 23 соединяется с первым входом первого элемента И 10, тактовыьда вxoдa Ф ре гистра 6 синдромов, регистра 12 адреса, входами синхронизации регист. ра 15 микрокоманд и триггера 9 блокировки , а также с тактовыми входами выходного регистр.а 2, буферного регистра 13 адреса, триггера 17 адреса слова и регистра 11 ошибок. Второй выход блока 3 формирования кода Хэмминга соединен с вторым информационным входом второго коммутатора 16. Выход контрольных разрядов выходного регистра 2 соединен с третьим информационным входом сумматора по модулю два 4. Микропрограммы хранятся в блоке памяти 1 и считываются в выходн.ой регистр 2. БЛОК 3 формирования кода Хэмкиига формирует дпя принятого в выходной регастр 2 двойного слова код Хэмминга, который сравнивается схемой сравнения 5 с -кодом Хэммннга, считанным из блока памяти . 1. Результаты, сравнения (синдромы) заносятся в регистр 6 синдромов. Кроме того, блок 3 формирования кода Хэмминга формирует разряды паритета для считанного из блока памяти I двойного слова для передачи в центральный процессор. Если синдромы ненулевые, на выходе дешифратора 7 появится номер сбойного бита и байта. В соответствии с этим на сумматоре по модулю два 4 инвертируется нужный бит считанного из блока памяти I двойного слова. . Адрес считываемого из блока памяти I двойного слова, содержащего микрокоманду, находится в регистре 12 адреса. Этот же адрес находится в буферном регистре 13 адреса. Первый коммутатор 14 определяет прием адреса в регистр 12 адреса /адрес может заноситься как с адресного входа устройства 19, так и из буферного регистра 13 адреса). Микрокоманда заносится в регистр 15 микрокоманд. Длина микрокомаиды равна четырем байтам, поэтому выделение нужного слова из считанного двойного слова для занесения в регистр 15 икpoкoмaнд осуществляется посредством второго коммутатора 16. Управляет вторым коммутатором 16 триггер 17 адреса слова, который устанавливается в зависимости от состояния младшего разряда адреса, поступающего с адресного входа устройства 19. Ненулевые синдромы вызывают установку в О триггера 9 блокировки . Нулевое состояние этого триггера блокирует прием в выходной регистр 2 и буферный регистр 13 адреса. Блокируется также изменение триггера 17 адреса слова. Выход триггера 9 блокировки через выход блокировки устройства 19 поступает в процессор, где блокирует действие микрокоманды, находящейся в егистре 15 микрокоманд. Триггер блокировки разрешает пеоедачу через первый элемент И 10 строба, записи в блок памяти I. С помощью элемента ИЛИ 8 и втоого элемента И 18 проверяется пра- 5 . вильность установки триггера 9 блокировки. Любой ненулевой синдром с выхода регистра 6 синдромов череэ элемент ИЛИ 8 поступает на вход второго элемента И 18. Если триггер 9 блокировки при этом на ходится в 1, то на выходе второго элемента И 18 появится сигнал ошибки, который заносится в регист П ошибок. Туда же заносится призн двойной ошибки из дешифратора 7. На временной диаграмме работы устройства для выборки fliкpoкoмaнд приняты следующие условные обозначения а - установка регистра 12 адреса; б - установка буферного регистра 13 адреса; в - прием микрокоманды в регистр 15 микрокоманд г - изменение состояния триггера 9 блокировки; д - запись в блок па мяти 1 скорректированной микрокоманды, е - прием данных из блока памяти 1 в выходной регистр 2. Устройство для выборки кикроко.манд работает следующим образом. Микрокоманда заносится в регист 15 микрокоманды до окончания текущего цикла процессс1ра. Она дешифри ется и по состоянию ее адресной части по адресному, входу устройств 18 через первый коммутатор 14 в регистр 12 адреса заносится адрес следующей микрокоманды. Этот адрес поступает в блок памяти, где начинается выборка следующей микрокома ды. Одновременно анализируется счи танное двойное слово, содержащее данную |«1крокоманду, на наличие в . нем ошибок. В случае единичной оши ки устанавливается в О триггер 9 блокировки (в исходном состоянии он в 1). Он блокирует прием двойного слова из блока памяти I в выходной регистр 2, а также блокирует изменение триггера 17 адреса слова. Тем самым в следующем цигспе (цикле коррекции) в регистр 15 микрокоманд заносится скорректированная микрокоманда. В цикле коррекции по нулевому состоянию триггера 9 блокировки блокируется изменение буферного регистра 13 адреса. В этом случае он хранит адрес сбойного двойного слова. Этот адрес передается: в регистр 12 адреса через первый коммутатор 14. Тем самым вместо адреса очередной макрокоманды, сформированного в результате дешифрации сбойной микрокоманды, в регистр 12 адреса заносится адрес, по которому осуществляется запись скорректированного двойного слова. В следующем цикле производится выборка очередной микрокоманды и выполнение скорректированной микрокоманды. В памяти сбойная микрокоманда оказывается скорректированной, поэтому при последующей выборке этой микрокоманды необходимость в цикле коррекции отп.здает. Таким образом, устройство позволяет начинать выполнение микрокоманды, не дожидаясь результатов анализа считанного из памяти двойного слова, содержащего эту микрокоманду. Время анализа составляет окало 30% длительности цикла процессора. Тем самым повьш1ается быстродействие устройства.