Изобретение относится к вычислительной технике и может быть использовано для диагностирования запоминающего устройства, содержащего блок оперативной памяти, блок управления оперативной памятью, блок управления канальными операциями и другие блоки ЭВМ.

Известно устройство для фиксации неустойчивых сбоев, содержащее пять элементов И, три триггера, регистр, счетчик, два элемента ИЛИ, распределитель импульсов, блок обмена, блок памяти, два блока индикации. Недостатком этого устройства является отсутствие возможности локализации сбоев и отказов (1).га|

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому устройству является устройство для контроля оперативной памяти, содержащее генератор кода Хэмминга, блок коррекции контрольного кода, дешифратор ошибок, вход которого подключен к выходу блока обнаружения неисправностей, выходной регистр и входной регистр, входы которого подключены к первому и второму входам устройства, блок коррекции входной информации, селектор, регистр контрольного кода, регистр кода Хэмминга, блок сравнения коДа Хэмминга и контрольный блок сравнения, первый вход которого соединен с выходом блока обнаружения неисправностей, второй вход - с выходом блока коррекции контрольного кода и с первым входом выходного регистра, третий вход - с выходом

ч

со ел

Ј fO

регистра кода Хэмминга, первым входом блока обнаружения неисправностей и первым входом блока сравнения кода Хзммин- га, а четвертый вход - с выходом блока коррекции входной информации и вторым входом выходного регистра, к третьему входу которого подключены выход генератора кода Хэмминга, входы регистра кода Хэмминга и регистра контрольного кода, второй вход блока сравнения кода Хэмминга и первый вход блока сравнения паритета записываемой информации, второй вход которого соединен с выходом паритета входного регистра, выход кода Хэмминга которого подключен ко второму входу блока обнаружения неисправностей, а информационный выход - к первому входу селектора, четвертому входу выходного регистра, первому входу блока коррекции входной информации, второй вход которого соединен с выходом дешифратора ошибок и первым входом блока коррекции контрольного кода, второй вход которого подключен к выходу регистра контрольного кода, второй вход которого подключен к выходу регистра контрольного кода, выход селектора соединен со входом генератора кода Хэмминга, а второй вход - с первым входом устройства, третий вход устройства подключен к третьему входу входного регистра, ко второму входу дешифратора ошибок и к третьему входу блока сравнения паритета записываемой информации (2).

Недостатком такого устройства является отсутствие средств, фиксирующих и накапливающих корректируемые ошибки и некорректируемые ошибки (в частном случае, неустойчивые сбои), и невозможность их локализации.

Целью предлагаемого изобретения является расширение области применения устройства за счет регистрации,накопления и локализации корректируемых и некорректируемых ошибок.

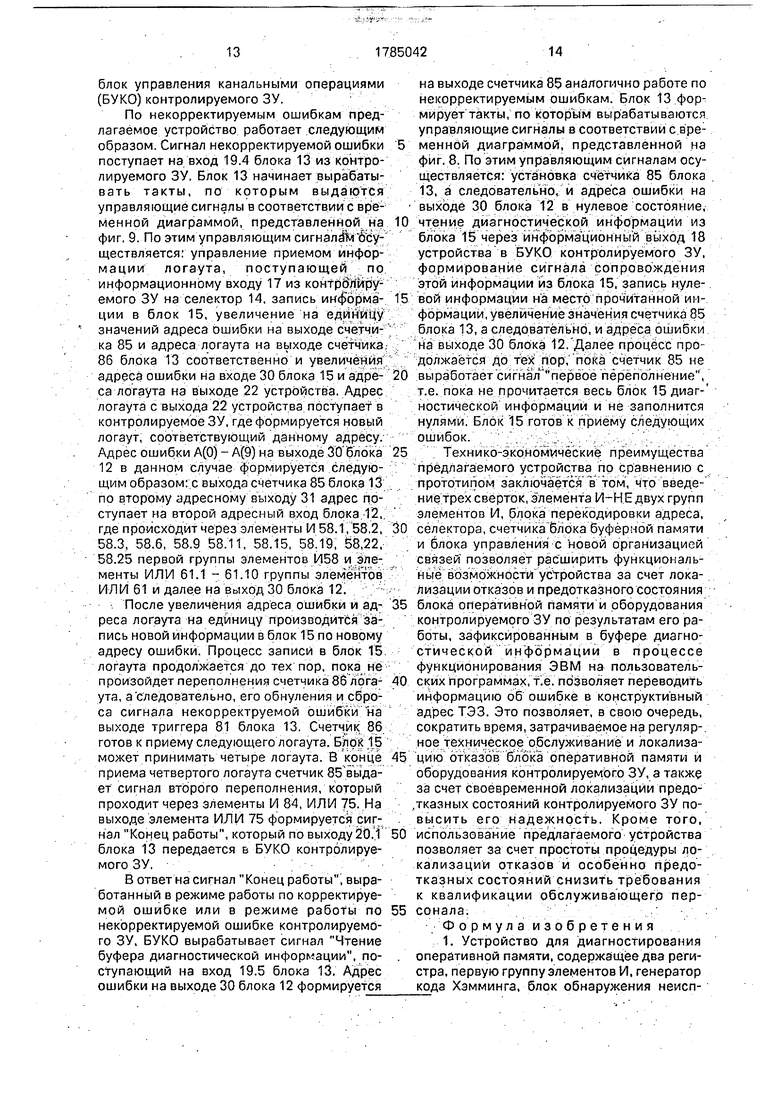

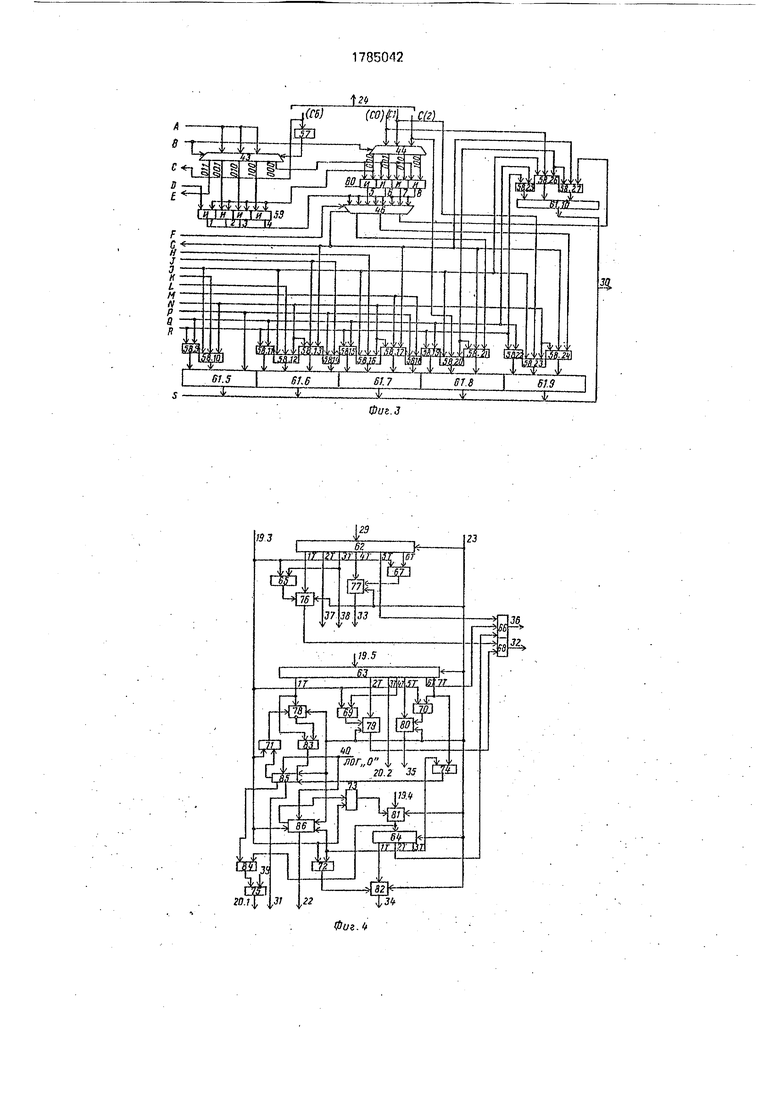

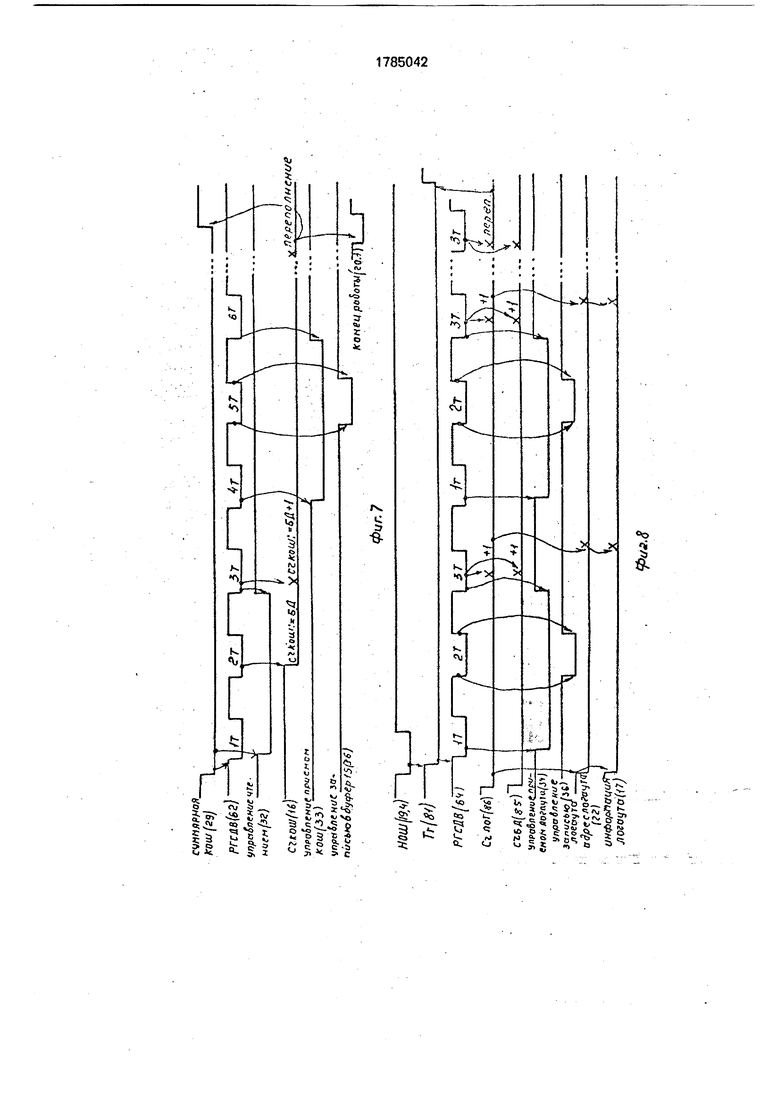

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг, 2, 4 - схема блока перекодировки адреса ошибки; на фиг. 4 - схема блока управления; на фиг. 5 - матрица модифицированного весового кода Хэмминга; на фиг. 6 - зоны фиксируемых ошибок и значения битов адреса ошибки, вырабатываемого блоком 12; на фиг. 7 - временная диаграмма работы предлагаемого устройства по сигналу Суммарная корректируемая ошибка ; на фиг. 8 - временная диаграмма работы предлагаемого устройства по сигналу Некорректируемая ошибка ; на фиг. 9 - временная диаграмма работы предлагаемого устройства по сигналу Чтение буфера диагностической информации ; на фиг. 10 - временная диаграмма формирования сигнала суммарная корректируемая ошибка при управлении из блока управления оперативной

памяти (БУОП) контролируемого запоминающего устройства (ЗУ).

Устройство для диагностирования запоминающего устройства (фиг. 1 содержит два регистра 1 и 2, первую группу элементов И

03, генератор 4 кода Хэмминга, блок 5 обнаружения неисправностей, дешифратор 6 корректируемых ошибок, три элемента 7, 8, 9 свертки по модулю два, элемент И-ИЕ 10, вторую группу элементов И 11, блок 12 пе5 рекодировки адреса ошибки, блок 13 управления, селектор 14 блок 15 буферной памяти, счетчик 16 корректируемых ошибок, группу информационных входов 17 и информационный выход 18 для подключения к ши0 не данных контролируемого ЗУ, группу управляющих входов 19 и группу управляющих выходов 20 устройства для подключения к шине управления контролируемого ЗУ, при этом входы с 19.1 по 19.6 и выходы

5 20.1 и 20.2 являются входами сигналов Рабочий режим, Режим сканирования, Начальная установка, Некорректируемая ошибка, Чтение буфера диагностической информации, Управление приемом ин0 формации, выходами сигналов Конец работы и Сопровождение информации устройства, адресный вход 21 и адресный выход 22 устройства для подключения к шине адреса контролируемого ЗУ, синхронизи5 рующий вход 23 устройства для подключения к шине синхронизации контролируемого ЗУ, вход 24 синдрома, вход 25 корректируемой одиночной ошибки в рабочем режиме, вход 26 корректируемой оди0 ночной ошибки в режиме сканирования, вход 27 корректируемой двойной ошибки в рабочем режиме, вход 28 корректируемой двойной ошибки в режиме сканирования, выход 29 суммарной корректируемой ошиб5 км и выход 30 адреса ошибки блока 12, выходы 31 - 38, вход 39 переполнения блока 13 управления, вход 40 логического О устройства.

Блок 12 перекодировки адреса ошибки

0 (фиг. 2, 3) содержит дешифратор 41 номера мегаслова, три дешифратора 42, 43, 44 синдрома, шифратор 45 информационных разрядов, шифратор 46 контрольных разрядов, семь элементов ИЛИ 47-53, два элемента И

5 54, 55, два элемента НЕ 56, 57, три группы элементов И 58, 59, 60, группу элементов ИЛИ 61.

Блок 13 управления (фиг. 4) содержит три регистра 62, 63, 64 сдвига, одиннадцать элементов ИЛИ 65-75, семь триггеров 7682, два элемента И 83, 84, счетчик 85 диагностики и счетчик 86 состояния.

Посредством шины данных, шины управления, шины синхронизации, и шины адреса предлагаемое устройство подключается к контролируемому ЗУ.

На информационные входы группы информационных входов 17 устройства поступают информация и коды Хэмминга из блока оперативной памяти контролируемо- го ЗУ и информация логаута из всех других блоков контролируемого ЗУ.

На управляющие входы группы управляющих входов 19 устройства поступают следующие сигналы: на вход 19.1 Рабочий режим, на вход 19.2 Режим сканирования, на вход 19.3 Начальная установка и на вход 19.6 Управление приемом информации - из блока управления оперативной памятью контролируемого ЗУ, на вход 19,4 Некорректируемая ошибка и на вход 19.5 Чтение буфера диагностической информации - из блока управления канальными операциями контролируемого ЗУ. Диагностическая информация информационного выхода 18 устройства и управляющая информация с выхода 20.1 Конец работы и выхода 20.2 Сопровождение информации поступает в блок управления канальными операциями контролируемого ЗУ. .

Блок оперативной памяти контролируемого ЗУ объемом 72 Мегабайта организован в виде 9 Мегаслов по 72 разряда (64 информационных разряда и 8 разрядов кода Хзм- минга) и конструктивно расположен в четырех панелях в виде 9 мегаслов по 18 разрядов в1 каждой. Каждый разряд блока оперативной памяти контролируемого ЗУ (9 Мегаслов) конструктивно расположен в трех накопительных ТЭЗ и определяется двадцатью четырьмя разрядами адреса, В шестрадцатиричном коде адресация разрядов блока оперативной памяти контролируемого ЗУ следующая:

1 ТЭЗ - ООООООш - 2ГГГГГ16 - (0/2 Мслово) 2ТЭЗ - ЗГГГГГш - 5ГГГГП6 - (3/5 Мслово) 3 ТЭЗ - 6ГГГГГ16 - 8ГГГГГ16 - (6/8 Мслово)

Первые четыре разряда адреса блока оперативной памяти контролируемого ЗУ, поступающие в предлагаемое устройство по адресному входу 21, характеризуют номер Мегаслова и используются для формирования адреса ошибки.

Генератор 4 кода Хэмминга содержит элементы, реализующие функцию сложения по модулю два. Для 64 информационных разрядов генератор вырабатывает 8 сумм по модулю два (СО - С6, СК), именуемых кодом Хэмминга (см. фиг. 5).

Блок 5 представляет собой К (К - число символов кода Хэмминга) двухвходовых элементов, реализующих функцию сложения по модулю два символов кода Хэмминга. прочитанных из блока оперативной памяти контролируемого ЗУ с соответствующими символами кода Хэмминга, выработанными генератором 4 кода Хэмминга.

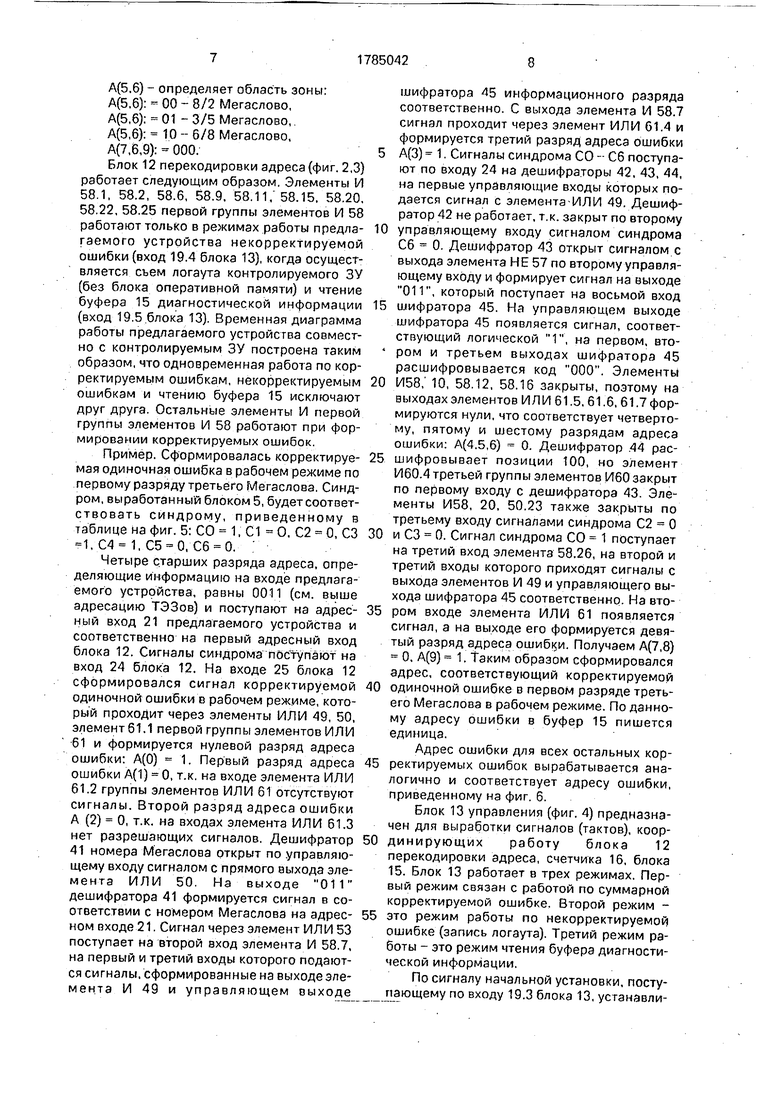

Блок 12 перекодировки адреса ошибки предназначен для выработки сигнала Суммарной корректируемой ошибки (выход 29) и адреса А(0) - А(9) ошибки (выход 30) в соответствии с- таблицей, приведенной на фиг. 6. Зона логауты. представленная в таблице на фиг. 6, формируется при появлении сигнала Некорректируемая ошибка на входе 19.4 устройства. По данной ошибке осуществляется съем логаута (информации о состоянии блоков контролируемого запо минающего устройства без учета блока оперативной памяти). Зоны корректируемых одиночных и двойных ошибок в рабочем и в режиме сканирования (КОШ1р, КОШ1ск, КОЩ2р, КОШ2ск)формируются при появлении соответствующих корректируемых ошибок блока оперативной памяти.

Адрес ошибки, вырабатываемый блоком 12 на выходе 30, формируется следующим образом (см. фиг. 6).

А(0) - определяет вид ошибки,

А(0): 0 - некорректируемая ошибка, по которой осуществляется запись логаутл,

А(0): 1 - корректируемая ошибка,

А(1) - характеризует режим работы,

А(1): 0 - рабочий режим,

А(1): 1 - режим сканирования.

При появлении одиночных корректируемых ошибок в информационных разрядах:

А(2,3) - определяет область зоны.

А(2,3): 00 - 0/2 мегаслово,

А(2,3): 01 - 3/5 мегаслово,

А(2,3): 10 - 6/8 мегаслово,

А(4,5,6,7,8,9) - определяет код номера информационного разряда (на выходе шифратора 45 блока 12).

При появлении одиночных корректируемых ошибок в контрольных разрядах:

А(2.3): 11,

А(4): 0й,

А(5,6) - определяет области зоны;

А(5,6): 00 - 0/2 мегаслово;

А(5,6): ,01 - 3/5 мегаслово,

А(5,6): 10 - 6/8 мегаслово,

А(7,8,9) - определяет код номера контрольного разряда (на выходе шифратора 46 блока 12).

При появлении двойной корректируемой ошибки,

А(2,3): 11,

А(4): 1,

А(5.6) - определяет область зоны:

А(5.6): 00 - 8/2 Мегаслово,

А(5,6): 01 - 3/5 Мегзслово,

А(5,6): 10 - 6/8 Мегаслово,

А(7,6,9): - 000.

Блок 12 перекодировки адреса (фиг. 2,3) работает следующим образом. Элементы И 58.1, 58.2, 58.6, 58.9. 58.11, 58.15. 58.20, 58.22, 58.25 первой группы элементов И 58 работают только в режимах работы предлагаемого устройства некорректируемой ошибки (вход 19.4 блока 13), когда осуществляется съем логаута контролируемого ЗУ (без блока оперативной памяти) и чтение буфера 15 диагностической информации (вход 19.5 блока 13). Временная диаграмма работы предлагаемого устройства совместно с контролируемым ЗУ построена таким образом, что одновременная работа по корректируемым ошибкам, некорректируемым ошибкам и чтению буфера 15 исключают друг друга. Остальные элементы И первой группы элементов И 58 работают при формировании корректируемых ошибок.

Пример. Сформировалась корректируемая одиночная ошибка в рабочем режиме по первому разряду третьего Мегаслова. Синдром, выработанный блоком 5, будет соответствовать синдрому, приведенному в таблице на фиг. 5: СО 1. С1 О, С2 О, СЗ 1,С4 1, С5 0, С6 0.

Четыре старших разряда адреса, определяющие информацию на входе предлагаемого устройства, равны 0011 (см. выше адресацию ТЭЗов) и поступают на адресный вход 21 предлагаемого устройства и соответственно на первый адресный вход блока 12. Сигналы синдрома поступают на вход 24 блока 12. На входе 25 блока 12 сформировался сигнал корректируемой одиночной ошибки в рабочем режиме, который проходит через элементы ИЛИ 49, 50, элемент 61.1 первой группы элементов ИЛИ 61 и формируется нулевой разряд адреса ошибки: А(0) 1. Первый разряд адреса ошибки А(1) 0, т.к. на входе элемента ИЛИ 61.2 группы элементов ИЛИ 61 отсутствуют сигналы. Второй разряд адреса ошибки А (2) 0, т.к. на входах элемента ИЛИ 61.3 нет разрешающих сигналов. Дешифратор 41 номера Мегаслова открыт по управляющему входу сигналом с прямого выхода эле- мента ИЛИ 50. На выходе 011 дешифратора 41 формируется сигнал в соответствии с номером Мегаслова на адресном входе 21. Сигнал через элемент ИЛИ 53 поступает на второй вход элемента И 58.7, на первый и третий входы которого подаются сигналы, сформированные на выходе эле- мента И 49 и управляющем выходе

шифратора 45 информационного разряда соответственно. С выхода элемента И 58.7 сигнал проходит через элемент ИЛИ 61.4 и формируется третий разряд адреса ошибки

А(3) 1. Сигналы синдрома СО - Сб поступают по входу 24 на дешифраторы 42, 43, 44, на первые управляющие входы которых подается сигнал с элемента-ИЛИ 49. Дешифратор 42 не работает, т.к. закрыт по второму

0 управляющему входу сигналом синдрома С6 0. Дешифратор 43 открыт сигналом с выхода элемента НЕ 57 по второму управляющему входу и формирует сигнал на выходе 011, который поступает на восьмой вход

5 шифратора 45. На управляющем выходе шифратора 45 появляется сигнал, соответствующий логической 1, на первом, вто- ром и третьем выходах шифратора 45 расшифровывается код 000. Элементы

0 И58, 10, 58.12, 58.16 закрыты, поэтому на выходах элементов ИЛИ 61.5,61.6, 61.7 формируются нули, что соответствует четвертому, пятому и шестому разрядам адреса ошибки: А(4.5,6) 0. Дешифратор 44 рас5 шифровывает позиции 100, но элемент И60.4 третьей группы элементов ИбО закрыт по первому входу с дешифратора 43. Элементы И58, 20, 50.23 также закрыты по третьему входу сигналами синдрома С2 О

0 и СЗ 0. Сигнал синдрома СО 1 поступает на третий вход элемента 58.26, на второй и третий входы которого приходят сигналы с выхода элементов И 49 и управляющего выхода шифратора 45 соответственно. На вто5 ром входе элемента ИЛИ 61 появляется сигнал, а на выходе его формируется девятый разряд адреса ошибки. Получаем А(7,8) 0. А(9) 1. Таким образом сформировался адрес, соответствующий корректируемой

0 одиночной ошибке в первом разряде третьего Мегаслова в рабочем режиме. По данному адресу ошибки в буфер 15 пишется единица.

Адрес ошибки для всех остальных кор5 ректируемых ошибок вырабатывается аналогично и соответствует адресу ошибки, приведенному на фиг. 6.

Блок 13 управления (фиг. 4) предназначен для выработки сигналов (тактов), коор0 динирующих работу блока 12 перекодировки адреса, счетчика 16, блока 15. Блок 13 работает в трех режимах. Первый режим связан с работой по суммарной корректируемой ошибке. Второй режим 5 это режим работы по некорректируемой ошибке (запись логаута). Третий режим работы - это режим чтения буфера диагностической информации.

По сигналу начальной установки, поступающему по входу 19.3 блока 13, усганавливакися в исходное состояние триггеры 76 - 82 через соответствующие им элементы ИЛИ 65, 67. 71, 69, 70, 73, 72, счетчик 86 логаута устанавливается в состояние О.

С приходом сигнала суммарной корректируемой ошибки на управляющий вход 29 регистра 62 сдвига начинает вырабатывать следующие такты:

1такт - триггер 76 устанавливается в состояние единицы и сигнал управления чтением блока 15 через элемент ИЛИ 68 поступает на выход 32 блока 13;

2такт - вырабатывается сигнал управления переписью содержимого блока 15 на счетчик 16 (выход 37 блока 13);

3такт - сбрасывается триггер 76 через элемент ИЛИ 63 и формируется сигнал плюс единица (выход 38 блока 13), по которому к содержимому счетчику 16 добавляется единица.

4такт - триггер 77 устанавливается в состояние единицы и сигнал разрешения приема значения счетчика 16, увеличенного на единицу, выдается на выход 33 блока 13. На селекторе 14 открывается третий информационный вход, подключающий выход счетчика 16;

5такт - вырабатывается сигнал управления записью нового значения счетчика 16 в буфер 15 через элемент ИЛИ 66 (выход 36 блока 13);

6такт - сброс триггера 77 через элемент ИЛИ 67.

Временная диаграмма работы предлагаемого устройства при приеме суммарной корректируемой ошибки приведена на фиг. 7.

С приходом сигнала Чтения диагностической информации на вход 19,5 блока 13 кольцевой регистр 63 сдвига вырабатывает следующие такты:

1такт - через триггер 78 и элемент И 83 на счетчике 85 устанавливается значение О, на выходе счетчика 85 устанавливается нулевой адрес блока 15 (выход 31 блока 13);

2такт - триггер 79 устанавливается в состояние единицы и сигнал управления чтением блока 15 через элемент ИЛИ 68 выдается на выход 32 блока 13;

3такт - вырабатывается сигнал на выходе 20.2 блока 13, сопровождающий дйаТг- ностическую информацию с выхода 18 устройства, поступающую из блока 15 в ко н- тролируемое ЗУ;

4такт - осуществляется сброс триггера 79 через элемент ИЛИ 69;

5такт - триггер 80 устанавливается в состояние единица.

На выходе 35 блока 13 формируется сигнал, который открывает первый информационный вход на селекторе 14 на прохождение сигнала логического

56 такт - через элемент И Л И 66 на выходе

36 блока 13 вырабатывается сигнал управления записью О в блок 15;

7 такт - происходит сброс триггера 80 через элемент ИЛИ 70 и вырабатывается 0 сигнал, по которому к значению счетчика 85 через элемент ИЛИ 74 прибавляется единица.

Далее процесс повторяется с первого

по седьмой такты, за исключением того, что

5 в первом такте уже не происходит записи

О в счетчик 85. Процесс чтения блока 15

продолжается до тех пор, пока не появится

сигнал первого переполнения на выходе

счетчика 85, который через элемент ИЛИ 71

0 устанавливает триггер 78 в состояние О.

Одновременно снимается сигнал чтения

блока 15 (выход 32 блока 13).

Временная диаграмма работы предлагаемого устройства в режиме чтения блока 5 15 диагностической информации приведена на фиг. 9.

С приходом импульсного сигнала некорректируемой ошибки на вход 19.4 триг- гер 81 устанавливается в состояние 0 единицы, кольцевой регистр 64 сдвига начинает вырабатывать такты.

1такт - триггер 82 устанавливается в состояние единица, а на выходе 34 блока 13 вырабатывается сигнал управления при5 емом логаута (открывается вход селектора 14 по приему логаута, поступающего по информационному входу 17 устройства;

2такт - вырабатывается сигнал управления записью логаута, считанного из конт0 ролируемого ЗУ в блоке 15 через элемент ИЛИ 66 (выход 36 блока 13);

3такт - осуществляется сброс триггера 82 через элемент ИЛИ 72 и вырабатывается сигнал, по которому к значению счетчика 85

5 через элементы ИЛИ 74 и к значению счетчика 86 прибавляется единица, и следовательно, адрес ошибки (выход 30 блока 12) и адрес логаута (выход 22 блока 13) увеличиваются на единицу,

0 Далее процесс продолжается, кольцевой регистр 64 сдвига продолжает вырабатывать такты до тех пор, пока на выходе 86 не появится сигнал переполнения. Сигнал с выхода переполнения счетчика 86 через

5 элемент ИЛИ 73 устанавливает триггер 81 в состояние О. Режим записи логаута закончен.

Временная диаграмма записи логаута приведена на фиг. 8. Блок 15 может принимать четыре логаута-информацию о состоянии контролируемого ЗУ (без блока оперативной памяти). После приема четвертого логаута на выходе счетчика 85 появляется сигнал второго переполнения, по которому через элементы И 84, ИЛИ 75 и выход 20.1 блока 13 выдается сигнал конец работы.

Блок 15, предназначенный для хранения диагностической информации, состоит из следующих зон (фиг. 5).

Зона хранения логаутов, записанных при появлении некорректируемой ошибки, Зона содержит четыре логаута.

Зона хранения содержимого счетчиков одиночных ошибок, корректируемых по коду Хэмминта и возникающих во время выполнения программ пользователя, т.е. в рабочем режиме (КОШ 1р)

Зона хранения содержимого счетчика двойных ошибок, корректируемых по коду Хэмминга и возникающих в рабочем режиме (КОШ2р).

Зона хранения содержимого счетчика одиночных ошибок, корректируемых по коду Хэмминга и возникающих в режиме сканирования (КОШ 1ск);

Зона хранения содержимого счетчика двойных ошибок, корректируемых по коду Хэмминга и возникающих в режиме сканирования (КОШ2ск).

Блок 16 диагностической информации может быть выполнен в виде групп элементов памяти (блока регистров).

Устройство для диагностирования ЗУ (фиг. 1) по корректируемым ошибкам работает следующим образом.

Блок управления оперативной памятью контролируемого ЗУ (БУОП) вырабатывает адрес, поступающий на вход 21 предлагаемого устройства, по которому из блока оперативной памяти (БОП) контролируемого ЗУ выдается информация на вход 17 предлагаемого устройства. БУОП затем выдает сигналы Рабочий режим на вход 19.1 или Режим сканирования на вход 19.2 и сигнал управления на вход 19.6 устройства.

По сигналу управления осуществляется запись кода Хэмминга в регистр 1, а информация через первую группу элементов Л 3 поступает на вход генератора 4 кода Хэмминга. Генератор 4 вырабатывает код Хэмминга, запоминаемый в регистре 2. В блоке 5 обнаружения неисправностей производится сравнение контрольного кода Хэмминга, записанного из БОП контролируемого ЗУ в регистр 1, с кодом, выработанным генератором 4 и записанным в регистр 2. С выхода блока 5 сигналы, Сформированные с помощью элементов 7, 8, 9 сверток и элемента И-НЕ 10, поступают на третий и второй входы дешифратора 6

соответственно, на первый вход дешифратора подается сигнал логического О. Если обнаружена ошибка, на выходе 100 дешифратора 6 вырабатывается сигнал корректируемой одиночной ошибки или корректируемой двойной ошибки на выходе 010, который с помощью второй группы элементов И 11 умножается на сигнал Рабочий режим или Режим сканирования,

0 поступающий в блок 12 с входов 19.1 и 19.2 устройства соответствен но. На выходах 25- 28 формируются сигналы корректируемой одиночной ошибки в рабочем режиме или корректируемой двойной ошибки в рабочем

5 режиме, или корректируемой одиночной ошибки в режиме сканирования, или корректируемой двойной ошибки в режиме сканирования соответственно. Одновременно может быть только одна из перечисленных

0 ошибок. С выхода 29 блока 12 данная ошибка в виде суммарной корректированной ошибки поступает в блок 13 управления. Временная диаграмма сигналов, поступающих из БУОП контролируемого ЗУ, и выра5 ботки суммарной корректированной ошибки приведена на фиг. 10.

С приходом одного из сигналов корректируемой ошибки на вход 25, 27, 26, 28 четырех старших разрядов адреса, на вход 21

0 из БУОП контролируемого ЗУ и сигналов синдрома на вход 24 блока 12 перекодировки адреса ошибки на выходах 30 и 29 блока 12 устанавливается адрес ошибки, в соответствии с таблицей приведенной на фиг. 6,

5 и сигнал суммарной корректируемой ошибки. Адрес ошибки поступает на вход адреса ошибки блока 15. Сигнал суммарной корректируемой ошибки поступает на одноименный вход блока 13. Блок 13 управления

0 вырабатывает такты, по которым выдаются управляющие сигналы в соответствии с временной диаграммой, представленной на фиг. 7, По этим управляющим сигналам происходит чтение блока 15, перепись инфор5 мации, считанной из буфера 15, на счетчик 16 по адресу ошибки, установленному на входе 30 блока 15, значение счетчика 16 корректируемых ошибок увеличивается на единицу, открывается селектор 14 на прием

0 нового значения со счетчика 16 и запись по тому же адресу ошибки нового значения со счетчика 16. Таким образом, фиксируется каждая новая корректируемая ошибка по своему адресу ошибки на входе

5 30 блока 15.

При переполнении счетчика 16 вырабатывается сигнал переполнения, который поступает на вход 39 блока 13 и затем выдается через элемент И 75 на выход 20.1 блока 13 в виде сигнала Конец работы в

блок управления канальными операциями (БУКО) контролируемого ЗУ.

По некорректируемым ошибкам предлагаемое устройство работает следующим образом Сигнал некорректируемой ошибки поступает на вход 19.4 блока 13 из контролируемого ЗУ. Блок 13 начинает вырабатывать такты, по которым выдаются управляющие сигналы в соответствии с временной диаграммой, представленной на фиг. 9. По этим управляющим сигнала тбсу- ществляется1 управление приемом информации логаута, поступающей по информационному входу 17 из контролируемого ЗУ на селектор 14, запись информации в блок 15, увеличение на единицу значений адреса ошибки на выходе счетчика 85 и адреса логаута на выходе счетчика 86 блока 13 соответственно и увеличения адреса ошибки на входе 30 блока 15 и адреса логаута на выходе 22 устройства. Адрес логаута с выхода 22 устройства поступает в контролируемое ЗУ, где формируется новый логаут, соответствующий данному адресу. Адрес ошибки А(0) - А(9) на выходе 30 блока 12 в данном случае формируется следующим образом: с выхода счетчика 85 блока 13 по второму адресному выходу 31 адрес поступает на второй адресный вход блока 12, где происходит через элементы И 58.1, 58.2, 58.3, 58.6, 58.9 58.11, 58.15, 5819, 58,22, 58.25 первой группы элементов И58 и элементы ИЛИ 61.1 - 61.10 группы элементов ИЛИ 61 и далее на выход 30 блока 12.

После увеличения адреса ошибки и адреса логаута на единицу производится запись новой информации в блок 15 по новому адресу ошибки. Процесс записи в блок 15 логаута продолжается до тех пор, пока не произойдет переполнения счетчика 86 логаута, а следовательно, его обнуления и сброса сигнала некорректруемой ошибки на выходе триггера 81 блока 13 Счетчик 86 готов к приему следующего логаута. Блок 15 может принимать четыре логаута. В конце приема четвертого логаута счетчик 85 выдает сигнал второго переполнения, который проходит через элементы И 84, ИЛИ 75. На выходе элемента ИЛИ 75 формируется сигнал Конец работы, который по выходу 20.1 блока 13 передается в БУКО контролируемого ЗУ,

В ответ на сигнал Конец работы, выработанный в режиме работы по корректируемой ошибке или в режиме работы по некорректируемой ошибке контролируемого ЗУ, БУКО вырабатывает сигнал Чтение буфера диагностической информации, поступающий на вход 19.5 блока 13. Адрес ошибки на выходе 30 блока 12 формируется

на выходе счетчика 85 аналогично работе по некорректируемым ошибкам. Блок 13 формирует такты, по которым вырабатываются управляющие сигналы в соответствии с вре- 5 менной диаграммой, представленной на фиг. 8. По этим управляющим сигналам осуществляется: установка счетчика 85 блока 13, а следовательно, и адреса ошибки на выходе 30 блока 12 в нулевое состояние,

0 чтение диагностической информации из блока 15 через информационный выход 18 устройства в БУКО контролируемого ЗУ, формирование сигнала сопровождения этой информации из блока 15. запись нуле5 вой информации на место прочитанной информации, увеличение значения счетчика 85 блока 13, а следовательно, и адреса ошибки на выходе 30 блока 12, Далее процесс продолжается до тех пор, пока счетчик 85 не

0 выработает сигнал первое переполнение, т.е. пока не пропитается весь блок 15 диаг- ностической информации и не заполнится нулями. Блок 15 готов к приему следующих ошибок.

5 Технико-экономические преимущества предлагаемого устройства по сравнению с прототипом заключается в том, что введение трех сверток, элемента И-НЕ двух групп элементов И, блока перекодировки адреса,

0 селектора, счетчика блока буферной памяти и блока управления с новой организацией связей позволяет расширить функциональные возможности ycYpoйcтвa за счет локализации отказов и предотказного состояния

5 блока оперативной памяти и оборудования контролируемого ЗУ по результатам его работы, зафиксированным в буфере диагностической информации в процессе функционирования ЭВМ на пользователь0 ских программах, т.е. позволяет переводить информацию об ошибке в конструктивный адрес ТЭЗ. Это позволяет, в свою очередь, сократить время, затрачиваемое на регулярное техническое обслуживание и локализа5 цию отказов блока оперативной памяти и оборудования контролируемого ЗУ, а также за счет своевременной локализации предо- дказных состояний контролируемого ЗУ повысить его надежность. Кроме того,

0 использование предлагаемого устройства позволяет за счет простоты процедуры локализации отказов и особенно предо- тказных состояний снизить требования к квалификации обслуживающего пер5 сонала.

Формула изобретения 1. Устройство для диагностирования оперативной памяти, содержащее два регистра, первую группу элементов И. генератор кода Хэмминга, блок обнаружения неислравностей и дешифратор, причем информационные входы первого регистра соединены с первыми входами элементов И первой группы и являются информационными входами устройства, управляющий вход первого регистра соединен с вторыми входами элементов И первой группы и является управляющим входом устройства, выходы первого и второго регистров соединены соответственно с первым и вторым информационными входами блока обнаружения неисправностей, выход элементов И первой группы - с входом генератора кода Хэммин- га, выход которого подключен к информационному входу второго регистра, вход синхронизации которого и вход синхронизации первого регистра объединены и являются входом синхронизации устройства, отличаю щ ееся тем, что, с целью расширения области применения устройства за счет регистрации, накопления и локализации корректируемых и некорректируемых ошибок, в него введены три элемента свертки по модулю два, элемент И-НЕ, вторая группа элементов И, блок перекодировки адреса ошибки, блок управления, селектор, блок буферной памяти и счетчик, причем управляющий вход первого регистра соединен с управляющим входом второго регистра, инверсные выходы блока обнаружения неисправностей подключены соответственно к входу элемента И-НЕ и входу первого элемента свертки по модулю два, прямой выход блока обнаружения неисправностей соединен с входом второго элемента свертки по модулю два и входом признака синдрома блока перекодировки адреса ошибки, выходы первого и второго элементов свертки по модулю два соединены с соответствующими входами третьего элемента светки по модулю два, выход которого соединен с третьим входом дешифратора, второй выход которого соединен с выходом элемента И-НЕ, а первый вход является входом логического О устройства, первый выход дешифратора соединен с первыми входами первого и второго элементов И второй группы, первые входы третьего и четвертбго элементов которой соединены с вторым входом дешифратора, вторые входы первого и третьего элементов И второй группы объединены и являются входом сигнала Рабочий режим устройства, вторые входы второго и четвертого элементов И второй группы объединены и являются входом сигнала Режим сканирования устройства, выходы элементов И второй группы соединены с соответствующими управляющими входами блока перекодировки адреса ошибки, первый адресный вход которого является адресным входом устройства, входы синхронизации блока перекодировки адреса ошибки, счетчика и блока управления подключены к входу синхронизации устройства, первый и второй выходы блока переко- дировки адреса ошибки соединены соответственно с входом суммарной корректируемой ошибки блока управления и входом адреса ошибки блока буферной па0 мята, входы н$чальной установки, некорректируемой ошибки и чтения диагностической информации блока управления являются одноименными входами устройства, первый и второй выходы блока

5 управления являются соответственно выходами сигналов Конец работы и Сопровождение информации устройства, адресным выходом которого является третий выход -блока управления, выходы с чет0 вертого по одиннадцатый которого соединены соответственно с вторым адресным входом блока перекодировки адреса ошибки, входом управления чтением блока буферной памяти, входом управления при5 емом корректируемых ошибок, входом управления приемом информации о состоянии контролируемой памяти и входом управления записью нулей устройства, входом управления записью блока буфер0 ной памяти, входом управления перезаписью и счетным входом счетчика, вход логического О блока управления подключен к соответствующему входу устройства, первый и второй информационные входы

5 селектора подключены соответственно к входу логического О и информационным входам устройства, третий информационный вход селектора соединен с выходом счетчика, выход переполнения которого со0 единен с соответствующим входом блока управления, выход селектора - с информационным входом блока буферной памяти, выход которого соединен с информационным входом счетчика и является одноимен5 ным выходом устройстйа.

. Устройство по п. 1, о т л и ч а ю- щ е е с я тем, что блок перекодировки адреса ошибки содержит дешифратор номера мегаслова, три деформатора синдрома,

0 шифратор информационных разрядов, шифратор контрольных разрядов, семь элементов ИЛИ, два элемента И, два элемента НЕ, три группы элементов И, группу элементов ИЛИ, причем первые входы первого и

5 второго элементов ИЛИ объединены и являются четвертым управляющим входом блока, второй вход первого элемента ИЛИ и первый вход третьего элемента ИЛИ объединены и являются вторым управляющим входом блока, вторые входы второго и третьего элементов ИЛИ являются соответственно третьим и первым управляющими входами блока, первые входы первого, второго, третьего, шестого, девятого, одиннадцатого, пятнадцатого, девятнадцатого, двадцать второго и двадцать пятого элементов И первой группы соединены с вторым адресным входом блока, первые входы четвертого, пятого, седьмого, восьмого, десятого, двенадцатого, тринадцатого, шестнадцатого, семнадцатого, двадцатого, двадцать первого, двадцать третьего, двадцать четвертого, двадцать шестого и двадцать седьмого эле- ментов И первой группы соединены с выходом третьего элемента ИЛ И, первым входом четвертого элемента ИЛИ, первыми управляющими входами первого и второго дешифраторов синдрома и управляющим входом третьего дешифратора синдрома, выход второго элемента ИЛИ соединен с вторым входом четвертого элемента ИЛИ, первыми входами четырнадцатого и восемнадцатого элементов И первой группы элементов И, первыми входами третьего, четвертого и пятого элементов ИЛИ группы элементов ИЛИ, выходы первого и второго элементов И первой группы элементов И соединены с первыми входами первого и второго элементов ИЛИ группы элементов ИЛИ соответственно, прямой выход четвертого элемента ИЛИ - с вторым входом первого элемента ИЛИ группы, управляющим входом дешифратора номера мегаслова и выходом суммарной корректируемой ошибки блока, выход первого элемента ИЛИ подключен к второму входу второго элемента ИЛИ группы, инверсный выход четвертого элемента ИЛИ соединен с вторыми входами первого, второго, третьего, шестого, девятого, одиннадцатого, пятнадцатого, девятнадцатого, двадцать второго и двадцати пятого элемента И первой группы, нулевой разряд первого адресного входа блока соединен с входом первого элемента НЕ и первым входом первого элемента И, выход которого подключен к первому входу пятого элемента ИЛИ, а второй вход соединен с первым входом второго элемента И и первым выходом дешифратора номера мегаслова, выходы с второго по седьмой которого соединены с вторым и третьим входами пятого элемента ИЛИ, первым и вторым входами шестого элемента ИЛИ, гтервым, вторым и третьим входами седьмого элемента ИЛ И соответственно, первый, второй и третий разряды первого адресного входа блока соединены с одноименными информационными входами дешифратора номера мегаслова соответственно, выход первого элемента НЕ соединен с вторым входом второго элемента И, выход которого подключен к третьему входу шестого элемента ИЛИ, четвертый вход которого соединен с выходом седьмого элемента ИЛИ и вторыми входами седьмо- 5 го, семнадцатого и восемнадцатого элементов И первой группы элементов И, выход пятого элемента ИЛИ соединен с пятым входом шестого элемента ИЛИ и вторыми входами четвертого, тринадцатого и

0 четырнадцатого элементов И первой группы, выход шестого элемента ИЛИ соединен с вторыми входами пятого и восьмого элементов И первой группы элементов И, управляющий вход шестого элемента ИЛИ

5 соединен с третьими входами пятого, восьмого, тринадцатого, семнадцатого и вторыми входами двадцать первого, двадцать четвертого и двадцать седьмого элементов И первой группы, с управляющим выходом

0 шифратора контрольных разрядов, выходы третьего, четвертого и пятого элементов и первой группы И соединены с вторым, третьим и четвертым входами третьего элемента ИЛИ группы, выходы шестого, седь5 мого и восьмого элементов И первой группы соединены с вторым, третьим и четвертым входами четвертого элемента ИЛИ группы, выходы девятого и десятого элементов И первой группы соединены с вторым и треть0 им входами пятого элемента ИЛИ, выходы с одиннадцатого по двадцать седьмой элементов И первой группы соединены с первым - четвертым входами шестого элемента ИЛИ, с первым - четвертым входами седь5 мого элемента ИЛИ, с первым, вторым и

третьим входами восьмого элемента ИЛИ, с

первым, вторым и третьим входами дебято- го элемента ИЛИ и с первым, вторым и третьим входами десятого элемента ИЛИ

0 группы соответственно, выходы с первого по десятый элементов ИЛИ группы подключены к выходу адреса ошибки блока, синхронизирующий вход блока соединен с входами синхронизации шифратора инфор5 мационных разрядов и шифратора контрольных разрядов, управляющий выход шифратора информационных разрядов соединен с третьими входами четвертого и седьмого элементов И первой группы и вто0 рыми входами десятого, двенадцатого, шестнадцатого, двадцатого, двадцать третьего и двадцать шестого элементов И первой группы, первый, второй и третий информационные выходы шифратора информацион5 ных разрядов подключены к третьим входам десятого, двадцатого и шестнадцатого элементов И первой группы соответственно, нулевой разряд входа признака синдрома блока соединен с первым информационным входом третьего дешифратора синдрома и

А

третьим входом двадцать шестого элемента И первой группы И, первый разряд входа признака синдрома блока соединен с вторым информационным входом третьего дешифратора синдрома и третьим входом двадцать третьего элемента И первой группы, второй разряд входа признака синдрома блока соединен с третьим информационным входом третьего дешифратора синдрома и третьим входом двадцатого элемента И первой группы, третий, четвертый и пятый разряды входа признака синдрома блока подключены соответственно к первым, вторым и третьим информаци- онным входам первого и второго дешифраторов синдрома, шестой разряд входа признака синдрома - с входом второго элемента НЕ и вторым управляющим входом первого дешифратора синдрома, выход второго элемента НЕ соединен с вторым управляющим входом второго дешифратора синдрома, с первого по седьмой выходы первого дешифратора синдрома соединены с одноименными информационными входами шифратора информационных разрядов, восьмой информационный вход которого подключен к первому выходу второго дешифратора синдрома, восьмой выход первого дешифратора синдрома - с первым входом первого элемента И второй группы, с второго по четвертый выходы второго дешифратора синдрома подключены к первым входам соответственно второго, третьего и четвертого элементов И второй группы элементов И, пятый выход второго дешифратора синдрома соединен с первыми входами элементов И и третьей группы элементов И, первый выход третьего дешифратора синдрома соединен с вторым входом первого элемента И третьей группы и вторыми входами элементов И второй группы, вторые входы второго, третьего и четвертого элементов И третьей группы соединены с второго но червертый выходами третьего дешифратора синдрома, выходы элементов И второй и третьей групп элементов И соединены с первого по восьмой информационными входами шифратора контрольных разрядов соответственно, первый, второй и третий информационные выходы шифратора контрольных разрядов подключены к третьим входам соответственно двадцать первого, двадцать четвертого и двадцать седьмого элементов И первой группы элементов И.

3. Устройство по п. 1,отличаю щее- с я тем, что блок управления содержит три регистра сдвига, одиннадцать элементов ИЛИ, семь триггеров, два элемента И, счетчик диагностики и счетчик состояния.причем управляющий вход nepsoio регистра сдвига является входом суммарной корректируемой ошибки блока, первый выход первого регистра сдвига соединен с

информационным входом первого триггера, второй выход является седьмым выходом блока, третий выход соединен с первым входом первого элемента ИЛИ и является восьмым выходом блока, а четвертый, пятый и

Q шестой выходы первого регистра сдвига подключены к информационному входу второго триггера1, первому входу второго элемента ИЛИ и первому входу третьего элемента ИЛИ соответственно, выходы пер5 вого и третьего элементов ИЛ И соединены с входами сброса первого и второго триггеров соответственно, прямой выход первого триггера соединен с первым входом четвертого элемента ИЛИ, прямой выход второго

Q триггера является третьим выходом блока, вход начальной установки блока соединен с вторыми входами первого и третьего элементов ИЛИ, первыми входами пятого - девятого элементов ИЛИ, входом начальной

5 установки счетчика состояния, входы синхронизации с первого по седьмой триггеров, с первого по третий регистров сдвига, счетчика диагностики, счетчика состояния подключены к входу синхронизации блока,

Q информационный вход второго регистра сдвига является входом Чтение диагностической информации блока, первый выход второго регистра сдвига соединен с информационным входом третьего триггера и пер5 вым входом первого элемента И, второй - шестой выходы соединены с информационным входом четвертого триггера, выходом Сопровождение информации блока, вторым входом пятого элемента ИЛИ, инфорQ мационным входом пятого триггера и вторым входом второго элемента ИЛИ соответственно, а седьмой выход второго регистра сдвига соединен с вторым входом шестою элемента ИЛИ и первым входом

5 десятого элемента ИЛИ, входы сброса третьего, четвертого и пятого триггеров соединены с выходами седьмого, пятого и шестого элементов ИЛИ, инверсный выход третьего триггера, прямые выходы четвер0 того и пятого триггеров соединены с вторым входом первого элемента И, вторым входом четвертого элемента ИЛИ и пятым выходом блока, входы установки О счетчика диагностики и счетчика состояния подключены к

е входу логического О блока, первый и второй управляющие входы счетчика диагностики соединены с выходами первого элемента И и выходом десятого элемента ИЛИ, первый и второй выходы переполнения и второй адресный выход счетчика диагностики соединены с вторым входом седьмого элемента ИЛИ, первым входом второго элемента И и первым выходом блока, выход переполнения счетчика состояния соединен с вторым входом девятого элемента ИЛИ, выход которого подключен к входу сброса шестого триггера, установочный вход шестого триггера является входом некорректируемой ошибки блока, а выход соединен с информационным входом третьего регистра сдвига и вторым входом второго элемента И. выход которою подключен к первому входу одиннадцатого элемента ИЛИ, второй вход и выход которого соединены с входом

17

переполнения блока и выходом сигнала Конец работы блока, первый и второй выходы третьего регистра сдвига соединены с информационным входом седьмого триггера и вторым входом второго элемента ИЛИ соответственно, а третий выход - с вторыми входами восьмого и десятого элементов ИЛИ и управляющим входом счетчика состояния, вход сброса и выход седьмого триггера соединены с выходом восьмого элемента ИЛИ и четвертым выходом блока соответственно, выходы второго и четвертого элементов ИЛИ подключены к шестому и второму выходам блока соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Устройство для обнаружения и коррекции ошибок | 1990 |

|

SU1783583A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

Изобретение относится к области вычислительной техники и может быть исполь- зовано в устройствах контроля и диагностирования запоминающих устройств. Целью изобретения является расширение области применения устройства за счет регистрации, накопления и локализации корректируемых и некорректируемых ошибок. Поставленная цель достигается тем, что в устройство для диагностирования запоминающего устройства, содержащее два регистра, первую группу элементов И, генератор кода Хэмминга, блок обнаружения неисправностей и дешифратор, введены три элемента свертки, элемент И-НЕ, вторая группа элементов И, блок перекодировки адреса ошибки, блок управления, селектор, блок буферной камеры, счетчик ошибок с новой организацией связей. Это позволяет локализовать отказы и предо- тказные состояния блока оперативной памяти и оборудования контролируемого ЗУ по результатам его работы, зафиксированные в блоке буферной памяти в процессе функционирования ЭВМ. 2 з.п. ф-лы, 10 ил. (/) С

Б1

I Щ I ь

- ҐMJL

ег

юг

к

Zfcossa

Ста

4

-0 /

Сэ

О «О

Гч

Ч

v -

п 0|

I - cvi гО -чг Л Л JC I О Со О О О О О

0 о

Фиг 6

85

f -- lM CkQл. ъ W

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля оперативной памяти | 1977 |

|

SU720515A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-12-30—Публикация

1990-08-02—Подача