с первьол входом пятого триггера, с ; третьим входом счетчика импульсов, с управляю14им входом первого регистра;, и с выходом первого элемента 2И-ИЛИ, третий вход которого подключен к первому выходу второго триггера, четвертый вход - к первому входу третьего; элемента ИЛИ и к выходу второго элемента совпадения, второй вход которого подключен к выходу первой линии задержки и к входу второй линии за- . держки, выход которой соединен с первым входом третьего элемента совпадения, выход которого соединен с вторыми входами третьего элемента ИЛИ и четвертого триггера, а второй вход третьего элемента совпадения.- с вторым выходом третьего триггера, с вторым входом блока уставок и с первым входом второго элемента 2И-ИШ, выход которого подключен к входу таймера и к второму входу пятого триггера, первый выход которого соединен с IBTO{жхм входом втррюго элемента 2И-ИЛИ,

третий вход которого соединен с вторым выходом пятого триггера и с управяющим входом второго ключа, четвертый вход - с входом первой линии задержки и с выходом четвертого элемента совпадения, первый вход которого соединен с выходом первого элемента ИЛИ и с пятым входом второго элемента 2И-ИЛИ, второй вход - с первым выходом пятого триггера, а третий вход - с третьим входом второго триггера и с выходом шестого триггера, вход которого подключен к выходу Первого блока сравнения, при этом выход блока уставки соединен с вторым входом блока деления, причем первый выход первого триггереь соединен с управляющим- входом обратного счета реверсивного счетчика импульсов, управляющий вход прямого счета которого подключен к второму выходу первого триггера, а выход - к информационному входу второго регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1095387A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU911721A1 |

| Устройство для определения объемного расхода жидкости | 1989 |

|

SU1723440A1 |

| Устройство для исследования пульсовой динамики сердечно-сосудистой системы | 1987 |

|

SU1512561A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2017 |

|

RU2671545C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| Способ гашения дуги однофазного замыкания на землю в сети переменного тока | 1986 |

|

SU1376169A1 |

| Устройство для дистанционногоизМЕНЕНия ВыХОдНОгО НАпРяжЕНиядЕКОдиРующЕгО пРЕОбРАзОВАТЕля | 1978 |

|

SU845257A1 |

| Устройство для тестового контроля временных соотношений | 1987 |

|

SU1596337A1 |

АДАПТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий первый и второй блоки сравнения, первые входы которых соединены между собой, вторые входы - с первой и второй шинами напряжения сравнения соответственно, первый триггер и первый элемент ИЛИ, первый вход которого соединен с выходом первого блока сравнения и с первым входом первого триггера, второй вход которого подключен к второтлу входу первого элемента ИЛИ и к выходу второго блока сравнения, реверсивный счетчис импульсов, преобразователь код - аналог, второй элемент ИЛИ, генератор импульсов, первый ключ, второй трипер, первую линию задержки, вход которой соединен с первьлм входом второго триггера, первый выход которого подключен к управляющему входу первого ключа, информационный вход которого соединен с выходом генератора импульсов, а выхрд с первым входом второго элемента ИЛИ, выход которого подключен к счетному входу реверсивного счетчика импульсов, выход которого соединен с входом преобразователя код - аналог, первый,второй, третий и четвертый элементы совпадения, таймер, первый и второй регистры, блок деления, блок сравнения кодов, счетчик импульсов и второй ключ, выход которого соединен с вторым входом второго элемента ИЛИ, информационный вход второго ключа подключен к выходу блока сравнения кодов и к первому входу счетчика импульсов, второй вход которого соединен с выходом генератора импульсов , а выход - с первым входом блока сравнения кодов, второй вход которого подключен к выходу блока деления, первый вход которого соединен с выходом первого регистра, информационный вход которого подключен к выходу таймера, вход которого соединен с управляющим входом второго § регистра, отличающийся (Л тем, что, с целью повьшения коэффициента сжатия адаптивного преобразования, в него введены вторая линия задержки, третий элемент ИЛИ, третий, четвертый, пятый и шестой триг-2 геры, блок уставож первый и второй элемент 2 И-ИЛИ, третий блок сравнения и аналоговый блок вычитания, первый вход которого подключен к входной шине, второй вход - к выходу преобразователя код - аналог, а выr-J ход - к Первому входу первого блока 00 Ot) сравнения к к первому входу третьего блока сравнения второй вход которого соединен с общей шиной, а выход - с о Ф первым входом первого элемента совпа дения, вторюй вход которого подключен к второму выходу второго триггера, второй вход которого соединен с выходом третьего элемента ИЛИ и с первым входом третьего триггера, первый выход которого подключен к первому входу второго элемента совпадения и к Первому входу блока уставок, второй вход - к выходу первого элемента совпадения и к первому входу первого элемента 2И-ИЛИ, второй вход которого подключен к выходу четвертого триггера первый вход которого соединен

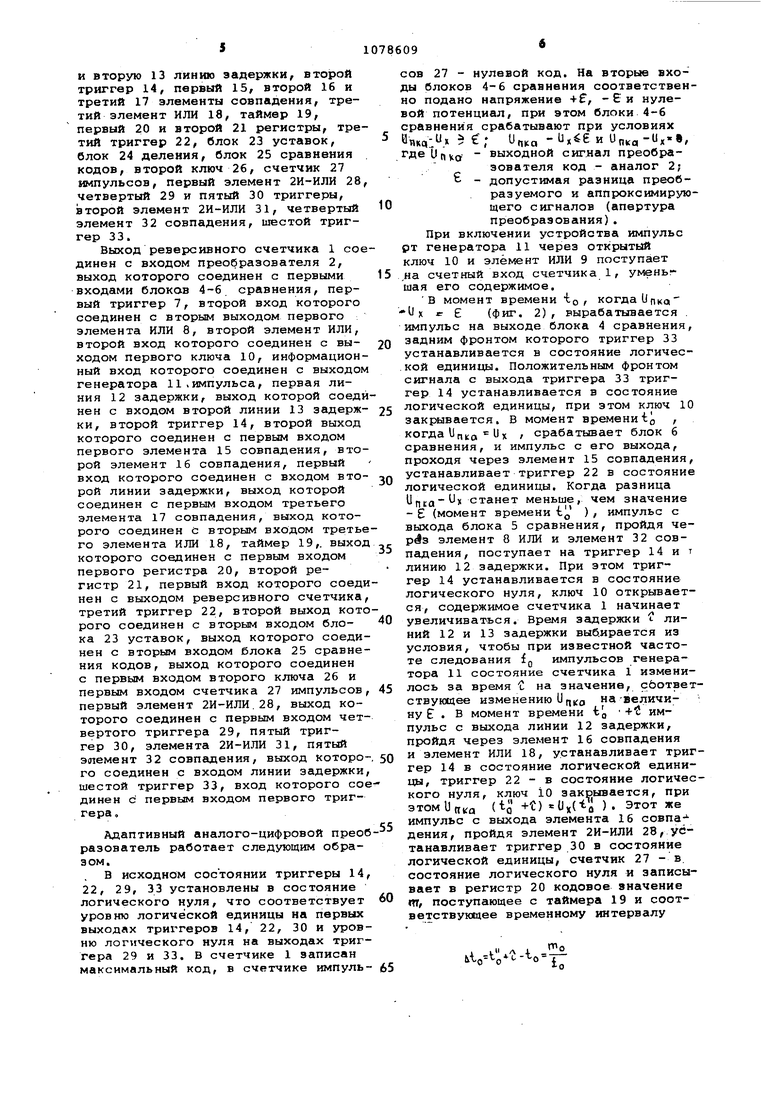

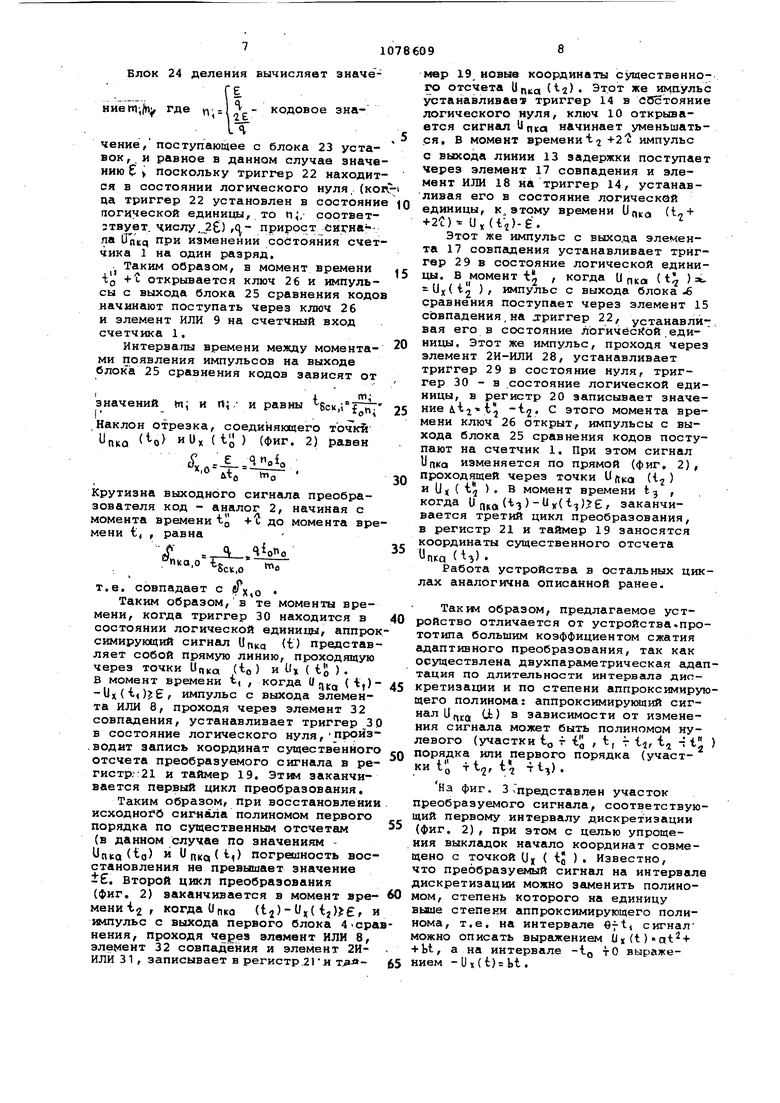

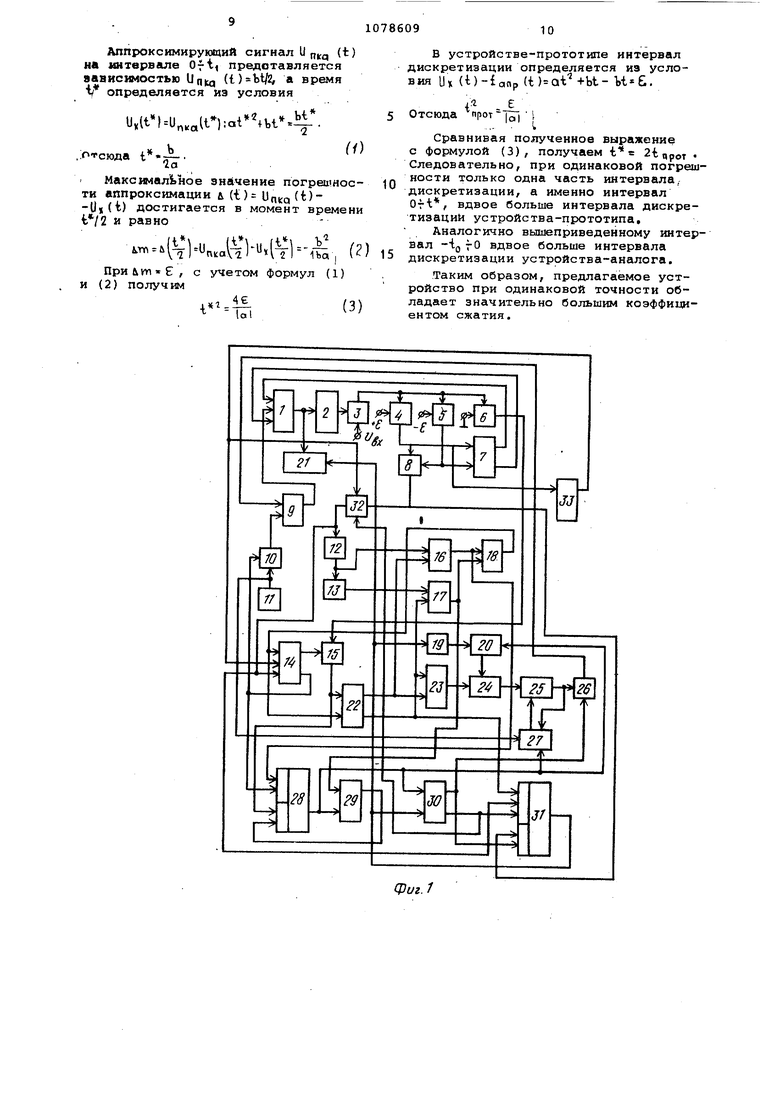

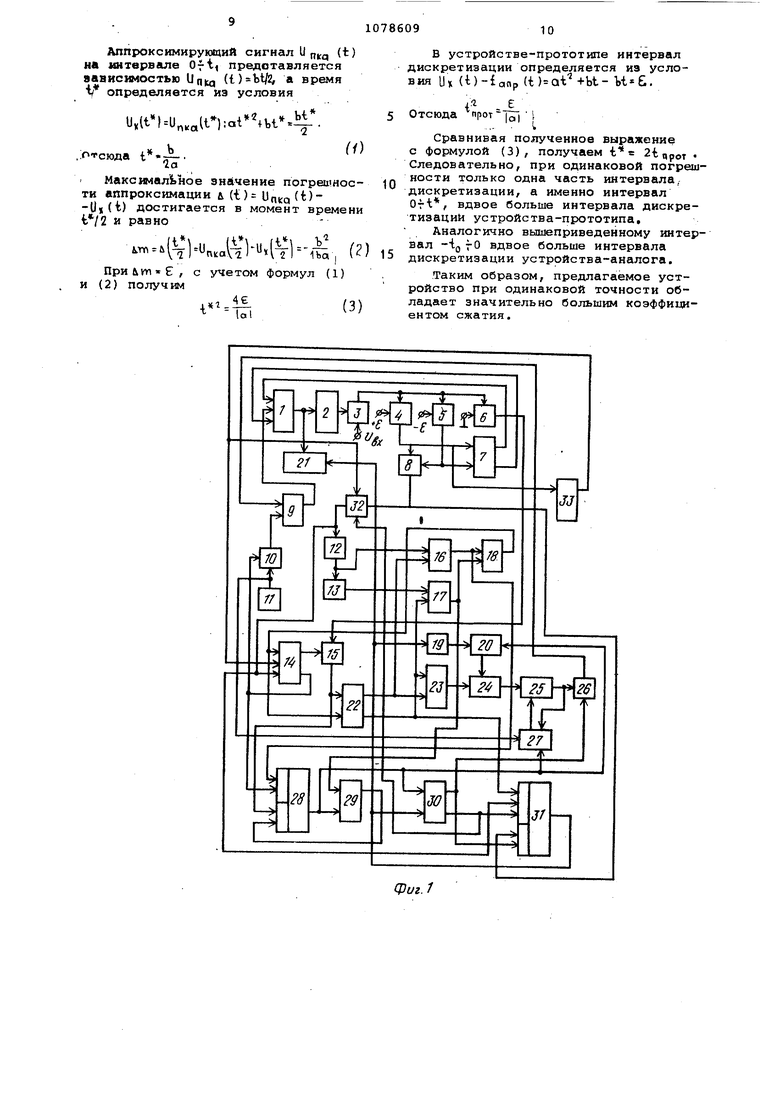

Изобретение относится к цифровой электроизмерительной технике и используется в адаптивных системах сбора и передачи цифровой измерительной информации, Известен гедаптивный аналого-цифровой преобразователь, содержащий И блоков сравнения, блок уставок, д шифратор, элемент ИЛИ и таймер ll . Недостатком устройства является низкая надежность. Наиболее близким к предлагаемому является адаптивный а налого-цифровой преобразователь, содержащий первый и второй блоки сравнения, первые входы которых соединены между собой вторые входы соответственно с первой и второй шинами напряжений сравнения первый триггер и первый элемент ИЛИ первый вход которого соединен с выходом первого блока сравнения и с первым входом первого триггера, второй вход котсзрого подключен к второму входу первого элемента ИЛИ и к выходу второго блока сравнения, реверсивный счетчик импульсов, преобраэователь код - аналог, второй элемент ИЛИ, генератор импульсОв, первый ключ, второй триггер, первую линию задержки, вход которой соединен с первым входом второго триггера, первый выход Которого подключен к управляющему входу первого ключа, информационный вход которого соединен с вь содом генератора импульсов, а выход первого ключа соединен с пер вым входом второго элемента ИЛИ, выход которого подключен к счетному входу реверсивного счетчика импульсов, выход которого соединен с входом преобразователя код - аналог, первый, второй, третий и четвертый элементы совпадения, таймер, первый и второй регистры, блок деления, блок сравнения кодов, счетчик импульсов и второй ключ, выход которого соединен с вторым входом второго элемента ИЛИ, информационный вход второго ключа подключен к выходу блока сравнения кодов и к первому входу счетчика импульсов, второй вход которого соединен с выходом Генератора импульсов, а выход счетчика - с перВ1Л4 входом блока сравнения кодов, второй вход которого подключен к выходу блока деления, первый вход которого соединен с выходом первого регистра, информационный вход которого подключен к выходу таймера, вход которого соединен с управляющим входом второго регистра 2j , Недостаток устройства - низкий коэффициент сжатия адаптивного преобразования. Цель изобретения - повышение коэффициента сжатия адаптивного преобразования путем осуществления двухпараметрической адаптации по длительности интервала дискретизации и по степени аппроксимирующего полинома. Поставленная цель достигается тем, что в адаптивный аналвго-ци1)ровой преобразователь, содержащий первый и второй блоки сравнения, первые входы которых соединены между собой вторые входы - с первой и второй ши ной напряжения сравнения соответственно, первый триггер и первый элемент ИЛИ, первый вход которого соединен с выходом первого блока срав.иения и с первым входом первого три гера, второй вход которого подключе к второму входу первого элемента ИЛИ и к выходу второго блока сравнения, реверсивный счетчик импульсов, прео разователь код - аналог, второй эле мент ИЛИ, генератор импульсов, первый ключ, второй триггер, первую ли нию задержки, вход которой соединен с первым входом второго триггера, первый выход которого подключен к управляющему входу первого ключа, инфррялационный вход которого соедииен с выходом генератора импульсов, а выход - с первым входом второго элемента ИЛИ, выход которого подклю чен к счетному входу реверсивного счетчика импульсов, выход которого соединен с входом преобразователя код - аналог, первый, второй, трети и четвертый элементы совпадения, та мер, первый и второй регистры, блок деления, блок сравнения кодов, счет чик импульсов и второй ключ, выход которого соединен с вторьм входом второго элемента ИЛИ, информационный вход второго ключа подключен к выход блока сравнения кодов и к первому входу счетчика импульсов, второй вхо которого соединен с выходом генератора импульсов, а выход - с первым входом блока сравнения кодов, второй вход которого подключен к выходу бло ка деления, первый вход которого соединен с выходом первого регистра информационный вход которого подключен к выходу таймера, вход которого соединен с управляющим входом второго регистра, введены вторая линия задержки, третий элемент ИЛИ, третий четвертый, пятый и шестой триггеры, блок уставок, первый и второй элементы 2И-ИЛИ, третий блок сравнения и аналоговый блок вычитания, первый вход которого подключен к входной шине, второй вход - к выходу преобразователя код - аналог, а выход - к первому входу первого блока сравнения и к первому выходу третьего блока сравнения, второй вход которого соединен с общей шиной, а выход - с первым входом первого элемента совпадения, второй вход которого подключен к второму выходу второго триг гера, второй вход которого соединен с выходом третьего элемента ИЛИ и с первым входом третьего триггера, пер вый выход которого подключен к первому входу второго элемента совпаде- ния и к первому входу блока уставок, второй вход - с выходом первого элемента совпадения и с первым входом Первого элемента 2И-ИЛИ, второй вход которого подключен к выходу четвертого триггера, первый вход которого соединен с первым входом пятого триггера, с третьим входом счетчика импульсов , с управляющим входом первого регистра и с выходом первого элемента 2И-ИЛИ, третий вход которого подключен к первому выходу второго триггера, четвертый вход - к первому входу третьего элемента ИЛИ и к выходу второго элемента совпадения, второй вход которого подключен к выходу первой линии задержки и к второй линии зашержки, выход которой соединен с первым входом третьего элемента совпадения, выход которого соединен с вторыми входами третьего элемента ИЛИ и четвертого триггера, а второй вход третьего элемента совпадения - с вторым выходом третьего триггера, с вторым входом блока уставок и с первым входом второго элемента 2И-ИЛИ, выход которого подключен к входу таймера и к второму входу пятого триггера, первый выход которого соединен с вторым входом второго элемента 2И-ИЛИ, третий вход которого соединен с вторым выходом пятого триггера и с управляющим входом второго ключа, четвертый вход - с входом первой линии задержки и с выходом четвертого элемента совпадения, первый вход которого соединен с выходом первого элемента ИЛИ и с пятым входом второго элемента 2И-ИЛИ, второй вход - с первым выходом пятого триггера, а третий вход - с третьим входом второго триггера и с выходом шестого триггера, вход которого подключен к выходу первого блока сравнения, при этом выход блока уставок соединен с вторым входом блока деления, причем первый выход первого триггера соединен с управляющим входом обратнсуго счета реверсивного счетчика импульсов, управляющий вход прямого счета которого подключен к второму выходу первого триггера, а выход - к информационному входу второго регистра. I На фиг. 1 приведена функциональная схема адаптивного аналого-цифрового преобразователя; на фиг, 2 и 3 диаг заммы, поясняющие работу устройства. Преобразователь (фиг. 1) содержит реверсивный счетчик 1 импульсов, преобразователь код - аналог 2, аналоговый блок 3 вычитания, первый 4, второй 5 и третий б блоки сравнения, первый триггер 7, первый 8 и второй 9 элементы ИЛИ, первый ключ 10, генератор 11 импульсов, порвую 12 и вторую 13 линию задержки, второй триггер 14, первый 15, второй 16 и третий 17 элементы совпадения, третий элемент ИЛИ 18, таймер 19, первый 20 и второй 21 регистры, тре тий триггер 22, блок 23 уставок, блок 24 деления, блок 25 сравнения кодов, второй ключ 26, счетчик 27 импульсов, первый элемент 2И-ИЛИ 28 четвертый 29 и пятый 30 триггеры, iaторой элемент 2И-ИЛИ 31, четвертый элемент 32 совпадения, шестой триггер 33. Выход реверсивного счетчика 1 сое динен с входом преобразователя 2, выход которого соединен с первыми входами блоков 4-6 сравнения, первый триггер 7, второй вход которого соединен с вторым выходом первого элемента ИЛИ 8, второй элемент ИЛИ, второй вход которого соединен с выходом первого ключа 10, информацион ный вход которого соединен с выходом генератора 11 .импульса, первая линия 12 задержки, выход которой соеди нен с входом второй линии 13 задержки, второй триггер 14, второй выход которого соединен с первым входом первого элемента 15 совпадения, второй элемент 16 совпадения, первый вход которого соединен с входом второй линии задержки, выход которой соединен с первым входом третьего элемента 17 совпадения, выход которого соединен С вторым входом третье го элемента ИЛИ 18, таймер 19,. выход которого соединен с первым входом первого регистра 20, второй регистр 21, первый вход которого соеди нен с выходом реверсивного счетчика третий триггер 22, второй выход кото рого соединен с вторым входом блока 23 уставок, выход которого соединен с вторым входом блока 25 сравнения кодов, выход которого соединен с первым входом второго ключа 26 и первым входом счетчика 27 импульсов первый элемент 2И-ИЛИ.28, выход которого соединен с первым входом четвертого триггера 29, пятый триггер 30, элемента 2И-ИЛИ 31, пятый элемент 32 совпадения, выход которого соединен с входом линии задержки шестой триггер 33, вход которого сое динен с первым входом первого триггера. /Адаптивный аналого-цифровой преоб разователь работает следующим образом. В исходном состоянии триггеры 14 22, 29, 33 установлены в состояние логического нуля, что соответствует уровню логической единицы на первых выходах триггеров 14, 22, 30 и уровню логического нуля на выходах триггера 29 и 33. В счетчике 1 записан максимальный код, в счетчике импульсов 27 - нулевой код. На вторые входы блоков 4-6 сравнения соответственно подано напряжение +С, -Ей нулевой потенциал, при этом блоки 4-6 сравнения срабатывают при условиях йчка:. ; и„,а -и,е и Un,, где ипНо выходной сигдал преобразователя код - аналог 2; t - допустимая разница преобразуемого и аппроксимирующего сигналов (апертура Преобразования). При включении устройства импульс рт генератора 11 через открытый ключ 10 и элемент ИЛИ 9 поступает ,на счетный вход счетчика 1, умеаъгшая его содержимое. В момент времени to, когда Упка х гг (фиг. 2), вырабатывается . импульс на выходе блока 4 сравнения, задним фронтом которого триггер 33 устанавливается в состояние логической единицы. Положительным фронтом сигнала с выхода триггера 33 триггер 14 устанавливается в состояние логической единицы, при этом ключ 10 закрывается. В момент временило , когда 11 / срабатывает блок 6 сравнения, и импульс с его выхода, проходя через элемент 15 совпадения, устанавливает триггер 22 в состояние логической единицы. Когда разница Иnta к меньше, чем значение - (момент времени V ), импульс с выхода блока 5 сравнения, пройдя черйз элемент 8 ИЛИ и элемент 32 совпадения, поступает на триггер 14 и т линию 12 задержки. При этом триггер 14 устанавливается в состояние логического нуля, ключ 10 открывается, содержимое счетчика 1 начинает Время задержки лиув ел ич ив а ть с я, НИИ 12 и 13 задержки выбирается из условия, чтобы при известной частоте следования i импульсов генератора 11 состояние счетчика 1 изменилось за время 1 на значение, сЬответствующее изменению U,g на-величину Е . В момент времени tg +1 импульс с выхода линии 12 задержки, пройдя через элемент 16 совпадения и элемент ИЛИ 18, устанавливает триггер 14 в состояние логической единицы, триггер 22 - в состояние логического нуля, ключ 10 закрывается, при 3TOMl(jv;a (tg H-t) «UxCtfl ). Этот же импульс с выхода элемента 16 coвпaдения, пройдя элемент 2И-ИЛИ 28, устанавливает триггер 30 в состояние логической единицы, счетчик 27 - в. состояние логического нуля и записывает в регистр 20 кодовое значение т, поступающее с таймера 19 и соответствующее временному интервалу vt;.t-t.. Блок 24 деления вычисляет знача...-.. ниет;/ где -.l кодовое значение, поступающее с блока 23 уставок,, и равное в данном случае значе нию V поскольку триггер 22 находит ся в состоянии логического нуля, (KO ца триггер 22 установлен в состояни логической единицы, то соответзтвует. числу.2) ,( прирост сигна-яа ilnKq при изменении сойтояния счет чика 1 на один разряд. Таким образом, в момент времени to +t открывается ключ 26 и импульсы с выхода блока 25 сравнения кодо начинают поступать через ключ 26 и элемент ИЛИ 9 на счетчный вход счетчика 1. Интервалы времени между моментами появления импульсов на выходе блок 51 25 сравнения кодов зависят от 1 т п . и равны бскй значений tn; и Наклон отрезка, соединяющего точки ;to) HUx ( to ) (фиг. 2) равен Крутизна выходного сигнала преобразователя код - аналог 2, начиная с момента времени tg +1 до момента вре мени t, , равна 4iono : -J-Л, т.е. совпадает с РХ,О Таким образом, в те моменты времени, когда триггер 30 находится в состоянии логической единицы, аппро симирующий сигнал Unica (t) представ ляет собой прямую линию, проходящую через точки Untca (о ) и U ( t ) . в момент времени t , когда U j,, (tj) -lx()f импульс с выхода элемента ИЛИ 8, проходя через элемент 32 совпадения, устанавливает триггер 3 в состояние логического нуля,произ .водит запись координат существенног отсчета преобразуемого сигнала в ре гистр,:21 и таймер 19. Этим заканчивается первый цикл преобразования. Таким образом, при восстановлени исходного сигнала полиномом первого порядка по существенным отсчетам (в данном случае по значениям UntQ to) и ) погрешность вос становления не превышает значение t. Второй цикл преобразования (фиг, 2) заканчивается в момент вре мени i , когдаУпко (t2)-Ux(2)€r импульс с выхода первого блока нения, проходя через элемент ИЛИ 8, элемент 32 совпадения и элемент 2ИИЛЙ 31 , записывает в регистр.2Ги т лмер 19 новые координаты существенного отсчета Un«;a (2)- Этот же импульс устанавливает триггер 14 в состояние логического нуля, ключ 10 открывается сигнал Ипка начинает уменьшаться, В момент времени 12 +2 импульс с выхода линии 13 задержки поступает через элемент 17 совпадения и элемент ИЛИ 18 на триггер 14, устанавливая его в состояние логический единицы, к, этому времени (t,,+ +2-0) Ux(t2)-g. Этот же импульс с выхода элемента 17 совпадения устанавливает триггер 29 в состояние логической единицы. В момент tj / когда U пка (t ) аи (i2 )/ импульс с выхода блокад сравнения поступает через элемент 15 совпадения,на триггер 22, устанавлит вая его в состояние логической.единицы. Этот же импульс, проходя через элемент 2И-ИЛИ 28, устанавливает триггер 29 в состояние нуля, триггер 30 - в .состояние логической единицы, в регистр 20 записывает значение С этого момента времени ключ 26 открыт, импульсы с выхода блока 25 сравнения кодов поступают на счетчик 1, При этом сигнал 11пка изменяется по прямой (фиг, 2) , проходящей через точки ( d и U ( t ). В момент времени t , когда и ,)к( заканчивается третий цикл преобразования, в регистр 21 и таймер 19 заносятся координаты существенного отсчета ИПРСО (Ц). Работа устройства в остальных циклах аналогична описанной ранее. Так образом, предлагаемое устройство отличается от устройства прототипа большим коэффициентом сжатия адаптивного преобразования, так как осуществлена двухпараметрическая адаптация по длительности интервала диг;кретизации и по степени аппроксимирующего полинома: аппроксимирукяций сигнал иг,д (jb) в зависимости от изменения сигнала может быть полиномом нулевого (участки to f ig , t, т ti, t -; tj ) порядка или первого порядка (участки t т Ц, t Т t-j) . На фиг. 3 чпредставлен участок преобразуемого сигнала, соответствующий первому интервалу дискретизации (фиг. 2), при этом с целью упрощения выкладок начало координат совмещено с точкой Ux ( 0 ) Известно, что преобразуемый сигнал на интервале дискретизации можно заменить полиномом, степень которого на единицу выше степени аппроксимирующего полинома, т.е. на интервале , сигнал ожно описать выражением Ux(t) + Ы, а на интервале -1 т О выражением -и к (t)ы.

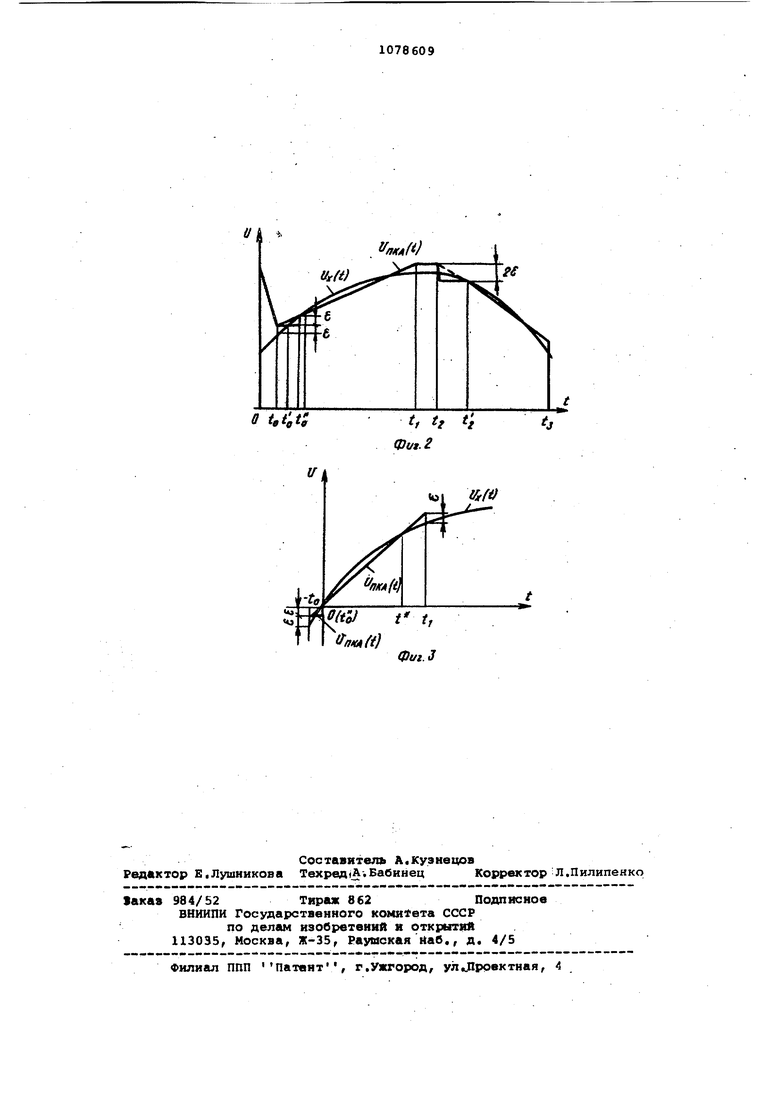

Аппроксимирующий сигнал U Kq () на кнтерваше Oft представляется яависимостью Uni) (i)bi/2, а время V определяется иэ условия

2

,..lt):at

+ Ы

.лтсюда t

1а

Максимальное значение погреиности аппроксимации л () УПКО) -ll)i(t) достигается в момент времени и равно

)-Vafel- №)-ra, (г)

Прилт-Е, с учетом формул (1) и (2) получим

тп(3)

1 кг -:-з t - „I

1а1

в устройстве-прототипе интервал дискретизации определяется из условия и (U-f апр (t)a-t +bt- UE.

Е

i 5 Отсюда прот- |а|

Сравнивая полученное выражение

с формулой (3), получаем t 2i

я рот Следовательно, при одинаковой погрешности только одна часть интервала, дискретизации, а именно интервал Oft, вдвое больше интервала дискретизации устройства-прототипа.

Аналогично вышеприведенному интервал -ifl 7-0 вдвое больше интервала дискретизации устройства-аналога.

.Таким образом, предлагаемое устройство при одинаковой точности обладает значительно большим коэффициентом сжатия.

Oito) t tr

)

Ifffi)

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислителыалх устройств | |||

| М., Энергия, 1975, с | |||

| Мяльно-трепальный станок | 1921 |

|

SU314A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-03-07—Публикация

1982-12-28—Подача