сл

с

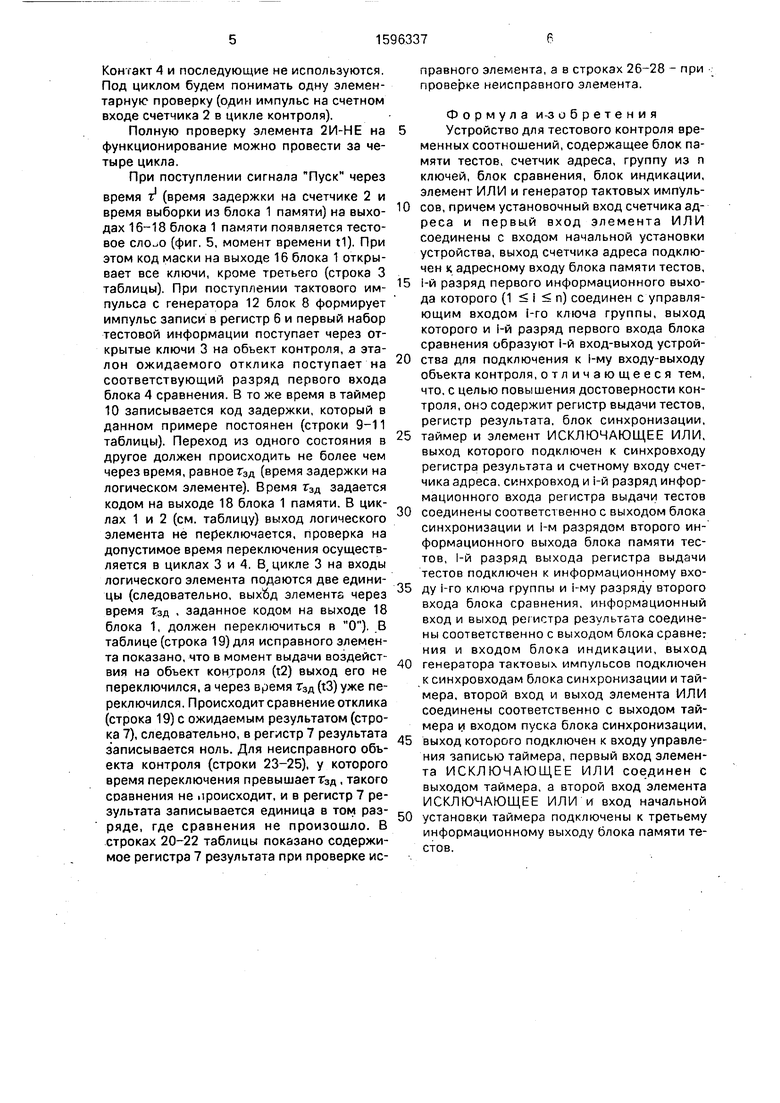

13ЗЛЛ1. Таймер 10 (формирователь временных интервалов) служит для формирования заданного интервала времени, кратного периоду тактовых импульсов, и может быть реализован, например, на микросхемах серии 133. Таймер 10 (фиг. 3) образуют триггер 21, элемент И 22 и счетчик 23.

Блок 11 синхронизации предназначен для формирования импульсов записи и может быть реализован, например, на микросхемах серии 133. Согласно фиг. 4 блок 11 выполнен на триггере 24 и элементе И 25.

Генератор 12 тактовых импульсов генерирует импульсы тактовой частоты и мoжet быть реализован, например, на микросхемах 533ГГ1. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13 служит для работы в качестве управляемого инвертора и может быть реализован, например, на микросхеме 133ЛП5.

Устройство работает следующим образом.

Сигналом Пуск, который поступает на вход 14 счетчика 2, адреса и на вход 15 блока 8, в счетчик 2 адреса заносится адрес первого тестового слова и запускается блок 8. При этом с выхода счетчика 2 адреса на вход блока 1 памяти тестов поступает адрес первого тестового слова и блок 1 выдает первое тестовое слово, которое состоит из трех частей. Каждая часть тестового слова выдается на соответствующий выход блока 1.

Выходы 16 блока 1 управляют работой ключей 3. Ключи 3, которые открываются сигналами с группы выходов 16, пропускают через себя сигналы воздействий, подаваемые на объект контроля. На выходах 17 группы формируются сигналы воздействий и сигналы ожидаемого отклика, а на выходах 18 - код времени задержки. Кроме того, блок 8 через заданный интервал времени (определяемый временем задержки в счетчике 2 адреса и временем выборки из блока 1 памяти) на выходе 19 формирует сигнал записи в регистр 6, который формируется по переднему фронту тактового импульса, поступающего с выхода генератора 12.

По сигналу записи в регистр 6 с выходов 17 блока 1 памяти тестов записываются сигналы воздействий, которые через ключи 3 поступают на объект контроля, а сигналы отклика поступают на вход блока 4 сравнения.. На выходе 20 блока 8 через интервал времени (относительно сигнала записи в регистр 6), определяемый кодом задержки, формируется сигнал записи в регистр 7 результата. По сигналу записи в регистр 7 с выхода блока 4 сравнения записывается результат сравнения. Этот же сигнал подается на счэтный вход счетчика 2, в котором по нему формируется адрес следующего тесто-,

вого слова. Результат сравнения с выхода регистра 7 результата поступает на вход блока 5 индикации. По адресу следующего тестового слова на выходе блока 1 памяти

тестов формируется следующее тестовое слово.

Блок 8 формирования задержки работа-, ет следующим образом. Сигнал, пришедщий на первый или второй вход элемента

0 ИЛИ 9, через этот элемент поступает на вход пуска блока 11 синхронизации. На син- хровход блока 11 синхронизации поступают тактовые импульсы с генератора 12 тактовых импульсов. Блок 11 синхронизации по

5 переднему фронту импульса после фиксации поступления на его вход сигнала пуска формирует сигнал записи в регистр 6. По этому же сигналу в таймер 10 записываются старшие разряды кода интервала времени

0 задержки. Старшие разряды кода интервала времени задержки соответствуют числу периодов тактовых импульсов генератора 12.

Через время, определяемое старшими

5 разрядами кода времени задержки относительно сигнала записи в регистр 6, на выходе таймера 10 формируется сигнал переноса, который поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и

0 на второй вход элемента ИЛИ 9. На второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 поступает младший разряд кода интервала времени задержки. В случае равенства его О на выходе элемента ИСКЛЮЧАЮЩЕЕ

5 ИЛИ 13 формируется прямой сигнал переноса и фиксация момента сравнения (т.е.. запись в регистр 7 результата) происходит по его переднему фронту, а в случае равенства его 1 на выходе злемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 формируется инверсный сигнал переноса и фиксация момента сравнения (т.е. запись в регистр 7) происходит по его заднему фронту, что позволяет уменьшить дискрет задаваемых временных интервалов до половины периода тактовой частоты.

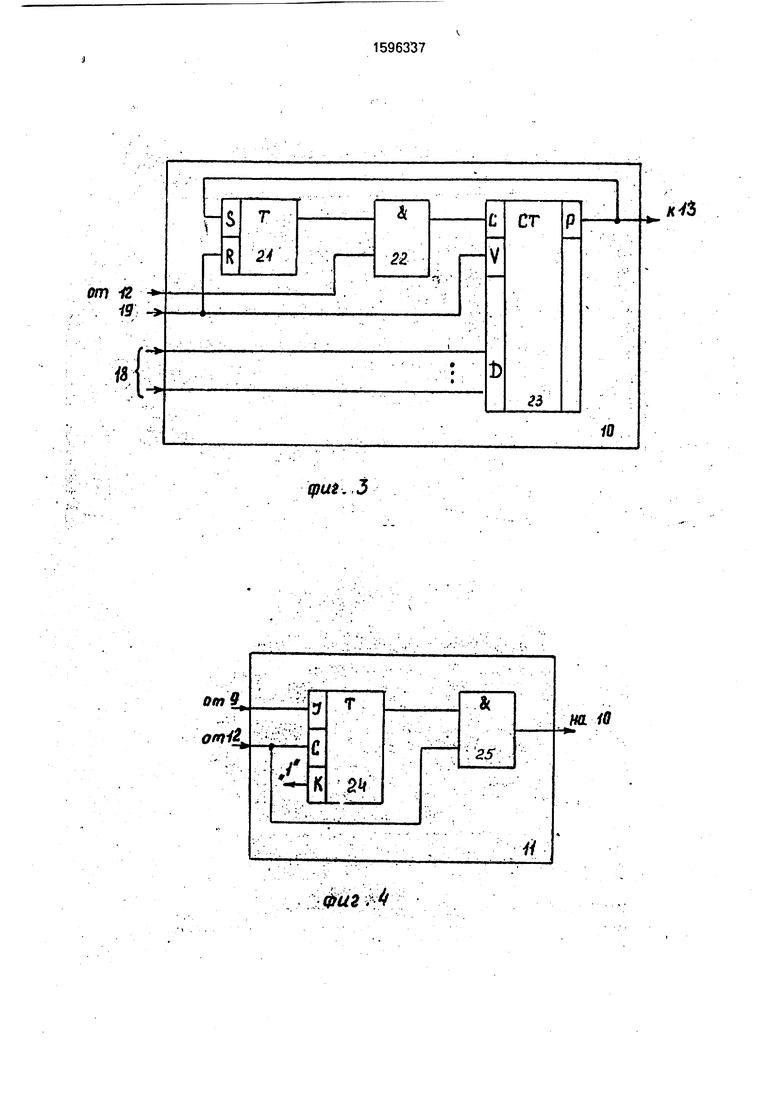

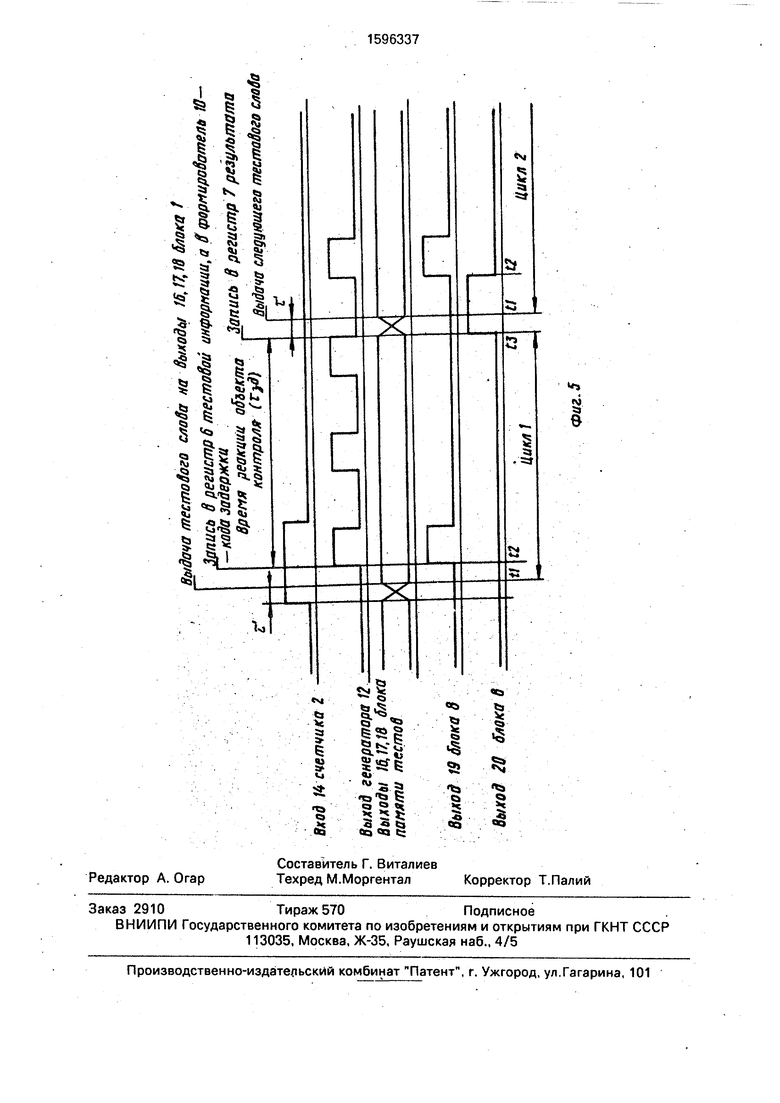

В таблице приведен пример, иллюстрирующий работу устройства в режиме проверки логического элемента 2И-ИЕ, а на

0 фиг. 5 - временные диаграммы, поясняющие принцип работы устройства.

Таблица истинности работы злемента 2И-НЕ имеет вид XI О 11 О

5 Х2 00 1 1 Y 1 1 О 1

Предположим, что входы Х1 и Х2 подключены, соответственно к контактам 1 и 2 (первый и второй ключи устройства), а выход Y - к контакту 3 (третий ключ устройства).

Контакт 4 и последующие не используются. Под циклом будем понимать одну элементарную проверку (один импульс на счетном входе счетчика 2 в цикле контроля).

Полную проверку элемента 2И-НЕ на функционирование можно провести за четыре цикла.

При поступлении сигнала Пуск через

время т (время задержки на счетчике 2 и время выборки из блока 1 памяти) на выходах 16-18 блока 1 памяти появляется тестовое (фиг. 5, момент времени t1). При этом код маски на выходе 16 блока 1 открывает все ключи, кроме третьего (строка 3 таблицы). При поступлении тактового импульса с генератора 12 блок 8 формирует импульс записи в регистр 6 и первый набор тестовой информации поступает через открытые ключи 3 на объект контроля, а эталон ожидаемого отклика поступает на соответствующий разряд первого входа блока 4 сравнения. В то же время в таймер 10 записывается код задержки, который в данном примере постоянен (строки 9-11 таблицы). Переход из одного состояния в другое должен происходить не более чем через время, равное Гзд (время задержки на логическом элементе). Время Гзд задается кодом на выходе 18 блока 1 памяти. В циклах 1 и 2 (см. таблицу) выход логического элемента не переключается, проверка на допустимое время переключения осуществляется в циклах 3 и 4. В, цикле 3 на входы логического элемента подаются две единицы (следовательно, выхбд элемента через время Тзд , заданное кодом на выходе 18 блока 1, должен переключиться в О). .В таблице (строка 19) для исправного элемента показано, что в момент выдачи воздействия на объект кон7роля (t2) выход его не переключился, а через время Тзд (t3) уже переключился. Происходит сравнение отклика (строка 19) с ожидаемым результатом (строка 7), следовательно, в регистр 7 результата записывается ноль. Для неисправного объекта контроля (строки 23-25), у которого время переключения превышает Тзд, такого сравнения не происходит, и в регистр 7 результата записывается единица в том разряде, где сравнения не произошло. В строках 20-22 таблицы показано содержимое регистра 7 результата при проверке исправного элемента, а в строках 26-28 при проверке неисправного элемента.

Формула и-з обретения

Устройство для тестового контроля временных соотношений, содержащее блок памяти тестов, счетчик адреса, группу из п ключей, блок сравнения, блок индикации, элемент ИЛИ и генератор тактовых импульсов, причем установочный вход счетчика адреса и первый вход элемента ИЛИ соединены с входом начальной установки устройства, выход счетчика адреса подключен к адресному входу блока памяти тестов,

1-й разряд первого информационного выхода которого (1 i п) соединен с управляющим входом i-ro ключа группы, выход которого и 1-й разряд первого входа блока сравнения образуют i-й вход-выход устройства для подключения к 1-му входу-выходу объекта контроля, отличающееся тем, что, с целью повышения достоверности контроля, оно содержит регистр выдачи тестов, регистр результата, блок синхронизации,

таймер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к синхровходу регистра результата и счетному входу счетчика адреса, синхровход и i-й разряд информационного входа регистра выдачи тестов

соединены соответственно с выходом блока синхронизации и 1-м разрядом второго информационного выхода блока памяти тестов, 1-й разряд выхода регистра выдачи тестов подключен к информационному входу i-ro ключа группы и i-му разряду второго входа блока сравнения, информационный вход и выход регистра результата соединены соответственно с выходом блока сравне: ния и входом блока индикации, выход

генератора тактовых импульсов подключен к синхровходам блока синхронизации и таймера, второй вход и выход элемента ИЛИ соединены соответственно с выходом таймера и входом пуска блока синхронизации,

выход которого подключен к входу управления записью таймера, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом таймера, а второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вход начальной

установки таймера подключены к третьему информационному выходу блока памяти тестов.

Фаг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Генератор тестов | 1989 |

|

SU1718221A1 |

| Устройство для отображения информации | 1986 |

|

SU1319072A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU717668A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики цифровых схем. Целью изобретения является повышение достоверности контроля. С этой целью в устройство, содержащее блок памяти тестов, счетчик адреса, группу из N ключей, блок сравнения, блок индикации, элемент ИЛИ и генератор тактовых импульсов, введены регистр выдачи тестов, регистр результата, блок синхронизации, таймер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. 5 ил.

15

11

/

fd

А

20

/J

/S

Фиг. 2

qjui, 3

Фи

1 I I §

о a I

tsll

IHI

ts

i|

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Устройство для тестового контроля временных соотношений | 1985 |

|

SU1260962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-30—Публикация

1987-12-22—Подача