Фиг.Г

3151256

точником 15 опорного напряя ения. Логическая cxewa, содержащая элементы И 12 и 13, ключи 5 и 6, компараторы 7 и 8 и одновибраторы 9 и 10, поз- воляет выделять минимальные и максимальные значения исследуемого сигнала и осуществлять их запись в регистры 21 и 22 памяти. Посредством КЗ- триггера 11, генератора 16. импульсов, Q ключей .17 и 18 и счетчиков 19 и 20 осуществляется измерение интервалов времени, соответствующих нарастанию, и спаду пульсового сигнала, значения У которых записьгоаются в регистры 23 и 15 24 памяти. В сумматоре 25 вычисляется период сердечных сокращений. Блоки 29, 30, 31 и 32 формирования команд, содержащие регистр памяти, блок двухвходовых элементов ИСКЛЮЧАНШЩЕ ИЛИ, задатчик кода анализируемых разрядов, блок элементов 2И и элемент ИЛИ, обеспечивают запись анализируемых параметров пульсовой волны в блок 27 памяти только в те моменты времени, когда изменение зтих параметров по сравнению с их предьщущими значениями имеет заданное значение., что уменьшает объем требуемой памяти за счет исключения записи повторяющихся значений параметров. Привязка к времени осуществляется таймером 26, 1 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Устройство для контроля остановки транспортного средства | 1988 |

|

SU1541654A1 |

| Устройство для ввода информации | 1987 |

|

SU1529231A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Цифровой вольтметр | 1979 |

|

SU845281A1 |

| Устройство для измерения перемещений | 1986 |

|

SU1357695A1 |

| Устройство для определения разрывной нагрузки волокнистых материалов | 1987 |

|

SU1538121A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

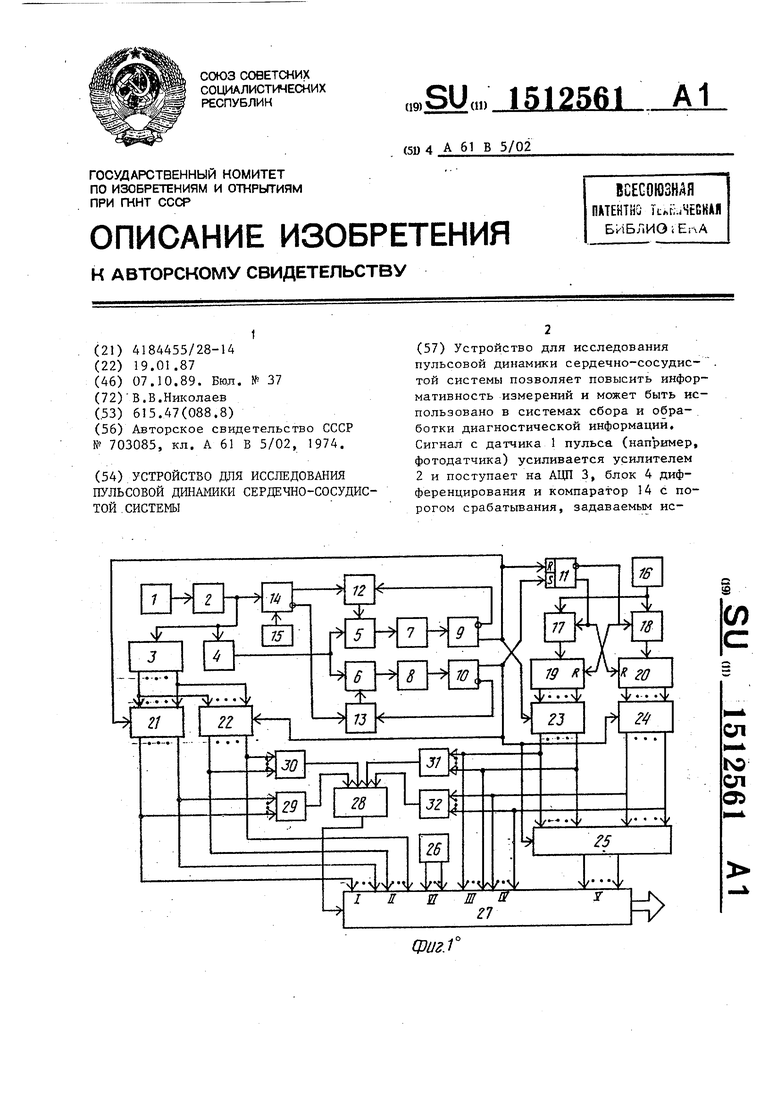

Устройство для исследования пульсовой динамики сердечно-сосудистой системы позволяет повысить информативность измерений и может быть использовано в системах сбора и обработки диагностической информации. Сигнал с датчика 1 пульса (например, фотодатчика) усиливается усилителем 2 и поступает на АЦП 3, блок 4 дифференцирования и компаратор 14 с порогом срабатывания, задаваемым источником 15 опорного напряжения. Логическая схема, содержащая элементы И 12 и 13, ключи 5 и 6, компараторы 7 и 8 и одновибраторы 9 и 10, позволяет выделять минимальные и максимальные значения исследуемого сигнала и осуществлять их запись в регистры 21 и 22 памяти. Посредством RS -триггера 11, генера 16 импульсов, ключей 17 и 18 и счетчиков 19 и 20 осуществляется измерение интервалов времени, соответствующих нарастанию и спаду пульсового сигнала, значения которых записываются в регистры 23 и 24 памяти. В сумматоре 25 вычисляется период сердечных сокращений. Блоки 29,30,31 и 32 формирования команд, содержащие регистр памяти, блок двухвходовых элементов Исключающее ИЛИ, задатчик кода анализируемых разрядов, блок элементов 2И и элемент ИЛИ, обеспечивают запись анализируемых параметров пульсовой волны в блок 27 памяти только в те моменты времени, когда изменение этих параметров по сравнению с их предыдущими значениями имеет заданное значение, что уменьшает объем требуемой памяти за счет исключения записи повторяющихся значений параметров. Привязка ко времени осуществляется таймером 26. 1 з.п. ф-лы, 3 ил.

Изобретение относится к медицине медицинской технике и может быть спользовано в системах сбора и обаботки диагностической информации 25 ри исследовании пульсовой динамики ердечно-сосудистой системы.

Цель изобретения - повышение инормативности измерений.

30

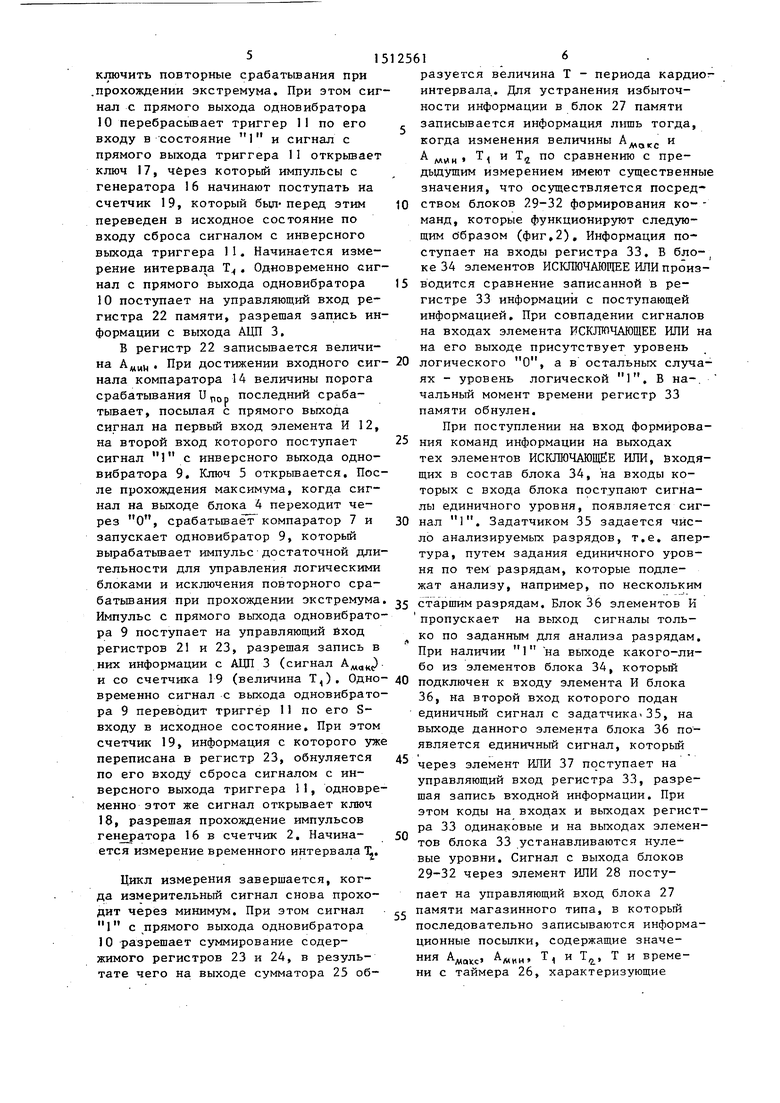

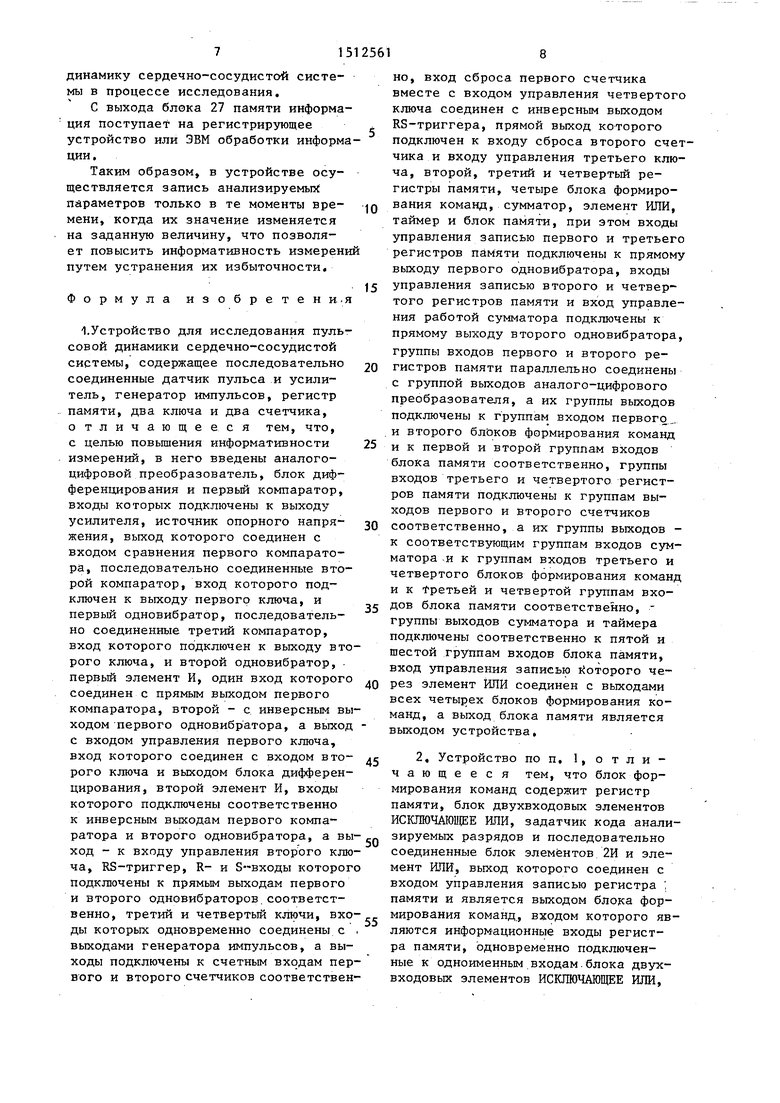

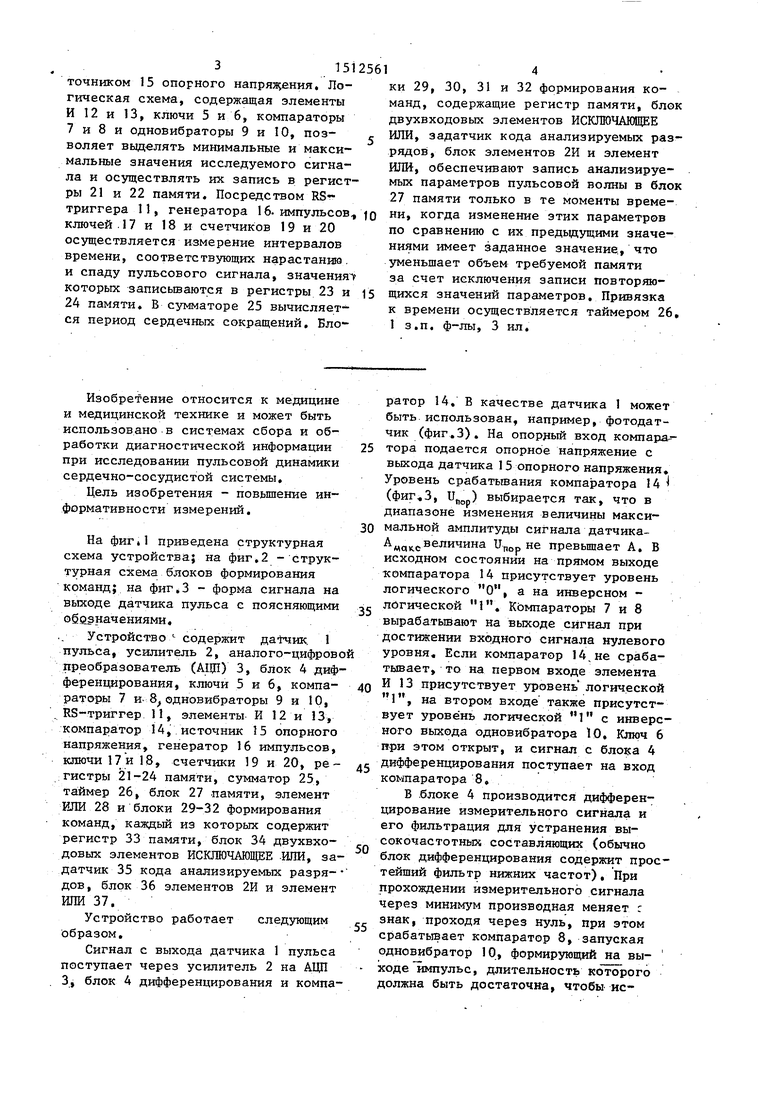

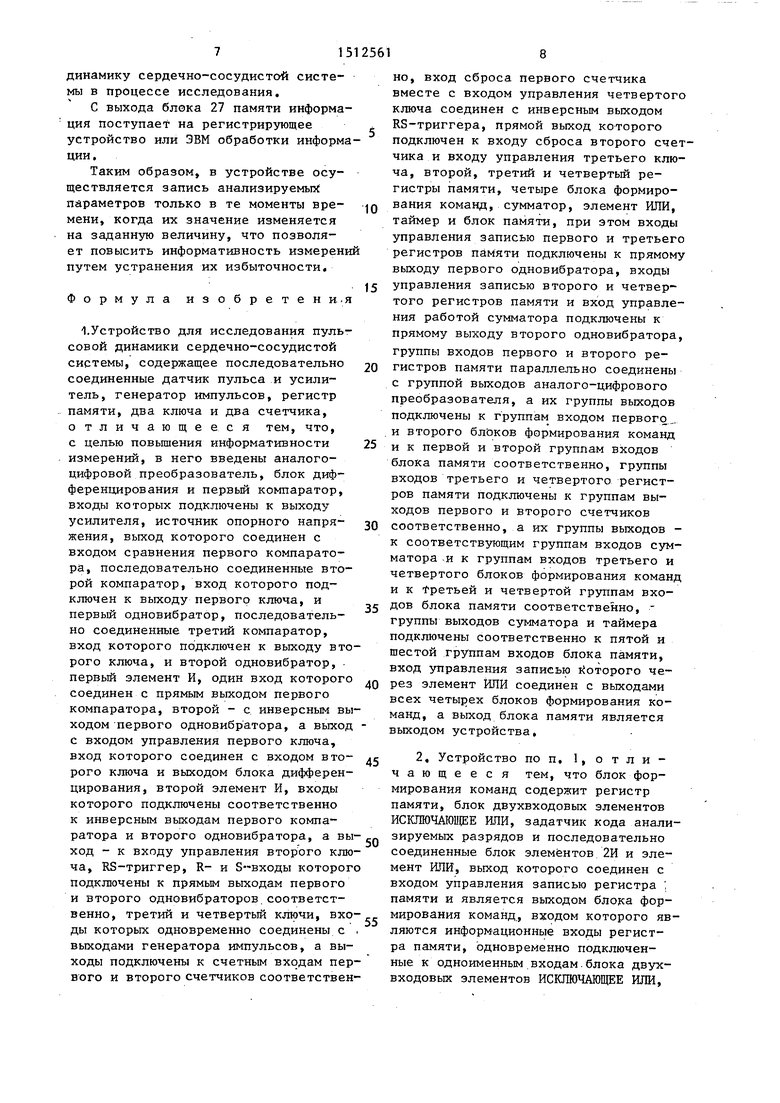

На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блоков формирования комавд; на - форма сигнала на выходе датчика пульса с поясняющими 5 обй начениями,

. Устройство содержит , 1 пульса, усилитель 2, аналого-цифровой преобразователь (А1Щ) 3, блок 4 дифференцирования, ключи 5 и 6, компа- 40 раторы 7 и-8 одновибраторы 9 и 10

RS-триггер 11, элементы И 12 и 13, компаратор 14, источник 15 опорного напряжения, генератор 16 импульсов, ключи 17 и 18, счетчики 19 и 20, ре- дд гистры 21-24 памяти, сумматор 25, таймер 26, блок 27 .памяти, элемент ИЛИ 28 и блоки 29-32 формирования команд, каждый из которых содержит регистр 33 памяти, блок 34 двухвхо- . довых элементов ИСКЛЮЧАЮЩЕЕ .ИЛИ, задатчик 35 кода анализируемых разря-- дов, блок 36 элементов 2И и элемент ИЛИ 37.

Устройство работает следующим сг образом.

Сигнал с выхода датчика 1 пульса поступает через усилитель 2 на АЦП 3, блок 4 дифференцирования и компаратор 14. В качестве датчика 1 может быть использован, например, фотодатчик (фиг.З). На опорный вход компара-- тора подается опорное напряжение с выхода датчика 15 опорного напряжения. Уровень срабатывания компаратора 14 (фиг,3, ) выбирается так, что в диапазоне изменения величины максимальной амплитуды сигнала датчика- А,д.величина и„ор не превышает А. В исходном состоянии на прямом выходе -компаратора 14 присутствует уровень логического О, а на инверсном - логической 1. Компараторы 7 и 8 вырабатьшают на выходе сигнал при достижении входного сигнала нулевого уровня. Если компаратор 14,не срабатывает, то на первом входе элемента И 13 присутствует уровень логической 1, на втором входе также присутствует уровень логической 1 с инверсного выхода одновибратора 10. Ключ 6 при этом открыт, и сигнал с блока 4 дифференцирования поступает на вход компаратора 8,

В .блоке 4 производится дифференцирование измерительного сигнала и его фильтрация для устранения высокочастотных составляющих (обычно блок дифференцирования содержит простейший фильтр нижних частот). При прохождении измерительного сигнала через минимум производная меняет : знак, проходя через нуль, при этом срабатывает компаратор 8, запуская одновибратор 10, формирующий на вы- ходе импульс, длительность которого должна быть достаточна, чтобы исключить повторные срабатьшания при .прохождении экстремума. При этом сигнал с прямого выхода одновибратора 10 перебрасывает триггер 11 по его входу в состояние 1 и сигнал с прямого выхода триггера 11 открьшает ключ 17, через который импульсы с генератора 16 начинают поступать на счетчик 19, который был-перед этим переведен в исходное состояние по входу сброса сигналом с инверсного выхода триггера 11. Начинается измерение интервала Т. Одновременно сигнал с прямого выхода одновибратора 10 поступает на управляющий вход регистра 22 памяти, разрешая запись информации с выхода АЦП 3,

В регистр 22 записьшается величина А

MllV4

При достижении входного сиг- 20

14 величины порога последний срабанала компаратора срабатывания тывает, посылая с прямого выхода сигнал на первый вход элемента И 12, на второй вход которого поступает сигнал 1 с инверсного выхода одно- вибратора 9. Ключ 5 открывается. После прохождения максимума, когда сигнал на выходе блока 4 переходит через О, срабатывает компаратор 7 и запускает одновибратор 9, который вырабатьшает импульс достаточной длительности для управления логическими блоками и исключения повторного срабатьшания при прохождении экстремума, Импульс с прямого выхода одновибратора 9 поступает на управляющий бход регистров 21 и 23, разрешая запись в них информации с АЦП 3 (сигнал А.м,к.

дьщущим измерением имеют существен значения, что осуществляется посре ством блоков 29-32 формирования ко манд, которые функционируют следую щим ббразом (фиг,2), Информация по ступает на входы регистра 33, Б бл ке 34 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ про водится сравнение записанной в регистре 33 информации с поступающей информацией. При совпадении сигнал на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ на его выходе присутствует уровень логического О, а в остальных слу ях - уровень логической 1, В на чальный момент времени регистр 33 памяти обнулен.

При поступлении на вход формиро ния команд информации на выходах тех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, Вхо щих в состав блока 34, на входы ко торых с входа блока поступают сигн лы единичного уровня, появляется с нал 1, Задатчиком 35 задается чи ло анализируемых разрядов, т,е, ап тура, путем задания единичного уро ня по тем разрядам, которые подлежат анализу, например, по нескольк 35 старшим разрядам. Блок 36 элементов пропускает на выход сигналы толь ко по заданным для анализа разряда При наличии 1 на выходе какого-л бо из элементов блока 34, который

25

30

и со счетчика 19 (величина Т,), Одно- 40 подключен к входу элемента И блока временно сигнал с выхода одновибрато- зб, на второй вход которого подан ра

9 переводит триггер 11 по его S- входу в исходное состояние. При этом счетчик 19, информация с которого уже переписана в регистр 23, обнуляется по его входу сброса сигналом с инверсного выхода триггера 11, одновременно этот же сигнал открывает ключ 18, разрешая прохождение импульсов генератора 16 в счетчик 2, Начинается измерение временного интервала 1,

Цикл измерения завершается, когда измерительный сигнал снова проходит через минимум. При этом сигнал 1 с прямого выхода одновибратора 10 разрешает суммирование содержимого регистров 23 и 24, в результате чего на выходе сумматора 25 об-

единичный сигнал с задатчика-35, на выходе данного элемента блока 36 по является единичный сигнал, который

через элемент ИЛИ 37 поступает на управляющий вход регистра 33, разре шая запись входной информации. При этом коды на входах и выходах регис ра 33 одинаковые и на выходах элеме тов блока 33 устанавливаются нулевые уровни. Сигнал с выхода блоков 29-32 через элемент ШИ 28 поступает на управляющий вход блока 27 памяти магазинного типа, в который последовательно записываются информ ционные посылки, содержащие значе50

55

ния А

макс мин

т, и Т„, Т и времени с таймера 26, характеризующие

разуется величина Т - периода кардио- интервала.. Для устранения избыточности информации в блок 27 памяти записывается информация Л1га1ь тогда, когда изменения

величины А ..„,., и

лп(д к с

МКН

Т И Tj ПО сравнению с пре

дьщущим измерением имеют существенные значения, что осуществляется посредством блоков 29-32 формирования ко - манд, которые функционируют следующим ббразом (фиг,2), Информация поступает на входы регистра 33, Б бло- ке 34 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ произ- водится сравнение записанной в регистре 33 информации с поступающей информацией. При совпадении сигналов на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ на на его выходе присутствует уровень логического О, а в остальных случаях - уровень логической 1, В на-. чальный момент времени регистр 33 памяти обнулен.

При поступлении на вход формирования команд информации на выходах тех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, Входящих в состав блока 34, на входы которых с входа блока поступают сигналы единичного уровня, появляется сигнал 1, Задатчиком 35 задается число анализируемых разрядов, т,е, апертура, путем задания единичного уровня по тем разрядам, которые подлежат анализу, например, по нескольким старшим разрядам. Блок 36 элементов И пропускает на выход сигналы толь- ко по заданным для анализа разрядам. При наличии 1 на выходе какого-либо из элементов блока 34, который

подключен к входу элемента И блока зб, на второй вход которого подан

40 подключен к входу элемента И блока зб, на второй вход которого подан

единичный сигнал с задатчика-35, на выходе данного элемента блока 36 появляется единичный сигнал, который

через элемент ИЛИ 37 поступает на управляющий вход регистра 33, разрешая запись входной информации. При этом коды на входах и выходах регистра 33 одинаковые и на выходах элементов блока 33 устанавливаются нулевые уровни. Сигнал с выхода блоков 29-32 через элемент ШИ 28 поступает на управляющий вход блока 27 памяти магазинного типа, в который последовательно записываются информационные посылки, содержащие значе50

55

ния А

макс мин

т, и Т„, Т и времени с таймера 26, характеризующие

динамику сердечно-сосудистой системы в процессе исследования.

С выхода блока 27 памяти информация поступает на регистрирующее устройство или ЭВМ обработки информации.

Таким образом, в устройстве осуществляется запись анализируемые параметров только в те моменты вре- мени, когда юс значение изменяется на заданную величину, что позволяет повысить информативность измерений путем устранения их избыточности.

Формула изобретен и. .я

о 5 Q мс

5

но, вход сброса первого счетчика вместе с входом управления четвертого ключа соединен с инверсным выходом RS-триггера, прямой выход которого подключен к входу сброса второго счетчика и входу управления третьего ключа, второй, третий и четвертый регистры памяти, четыре блока формирования команд, сумматор, элемент ИЛИ, таймер и блок памяти, при этом входы управления записью первого и третьего регистров памяти подключены к прямому выходу первого одновибратора, входы управления записью второго и четвер того регистров памяти и вход управления работой сумматора подключены к прямому выходу второго одновибратора, группы входов первого и второго регистров памяти параллельно соединены с группой выходов аналого-цифрового преобразователя, а их группы выходов подключены к группам входом первого., и второго блЬков формирования команд и к первой и второй группам входов блока памяти соответственно, группы входов третьего и четвертого регистров памяти подключены к группам выходов первого и второго счетчиков соответственно, а их группы выходов - к соответствующим группам входов сумматора -и к группам входов третьего и четвертого блоков формирования команд и к Третьей и четвертой группам входов блока памяти соответственно, группы выходов сумматора и таймера подключены соответственно к пятой и шестой группам входов блока памяти, вход управления записью i oTOporo через элемент ИЛИ соединен с выходами всех четырех блоков формирования команд, а выход блока памяти является выходом устройства.

2, Устройство по п. 1, отличающееся тем, что блок формирования команд содержит регистр памяти, блок двухвходовых элементов ИСКЛЮЧАЮиЩЕ ИЛИ, задатчик кода анализируемых разрядов и последовательно соединенные блок элементов 2И и элемент ИЛИ, выход которого соединен с входом управления записью регистра , памяти и является выходом блока формирования команд, входом которого являются информационные входы регистра памяти, одновременно подключенные к одноименным.входам.блока двухвходовых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,

вторые одноименные входы которого -подключены к соответствующим разрядам группы выходов регистра памяти, а выходы соединены с одними одноимен1512561

, ен10

ными входами блока элементов 2И, другие одноименные входы которого подключены к выходам задатчика кода анаг лизируемых разрядов.

Фиг.г

| Устройство для исследования пульсовой динамики сердечно-сосудистой системы | 1974 |

|

SU703085A1 |

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1989-10-07—Публикация

1987-01-19—Подача